Fターム[5J500AK02]の内容

Fターム[5J500AK02]に分類される特許

1 - 20 / 1,173

コンデンサマイクロホン用インピーダンス変換器およびコンデンサマイクロホン

正帰還増幅器およびインターポレーション回路

全差動型帰還増幅回路および電気機器

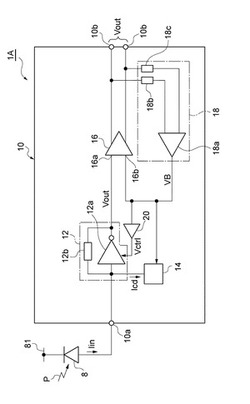

トランスインピーダンスアンプ

【課題】入力電流の大きさに応じた量の電流を入力電流から分流することによりダイナミックレンジが拡大されたトランスインピーダンスアンプ(TIA)において、入力インピーダンスの変化を低減する。

【解決手段】TIA10は、光電流Iinの大きさに応じた出力電圧Voutを生成する。TIA10は、光電流Iinを出力電圧Voutに変換する利得可変増幅回路12と、光電流Iinが大きいほど大きな電流Icdを光電流Iinから分流する分流回路14と、光電流Iinが大きいほど利得可変増幅回路12の利得を小さくする利得調整回路20とを備える。

(もっと読む)

パルス幅変調回路およびスイッチングアンプ

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

オペアンプ補償回路

【課題】出力バッファを有するオペアンプA1であつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路を提供する。

【解決手段】バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタT1を有し、あるいは、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続し、それぞれ入力信号と反転された入力信号が入力されている構成を有し、オフセット電位が接地となることを特徴とする。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

電力増幅器における動的バイアス制御

【課題】平均電力効率(APE)が改良されることができるセルラ電話における電力増幅器を提供する。

【解決手段】RF出力電力増幅器(PA)は、第1および第2のAB級増幅回路を含んでいる。高電力オペレーティングモードにおいて動作する場合、第1の増幅器はPA出力端子を駆動する。第1の増幅器のパワートランジスタ(単数または複数)は、高い出力電力での効率性および線形性を最適化するように、バイアスをかけられる。低電力オペレーティングモードにおいて動作する場合、第2の増幅器は出力端子を駆動する。第2の増幅器のパワートランジスタは、低い出力電力での効率性および線形性を最適化するように、バイアスをかけられる。増幅器のパワートランジスタを適切にサイジングすることによって、エミッタ電流密度は、実質的に等しく維持されるので、PA電力利得は、2つのオペレーティングモードにおいて同じである。

(もっと読む)

同相電圧帰還回路及び全差動演算増幅器

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

基準電圧発生回路

【課題】小規模の付加回路により、基準電圧の温度特性を簡易な調整によって十分に改善することができる基準電圧発生回路を提供する

【解決手段】バイポーラトランジスタ106、バイポーラトランジスタ106と並列に接続されるバイポーラトランジスタ107、バイポーラトランジスタ107のエミッタに一端が接続される抵抗素子104、バイポーラトランジスタ106のベース電位と、バイポーラトランジスタ107のベース電位との差分によって生じる差電圧を発生させる抵抗素子109、バイポーラトランジスタ106のエミッタ電位と抵抗素子104の他端の電位とが等しくなるように動作する演算増幅器105によって基準電圧発生回路を構成し、抵抗素子109が生成する差電圧が、温度によって変化する。

(もっと読む)

センサ信号処理装置

【課題】簡単な構成で入力オフセット電圧の温度依存性が小さいセンサ信号処理装置を提供する。

【解決手段】センサ用電源として第1の電源電圧V´ccを供給されて動作し、センサ出力Vs1、Vs2を出力するセンサ部100と、信号処理用電源として第2の電源電圧Vccを供給されて動作し、センサ出力Vs1、Vs2が入力される差動対を使用する差動増幅部を有して信号処理を行なう信号処理部200と、を有してセンサ信号処理装置1を構成する。この第1の電源電圧V´ccは、信号処理部200の差動増幅部250の入力電圧範囲の下限領域に設定される。

(もっと読む)

差動増幅回路

【課題】正常動作する入力信号電圧範囲を広げることが可能な差動増幅回路を提供する。

【解決手段】差動信号が入力され、該差動信号を構成する2つの信号の電圧の差を増幅して出力する差動増幅回路であって、差動信号を構成する2つの信号の平均電圧を検出する平均電圧検出回路2と、差動信号を構成する2つの信号のそれぞれに対応するように設けられ、差動信号を構成する一の信号を、平均電圧検出回路2で検出した平均電圧と等しい電圧降圧して出力する2つの電圧シフト回路3,4と、2つの電圧シフト回路3,4のそれぞれから出力される2つの信号の電圧の差を増幅して出力する差動増幅回路本体5と、を備えたものである。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

抵抗の調整機能を有する演算回路

【課題】MOSスイッチによる抵抗の調整機能を有する演算回路において、面積の増加を最小限に留め、かつ、非常に簡易な方法でMOSスイッチの寄生容量の影響を抑える演算回路を提供する。

【解決手段】MOSスイッチ21−23のゲートやバックゲートに、調整対象の抵抗11−13よりも数倍以上大きな抵抗31−33、61を設けることにより、寄生容量でできる極とほぼ同じ周波数にゼロが発生し、寄生容量の影響を抑えることができる。この抵抗には、絶対値バラつきや温度特性、相対バラつきやノイズ等の特性は要求されないため、用いるプロセスで最もシート抵抗の高い抵抗を細い幅で作成すればよく、面積の増加量は少ない。また、抵抗は容量よりも微細化が容易であるため、今後更にプロセスの微細化が進んでも本発明を変わらず使用できる。

(もっと読む)

増幅装置

【課題】 入力電圧が低く、特性を向上させた増幅装置を提供する。

【解決手段】 増幅装置は、一対の受光素子からそれぞれ入力された第1及び第2の電流信号In(+),In(−)を、第1及び第2の電圧信号Vo(−),Vo(+)にそれぞれ変換して出力する第1及び第2のトランスインピーダンスアンプ20と、第1及び第2の電流信号In(+),In(−)の各電流を分流する分流回路24と、第1及び第2の電圧信号Vo(−),Vo(+)の平均電圧値を示す平均信号を生成して出力する平均値検出回路と、平均信号Vav、及び第1及び第2の電圧信号Vo(−),Vo(+)のオフセット電圧値に基づいて、分流回路24に分流される第1及び第2の電流信号In(+),In(−)の各電流値を制御する制御回路23とを含む。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

RFパワーモジュール

【課題】多段増幅段を含むRF電力増幅回路の低パワーおよび中間パワー時における電力付加効率(PAE)の低下を軽減する。

【解決手段】RF電力増幅回路313は、前段増幅器310、後段増幅器311、制御部312を具備する。前段増幅器310はRF送信入力信号Pinに応答して、前段増幅器310の出力の増幅信号に後段増幅器311が応答する。制御部312は、出力電力制御電圧Vapcに応答して、前段増幅器310と前記後段増幅器311のアイドリング電流を制御して前段増幅器310と前記後段増幅器311の利得を制御する。出力電力制御電圧Vapcに応答して、前段増幅器310のアイドリング電流と利得とは第1の連続関数2ndAmpに従って連続的に変化して、後段増幅器311のアイドリング電流と利得とは第2の連続関数3rdAmpに従って連続的に変化する。第2の連続関数3rdAmpは、第1の連続関数2ndAmpよりも1次以上高次の関数である。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

1 - 20 / 1,173

[ Back to top ]