Fターム[5J500AK05]の内容

Fターム[5J500AK05]に分類される特許

1 - 20 / 1,226

正帰還増幅器およびインターポレーション回路

D級増幅器

正帰還増幅器およびインターポレーション回路

制御回路および位相変調器

パルス幅変調回路およびスイッチングアンプ

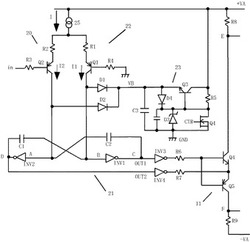

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

(もっと読む)

トランスインピーダンスアンプ

【課題】入力電流の大きさに応じた量の電流を入力電流から分流することによりダイナミックレンジが拡大されたトランスインピーダンスアンプ(TIA)において、入力インピーダンスの変化を低減する。

【解決手段】TIA10は、光電流Iinの大きさに応じた出力電圧Voutを生成する。TIA10は、光電流Iinを出力電圧Voutに変換する利得可変増幅回路12と、光電流Iinが大きいほど大きな電流Icdを光電流Iinから分流する分流回路14と、光電流Iinが大きいほど利得可変増幅回路12の利得を小さくする利得調整回路20とを備える。

(もっと読む)

駆動回路、及び、光送信装置

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

ダブルソースフォロア回路

【課題】電流源によって流れる電流量を増大させることなく、出力信号の立ち上り、立ち下りを高速化することができるダブルソースフォロア回路を提供する。

【解決手段】nMOSFET102を含むソースフォロア回路と、nMOSFET102とは極性が異なるpMOSFET101を含むソースフォロア回路と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路に入力信号を入力する入力端子111と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路から出力信号を出力する共通の出力端子112)と、を含むダブルソースフォロア回路を構成する。

(もっと読む)

光受信回路用信号増幅器

【課題】受信した光信号を電流信号に変換する受光素子に接続される信号増幅器において、メインアンプの入力段の入力インピーダンスが無視できないときに設けられるレベル調整抵抗の影響を少なくし、広帯域の周波数特性と高い光受信感度特性とを得る。

【解決手段】信号増幅器は、電流信号を電圧に変換して出力するプリアンプと、少なくとも入力段が差動回路からなりプリアンプから出力された電圧信号を増幅するメインアンプと、プリアンプとメインアンプとの間に設けられ電圧信号が供給される2個以上のフォロワ回路と、プリアンプの出力とメインアンプの各入力との間の経路において各フォロワ回路ごとに設けられる抵抗値が等しい抵抗と、抵抗のうちの1つに対して一端が接続し、他端が接地されたコンデンサと、を備えている。コンデンサとそのコンデンサに接続する抵抗とによって、電圧信号の平均電位を検出するローパスフィルタが構成されている。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】オフセット補償機能付き駆動回路190は、入力電位に応じたレベルの出力電位を出力するプッシュ型駆動回路160と、駆動回路160のオフセット電圧VOFを補償するオフセット補償回路とを備える。オフセット補償回路は、キャパシタ122およびスイッチS1〜S4を含む。スイッチS1,S2をオンしてキャパシタ122をオフセット電圧VOFに充電し、次にスイッチS3をオンしてVI+VOFを駆動回路160に与え、次いでスイッチS4をオンしてVO=VIとする。したがって、消費電流を低減し、オフセット電圧VOFを補償できる。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

差動増幅回路

【課題】正常動作する入力信号電圧範囲を広げることが可能な差動増幅回路を提供する。

【解決手段】差動信号が入力され、該差動信号を構成する2つの信号の電圧の差を増幅して出力する差動増幅回路であって、差動信号を構成する2つの信号の平均電圧を検出する平均電圧検出回路2と、平均電圧検出回路2で検出した平均電圧を基準として正負の電源電圧を生成する電源電圧発生回路3と、電源電圧発生回路3で生成した正負の電源電圧を正電源、負電源として用い、差動信号を構成する2つの信号の電圧の差を増幅して出力する差動増幅回路本体4と、を備えたものである。

(もっと読む)

ソースフォロア回路

【課題】消費電力の増加を抑制しつつ、負荷回路からのキックバックを抑制する。

【解決手段】MOSトランジスタM11と、ゲートおよびドレイン間がダイオード接続されたMOSトランジスタM12と、電流源C11とを直列接続してソースフォロア回路10を構成する。MOSトランジスタM11のゲートに入力された、ソースフォロア回路10への入力信号Vinは、MOSトランジスタM11によりほぼ1倍の利得で出力され、さらに、ダイオード接続されたMOSトランジスタM12でほぼ1倍の利得で出力され、これがソースフォロア回路10の出力信号Voutとして出力されるため、結果的に、1段構成のソースフォロア回路と同様の動作をするが、その消費電力は少なくてすむ。

(もっと読む)

トランスインピーダンスアンプ

【課題】広帯域かつ平坦性の高い利得周波数特性を有するトランスインピーダンスアンプを提供する。

【解決手段】トランスインピーダンスアンプは、コア回路6と、コア回路6の出力信号振幅を検出する出力信号モニタ回路7と、振幅検出値に基づいてコア回路6の利得および周波数ピーキング量を制御する制御回路8を備える。制御回路8は、出力信号モニタ回路7の第一の帯域通過フィルタの通過帯域におけるコア回路6の出力信号振幅が所望の値になるように、出力信号モニタ回路7の第一の振幅検出回路が検出した検出値に基づいて帰還抵抗RFの値を変化させ、出力信号モニタ回路7の第二の帯域通過フィルタの通過帯域におけるコア回路6の出力信号振幅が所望の値になるように、出力信号モニタ回路7の第二の振幅検出回路が検出した検出値に基づいて周波数ピーキング量を変化させる。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

ソースフォロア回路

【課題】複数段構成におけるソースフォロア回路において入出力レンジを確保する。

【解決手段】ソースフォロア部SF11、SF12間に、ゲートドレイン間がダイオード接続され且つソースフォロア部SF11およびSF12を構成するMOSトランジスタM11およびM12と同一チャネル種類のMOSトランジスタM13とそのドレインに接続された電流源C13とからなる接続部11を設け、前段のソースフォロア部SF11の出力端とMOSトランジスタM13のソースとを接続し、MOSトランジスタM13のドレインと後段のソースフォロア部SF12の入力端とを接続する。接続部11における入出力間の電圧レベルのシフト方向は、ソースフォロア部SF11、SF12における入出力間の電圧レベルのシフト方向と逆となり、電圧シフトを打ち消す方向に作用するため、電圧レベルのシフトにより入出力レンジが狭くなることを抑制することが可能となる。

(もっと読む)

演算増幅器

【課題】消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転を防止する。

【解決手段】入力部10の反転入力端子100と第2のトランジスタ2のコレクタとが第1のダ入力部用イオード11を介して、非反転入力端子200と第1のトランジスタ1のコレクタとが第2の入力部用ダイオード12を介して、それぞれ接続される一方、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と反転入力端子100とが第5のダイオード15を介して、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と非反転入力端子200とが第6のダイオード16を介して、それぞれ接続されて、消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転が防止されるようになっている。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高線形性と低歪みの増幅器を提供する。

【解決手段】修正された微分重ね合わせ低ノイズ増幅器は、メイン電流経路とキャンセル電流経路を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタが、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第2の新規な側面では、LNA負荷を通過しないデブースト電流経路が設けられる。デブースト電流は、ヘッドルームの問題を生じさせることなく、ネガティブ・フィードバックを増加させる。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

1 - 20 / 1,226

[ Back to top ]