Fターム[5J500AK09]の内容

Fターム[5J500AK09]の下位に属するFターム

多段ミラー回路 (24)

Fターム[5J500AK09]に分類される特許

1 - 20 / 1,016

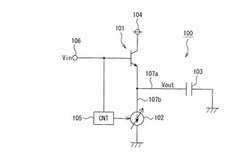

トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

(もっと読む)

同相電圧帰還回路及び全差動演算増幅器

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

電力増幅器における動的バイアス制御

【課題】平均電力効率(APE)が改良されることができるセルラ電話における電力増幅器を提供する。

【解決手段】RF出力電力増幅器(PA)は、第1および第2のAB級増幅回路を含んでいる。高電力オペレーティングモードにおいて動作する場合、第1の増幅器はPA出力端子を駆動する。第1の増幅器のパワートランジスタ(単数または複数)は、高い出力電力での効率性および線形性を最適化するように、バイアスをかけられる。低電力オペレーティングモードにおいて動作する場合、第2の増幅器は出力端子を駆動する。第2の増幅器のパワートランジスタは、低い出力電力での効率性および線形性を最適化するように、バイアスをかけられる。増幅器のパワートランジスタを適切にサイジングすることによって、エミッタ電流密度は、実質的に等しく維持されるので、PA電力利得は、2つのオペレーティングモードにおいて同じである。

(もっと読む)

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の利得の温度依存性を抑制し、温度補償回路を有するバイアス回路を備えた電力増幅回路を提供する。

【解決手段】ドレインが高電位に接続され、ソースが接地された増幅用トランジスタを備え、ソースが接地され増幅用トランジスタGTrのゲートにゲートが接続されたカレントミラートランジスタCMTrによって増幅用トランジスタのバイアス電流を制御する電力増幅回路であって、アノードが制御電源端子に接続された第1のダイオードD1と、アノードが第1のダイオードD1のカソードに結合され、カソードがカレントミラートランジスタCMTrのドレインに接続された第2のダイオードD2と、一方の端子が第2のダイオードD2のカソードに接続され他方の端子が接地された第1の抵抗素子R1と、第2のダイオードD2と並列接続された第2の抵抗素子R2とを備える。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

基準電圧発生回路

【課題】小規模の付加回路により、基準電圧の温度特性を簡易な調整によって十分に改善することができる基準電圧発生回路を提供する

【解決手段】バイポーラトランジスタ106、バイポーラトランジスタ106と並列に接続されるバイポーラトランジスタ107、バイポーラトランジスタ107のエミッタに一端が接続される抵抗素子104、バイポーラトランジスタ106のベース電位と、バイポーラトランジスタ107のベース電位との差分によって生じる差電圧を発生させる抵抗素子109、バイポーラトランジスタ106のエミッタ電位と抵抗素子104の他端の電位とが等しくなるように動作する演算増幅器105によって基準電圧発生回路を構成し、抵抗素子109が生成する差電圧が、温度によって変化する。

(もっと読む)

バイアス回路およびそれを有するアンプ回路

【課題】増幅トランジスタのトランスコンダクタンスgmの変動を抑制する。

【解決手段】バイアス回路は,第1のドレイン電流を生成する第1のトランジスタと,第2のドレイン電流を生成する第2のトランジスタと,直列に接続された複数の抵抗素子を有し,複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有する。そして,抵抗回路の第1のノードの第1の電圧が第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が第2のトランジスタのゲートに印加され,第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力される。

(もっと読む)

センサ信号処理装置

【課題】簡単な構成で入力オフセット電圧の温度依存性が小さいセンサ信号処理装置を提供する。

【解決手段】センサ用電源として第1の電源電圧V´ccを供給されて動作し、センサ出力Vs1、Vs2を出力するセンサ部100と、信号処理用電源として第2の電源電圧Vccを供給されて動作し、センサ出力Vs1、Vs2が入力される差動対を使用する差動増幅部を有して信号処理を行なう信号処理部200と、を有してセンサ信号処理装置1を構成する。この第1の電源電圧V´ccは、信号処理部200の差動増幅部250の入力電圧範囲の下限領域に設定される。

(もっと読む)

演算増幅器

【課題】消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転を防止する。

【解決手段】入力部10の反転入力端子100と第2のトランジスタ2のコレクタとが第1のダ入力部用イオード11を介して、非反転入力端子200と第1のトランジスタ1のコレクタとが第2の入力部用ダイオード12を介して、それぞれ接続される一方、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と反転入力端子100とが第5のダイオード15を介して、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と非反転入力端子200とが第6のダイオード16を介して、それぞれ接続されて、消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転が防止されるようになっている。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

RFパワーモジュール

【課題】多段増幅段を含むRF電力増幅回路の低パワーおよび中間パワー時における電力付加効率(PAE)の低下を軽減する。

【解決手段】RF電力増幅回路313は、前段増幅器310、後段増幅器311、制御部312を具備する。前段増幅器310はRF送信入力信号Pinに応答して、前段増幅器310の出力の増幅信号に後段増幅器311が応答する。制御部312は、出力電力制御電圧Vapcに応答して、前段増幅器310と前記後段増幅器311のアイドリング電流を制御して前段増幅器310と前記後段増幅器311の利得を制御する。出力電力制御電圧Vapcに応答して、前段増幅器310のアイドリング電流と利得とは第1の連続関数2ndAmpに従って連続的に変化して、後段増幅器311のアイドリング電流と利得とは第2の連続関数3rdAmpに従って連続的に変化する。第2の連続関数3rdAmpは、第1の連続関数2ndAmpよりも1次以上高次の関数である。

(もっと読む)

受光回路

【課題】受光回路の消費電流を削減する。

【解決手段】一つの実施形態によれば、受光回路は、トランスインピーダンスアンプと出力回路が設けられる。トランスインピーダンスアンプは、フォトダイオード、帰還抵抗、及び第1のトランジスタが設けられる。フォトダイオードは、光信号を電気信号に変換する。帰還抵抗は、フォトダイオードと内部出力端子の間に設けられる。第1のトランジスタは、ゲートにフォトダイオードで光電変換された電気信号が入力され、ドレインが内部出力端子に接続される。出力回路は、第1のトランジスタと同一チャネル型であり、ゲートが内部出力端子に接続され、電流源負荷が接続されるとともにドレイン側から出力信号を出力する第2のトランジスタを含む。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

トランスインピーダンスアンプおよび受光回路

【課題】出力電圧範囲を広げることが容易なトランスインピーダンスアンプおよび受光回路を提供する。

【解決手段】第1のMOSトランジスタと、カレントミラー回路と、第2のMOSトランジスタと、負荷と、第1帰還抵抗と、を有する。前記第1のMOSトランジスタは、フォトダイオードが接続されるゲート端子を有する。前記カレントミラー回路には、前記第1のMOSトランジスタからの出力電流が入力される。前記第2のMOSトランジスタは、前記カレントミラー回路の出力端子の電圧が入力されるゲート端子を有し、ソース接地とされ、前記第1のMOSトランジスタの極性と同じ極性を有する。前記負荷は、前記カレントミラー回路の前記出力端子に接続される。第1帰還抵抗は、前記第1のMOSトランジスタの前記ゲート端子と、前記第2のMOSトランジスタのドレイン端子と、の間に接続される。前記第2のMOSトランジスタは、前記ゲート端子電圧に対応した電圧を前記ドレイン端子から出力することを特徴とする。

(もっと読む)

RF電力増幅器およびその動作方法

【課題】ランプアップまたはランプダウンにおいてスイッチングスペクトラムの劣化を軽減すること。

【解決手段】初段と最終段のバイアス回路81、83が、初段と最終段の増幅回路41、43のアイドリング電流を決定する。電力検出回路5、6は、最終段出力信号Poutの信号レベルに応答する電力検出信号VDETを生成する。誤差増幅器7に検出信号VDETと目標電力信号VRAMPが供給され、電力制御電圧VAPCが制御信号増強回路9の入力に供給され、出力から増強制御信号VENを生成する。制御信号増強回路9は、所定の非線型の入出力特性を有する。増強制御信号VENが初段と最終段のバイアス回路81、83とに供給され、初段と最終段の増幅回路41、43のアイドリング電流は増強制御信号VENによって制御され、RF電力増幅器の制御利得の低下が補償される。

(もっと読む)

定電圧バッファ回路

【課題】スタートアップ時などに、演算増幅回路の出力電圧が、駆動能力の高い側とは反対方向に大きくずれた場合においても、出力段の定電流源に制限されることなく、所定電圧へのセットリングを加速することが可能な定電圧バッファ回路を提供すること。

【解決手段】基準電圧(Vref)をバッファし、一定電圧の出力電圧(Vout)を供給する定電圧バッファ回路であって、出力電圧と基準電圧とを取得する差動増幅器(1)と、差動増幅器(1)の出力信号に応じて制御されるP型駆動の出力手段(2)と、出力電圧が基準電圧よりも大きいことを検出する検出手段(M11)と、検出手段(M11)において、出力電圧が基準電圧に対して大きいことが検出された場合には、出力ノードから電流を引き出すように電流を制御する電流制御手段(3)とを有する定電圧バッファ回路。

(もっと読む)

オーディオ信号処理回路および電子機器

【課題】アンプに対する電源電圧を好適に制御する。

【解決手段】メインアンプ4は、オーディオ信号S1を増幅する。電源回路2は、アンプの上側電源ラインに正の電源電圧CPVDDを、下側電源ラインに負の電源電圧CPVSSを供給する。電圧検出部32は、アンプにより増幅されたオーディオ信号S2の振幅が所定のしきい値より大きいときアサートされる電圧検出信号S21を生成する。電流検出部34は、メインアンプ4の出力段に流れる負荷電流ILが所定のしきい値電流ITHより大きいときアサートされる電流検出信号S22を生成する。電圧制御部30は、電圧検出信号S21がネゲートされると、電源回路2が生成する正および負の電源電圧の絶対値を低下させる。また電圧検出信号S21がアサートされ、または電流検出信号S22がアサートされると、電源回路2が生成する正および負の電源電圧の絶対値を増大させる。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

演算増幅器

【課題】所定のS/Nを維持しながら消費電流の増加を抑制することのできる演算増幅器を提供する。

【解決手段】実施形態の演算増幅器は、正相信号Vpと逆相信号Vmが入力される差動増幅回路100と、差動増幅回路100へ動作電流を供給するカレントミラー回路200とを有する。この演算増幅器は、入力信号電圧検出回路1が、正相信号Vpと逆相信号Vmとの間の電圧差を検出し、動作電流制御回路2が、その電圧差の大きさに応じた制御信号を出力する。この制御信号の制御により、可変定電流回路3が、カレントミラー回路200へ入力する定電流の大きさを変化させる。

(もっと読む)

1 - 20 / 1,016

[ Back to top ]