Fターム[5J500AM17]の内容

Fターム[5J500AM17]に分類される特許

1 - 20 / 313

スプリッタ回路およびチューナーシステム

演算増幅器

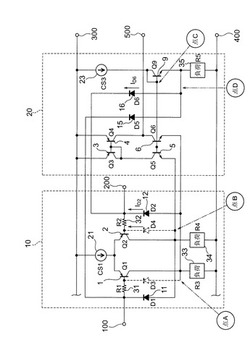

【課題】消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転を防止する。

【解決手段】入力部10の反転入力端子100と第2のトランジスタ2のコレクタとが第1のダ入力部用イオード11を介して、非反転入力端子200と第1のトランジスタ1のコレクタとが第2の入力部用ダイオード12を介して、それぞれ接続される一方、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と反転入力端子100とが第5のダイオード15を介して、第9のトランジスタ9のエミッタと第3の負荷35の相互の接続点と非反転入力端子200とが第6のダイオード16を介して、それぞれ接続されて、消費電流の増加や最低動作電源電圧の上昇などを招くことなく出力位相反転が防止されるようになっている。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】低ノイズ係数(NF)、高利得、及び低電流消費と共に、非常に高い三次入力インターセプトポイント(IIP3)を有する低ノイズ増幅器(LNA)を提供する。

【解決手段】修正された微分重ね合わせ(DS)低ノイズ増幅器(LNA)222は、メイン電流経路320とキャンセル電流経路322を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタ306,308が、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高利得、及び低電流消費と共に、非常に高い三次入力インターセプトポイント(IIP3)を有するLNAを提供する。

【解決手段】LNA222は、メイン電界効果トランジスタ(FET)302、キャンセルFET304、第1ソース・ディジェネレーション・インダクタ306、第2ソース・ディジェネレーション・インダクタ308、カスコード・トランジスタ310、及びLNA負荷312を含む。LNA負荷312は、並列に結合されたインダクタ314及びキャパシタ316を含むLCタンク回路である。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高線形性と低歪みの増幅器を提供する。

【解決手段】修正された微分重ね合わせ低ノイズ増幅器は、メイン電流経路とキャンセル電流経路を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタが、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第2の新規な側面では、LNA負荷を通過しないデブースト電流経路が設けられる。デブースト電流は、ヘッドルームの問題を生じさせることなく、ネガティブ・フィードバックを増加させる。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

増幅器

【課題】歪の発生を少なくする。

【解決手段】入力信号(IN)を受ける初段増幅回路(PREA)と、ゲートに初段増幅回路(PREA)の出力信号を受けるソース接地の第1のトランジスタ(Tr1)と、ソースを第1のトランジスタ(Tr1)のドレインに接続し、ドレインから出力信号(OUT)を送出すると共にドレインに対して電源供給がなされるゲート接地の第2のトランジスタ(Tr2)と、初段増幅回路(PREA)の電源端と第2のトランジスタ(Tr2)のソースとの間に介在する第1のインピーダンス回路(Z1)と、を備える。第1のインピーダンス回路(Z1)は、直流を通過させると共に、所定の周波数帯域において所定のインピーダンス以上となるように構成された回路である。

(もっと読む)

RFパワーモジュール

【課題】多段増幅段を含むRF電力増幅回路の低パワーおよび中間パワー時における電力付加効率(PAE)の低下を軽減する。

【解決手段】RF電力増幅回路313は、前段増幅器310、後段増幅器311、制御部312を具備する。前段増幅器310はRF送信入力信号Pinに応答して、前段増幅器310の出力の増幅信号に後段増幅器311が応答する。制御部312は、出力電力制御電圧Vapcに応答して、前段増幅器310と前記後段増幅器311のアイドリング電流を制御して前段増幅器310と前記後段増幅器311の利得を制御する。出力電力制御電圧Vapcに応答して、前段増幅器310のアイドリング電流と利得とは第1の連続関数2ndAmpに従って連続的に変化して、後段増幅器311のアイドリング電流と利得とは第2の連続関数3rdAmpに従って連続的に変化する。第2の連続関数3rdAmpは、第1の連続関数2ndAmpよりも1次以上高次の関数である。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

【課題】差動入力を有する直交出力低雑音トランスコンダクタンス増幅器を提供する。

【解決手段】低雑音トランスコンダクタンス増幅器200は、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部110と、PMOSトランスコンダクタンス部に結合されたPMOSカスコード部130と、RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部120と、NMOSトランスコンダクタンス部に結合されたNMOSカスコード部140と、を含み、PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号gmpq、gmnq及び差動同相出力信号gmpi、gmniを提供する。RF信号を増幅するための方法は、差動RF入力信号を受信することと、差動RF入力信号を電流信号に変換することと、電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供する。

(もっと読む)

差動増幅回路及びコンパレータ

【課題】オフセット電圧の変動を低減した差動増幅回路及びコンパレータを提供する。

【解決手段】実施形態によれば、差動回路と、出力回路と、クリップ回路と、を備えたことを特徴とする差動増幅回路が提供される。前記差動回路は、一対の入力信号の電位差に応じた一対の差動電流を生成する。前記出力回路は、前記一対の差動電流を受けて、電流差に応じた出力電圧を生成する。前記クリップ回路は、前記出力電圧に応じてオンし、前記出力電圧をしきい値電圧を含みローレベルまたは前記ローレベルよりも高いハイレベルに変換できる範囲に抑制するクリップ素子を有する。

(もっと読む)

レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置

【課題】レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置を提供する。

【解決手段】本願発明は、増幅器であって、入力信号を受け取るための入力ステージと、前記入力ステージに連結されると共に、前記入力信号に応答して出力ドライバステージに対して駆動信号を提供する高利得ステージと、前記出力ドライバステージに連結された出力端子とを具備することを特徴とする。前記出力ドライバステージは、前記高利得ステージから第1の駆動信号“pdrive”を受け取る第1の端子、第1の電圧降下を通じてVDDに連結された第2の端子、及び、前記増幅器の前記出力端子に連結された第3の端子を有する高電位側ドライバ回路を備える。

(もっと読む)

トランスインピーダンスアンプ

【課題】利得周波数特性の広帯域化と群遅延平坦特性とを両立させる。

【解決手段】ソース接地トランジスタM1、ゲート接地トランジスタM2、および負荷抵抗RLからカスコード接続回路11を構成し、ソース接地トランジスタM1のドレイン端子とゲート接地トランジスタM2のソース端子と間に第1のインダクタL1を設ける。

(もっと読む)

アクティブポストディストーション線形化を有する差動増幅器

【課題】電力消費量を低下させ、回路面積を縮小した線形性がより高いLNAを提供する。

【解決手段】差動増幅器300の一腕は第1トランジスタ310及び第2トランジスタは320、第1のカスケード対として結合され、第3トランジスタ330及び第4トランジスタ340は、第2のカスケード対として結合される。第3トランジスタ330は、第2トランジスタ320のソースに結合したゲートを有し、第4トランジスタ340は、第2トランジスタ320のドレインに結合したドレインを有する。第3トランジスタ330は、第1トランジスタ310によって生成される3次歪み成分を除去するのに用いられる歪み成分を生成する。誘導子350は、第1トランジスタ310に対してソースディジェネレーションを提供し、歪み除去を向上させる。第2トランジスタ320及び第3のトランジスタ330の大きさは、利得損失を低減させるために選択される。

(もっと読む)

増幅回路

【課題】追加プロセスなしに、コモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる高耐圧の入力段とすることが可能な増幅回路を提供する。

【解決手段】増幅回路の入力段は、入力端子IN1,IN2が接続された第1の差動対トランジスタ10と、N1VDDに接続された第1の入力段電流バイアス手段20と、第1の差動対トランジスタ10と第1の入力段電流バイアス手段20に接続された第1の入力段カスコードトランジスタ群30と、第1の差動対トランジスタ10に接続された第2の入力段カスコードトランジスタ群40と、0VからN1VDDまで変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のVGSとVGDの絶対値がVDD以内となるバイアス電圧に調整する入力段バイアス調整回路60を備えている。

(もっと読む)

集積されたパワー増幅器を有するCMOSトランシーバ

【課題】通信信号を増幅する絶縁破壊に耐えるトランジスタ構造を提供する。

【解決手段】入力無線周波数信号を受信するため接地点と第1のゲートに接続されたソースを有する第1のNMOSトランジスタ12は、第1のトランスコンダクタンスと第1の破壊電圧とを有する。また第2のNMOSトランジスタは、第1のNMOSトランジスタのドレインに接続されたソースと、基準DC電圧に接続されたゲートと、増幅された無線信号の出力を与えるドレインと、基準DC電圧と第2のNMOSトランジスタのドレインとの間に配置された負荷とを有する。第2のNMOSトランジスタ14は第2のトランスコンダクタンスと第2の破壊電圧とを有し、第2の絶縁体は第1の絶縁体よりも厚い。この結果、第1のトランスコンダクタンスは第2のトランスコンダクタンスよりも大きく、第2の破壊電圧は第1の破壊電圧よりも大きい。

(もっと読む)

電力増幅器

【課題】高調波信号が基本波増幅器に効率よく注入され、高効率化を図る電力増幅器を得る。

【解決手段】基本波増幅器3と、基本波増幅器3から発生する高調波信号を基本波信号から分波する第1分波回路と、第1分波回路から出力された高調波信号を基本波増幅器3の入力側又は出力側に注入するための高調波伝達回路15と、高調波伝達回路15から出力された高調波信号を基本波増幅器3に注入する第2分波回路とを備え、高調波信号を基本波増幅器3に注入し、基本波増幅器3の効率を高めるようにしたものである。

(もっと読む)

分布定数型増幅器

【課題】分布定数型差動増幅器の出力波形におけるジッタを低減する。

【解決手段】分布定数型増幅器は、複数の増幅器を有する。複数の増幅器はそれぞれ、固有の遅延時間を持って一の信号源からの入力信号を受ける。また、複数の増幅器はそれぞれ、固有の遅延時間に対応する遅延時間をもって共通の負荷に出力信号を提供する。複数の増幅器それぞれに関して、固有の遅延時間と対応する遅延時間の和は等しく設定されている。複数の増幅器のそれぞれは、一対の差動トランジスタと、該一対の差動トランジスタと当該増幅器の出力との間に直列に挿入された一対のカスコードトランジスタを含む。一対の差動トランジスタは、当該一対の差動トランジスタそれぞれのコレクタ−ベース間の接合容量が準飽和領域の接合容量となるように、バイアスされている。

(もっと読む)

カレントミラー回路及びそれを有する増幅回路

【課題】電源電圧の変動に対する出力電流の変動が小さいカレントミラー回路を提供すること。

【解決手段】カレントミラー回路5は,トランジスタM12の第2のドレイン電流を第2の比率で複製した第2の複製電流を生成する第2の複製電流生成回路J2と,基準電流と第2の複製電流が流入する接続ノード接続ノードQ1とグランドとの間に設けられ,トランジスタM11の第1のドレイン電流を第1の比率で複製した第1の複製電流を生成する第1の複製電流生成回路J1とを有し,出力トランジスタM10のゲートとトランジスタM11,M12のゲートと接続ノードQ1とが接続されている。

(もっと読む)

カレントミラー回路およびそれを用いた半導体装置

【課題】プロセス変動があった場合でも広い出力電圧範囲が得られるカレントミラー回路を提供する。

【解決手段】この低電圧カスコードカレントミラー回路は、NチャネルMOSトランジスタQ1〜Q5と抵抗素子1を備える。トランジスタQ3のオーバードライブ電圧Vov_Q3は、トランジスタQ4,Q5のオーバードライブ電圧Vov_Q4,Vov_Q5の和に等しい。定電流Icと抵抗素子1の抵抗値R1との積は、トランジスタQ5の飽和マージンVdsm_Q5となる。したがって、プロセス変動があった場合でも、トランジスタQ5の飽和マージンVdsm_Q5は変化しない。

(もっと読む)

利得可変差動増幅回路

【課題】広いダイナミックレンジを確保しつつ利得を変化させることが可能な利得可変差動増幅回路を提供すること。

【解決手段】この利得可変差動増幅回路12は、差動対トランジスタQ1,Q2,Q3,Q4とそれらのトランジスタのそれぞれのコレクタに接続された負荷抵抗14,15,18,19とそれらのトランジスタのエミッタに共通に接続された電流源16,20とをそれぞれ含む差動増幅回路17,21を有し、次段差動増幅回路21の出力を、帰還トランジスタQ5,Q6を介して初段差動増幅回路17に帰還させる利得可変差動増幅回路において、該初段差動対トランジスタQ1,Q2を流れるべき電流を分岐させる電流分岐回路部12Cと、差動対トランジスタQ1,Q2に電流を供給する電流供給回路部12Bとを備える。

(もっと読む)

1 - 20 / 313

[ Back to top ]