Fターム[5J500AM21]の内容

Fターム[5J500AM21]に分類される特許

1 - 20 / 988

正帰還増幅器およびインターポレーション回路

D級増幅器

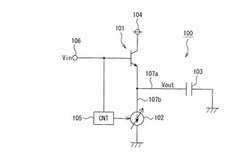

トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

(もっと読む)

トランスインピーダンスアンプ

【課題】入力電流の大きさに応じた量の電流を入力電流から分流することによりダイナミックレンジが拡大されたトランスインピーダンスアンプ(TIA)において、入力インピーダンスの変化を低減する。

【解決手段】TIA10は、光電流Iinの大きさに応じた出力電圧Voutを生成する。TIA10は、光電流Iinを出力電圧Voutに変換する利得可変増幅回路12と、光電流Iinが大きいほど大きな電流Icdを光電流Iinから分流する分流回路14と、光電流Iinが大きいほど利得可変増幅回路12の利得を小さくする利得調整回路20とを備える。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】SOI基板にLNA回路を形成した場合や、バルクCMOSプロセスを用いてLNA回路を形成した場合に、NFの劣化の回避と高い線形性の達成とを実現することが可能なCMOS集積回路を提供する。

【解決手段】ゲート電極に信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された電界効果トランジスタを備え、前記電界効果トランジスタはSOI(Silicon−On−Insulator)基板上に形成し、ボディ電位と、ソース電位以下の電位との間を、抵抗素子で接続することを特徴とする、CMOS集積回路が提供される。かかるCMOS集積回路を用いることで、NFの劣化の回避と高い線形性の達成とを実現することが可能となる。

(もっと読む)

増幅器

【課題】 携帯電話をはじめとする移動体通信用高周波電力増幅器などの増幅器において、受信帯雑音特性が良好で小型な増幅器を提供する。

【解決手段】 第一の周波数を中心周波数とする信号を増幅する増幅素子と、前記増幅素子の前段または後段に接続される整合回路と、前記増幅素子と前記整合回路の間に接続され、前記第一の周波数とは異なる第二の周波数を中心周波数とする信号を減衰させるフィルタ回路と、を備えたことを特徴とする。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

オペアンプ補償回路

【課題】出力バッファを有するオペアンプA1であつて、オフセット電位を従来よりも抑えられるオペアンプ補償回路を提供する。

【解決手段】バッファの出力と接地間に、入力信号が接地から電源電圧まで変化されるMOSトランジスタT1を有し、あるいは、NチャンネルトランジスタTN1と、PチャンネルトランジスタTP1とを並列接続し、それぞれ入力信号と反転された入力信号が入力されている構成を有し、オフセット電位が接地となることを特徴とする。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

EM級増幅器

【課題】高調波歪みを容易に低減させることのできるEM級増幅器を提供する。

【解決手段】本発明にかかるEM級増幅器は、主回路と、主回路に信号を入力する補助回路と、を有するEM増幅器であって、主回路は、プッシュプル構造を有することを特徴とする。この場合において、限定されるわけではないが、プッシュプル構造は、第一の主基礎回路と、第一の主基礎回路と同様な構造の第二の主基礎回路と、第一の主基礎回路と第二の主基礎回路に接続される負荷回路と、を有して構成される。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高線形性と低歪みの増幅器を提供する。

【解決手段】修正された微分重ね合わせ低ノイズ増幅器は、メイン電流経路とキャンセル電流経路を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタが、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第2の新規な側面では、LNA負荷を通過しないデブースト電流経路が設けられる。デブースト電流は、ヘッドルームの問題を生じさせることなく、ネガティブ・フィードバックを増加させる。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

増幅器

【課題】歪の発生を少なくする。

【解決手段】入力信号(IN)を受ける初段増幅回路(PREA)と、ゲートに初段増幅回路(PREA)の出力信号を受けるソース接地の第1のトランジスタ(Tr1)と、ソースを第1のトランジスタ(Tr1)のドレインに接続し、ドレインから出力信号(OUT)を送出すると共にドレインに対して電源供給がなされるゲート接地の第2のトランジスタ(Tr2)と、初段増幅回路(PREA)の電源端と第2のトランジスタ(Tr2)のソースとの間に介在する第1のインピーダンス回路(Z1)と、を備える。第1のインピーダンス回路(Z1)は、直流を通過させると共に、所定の周波数帯域において所定のインピーダンス以上となるように構成された回路である。

(もっと読む)

信号変換回路ならびにそれを用いた増幅回路,送信装置および通信装置

【課題】 不要パルスの発生が抑制された信号変換回路およびそれを用いた増幅回路,送信装置,通信装置を提供する。

【解決手段】 第1信号S1がソース端子に、第2信号S2がゲート端子に入力されるトランジスタ7と、第1信号S1と第2信号S2とが入力されて、第1信号S1と第2信号S2との位相差の情報を有する第3信号S3を出力する第1回路5と、第1信号S1と第3信号S3とが入力されて、第1信号S1の位相を所定の値だけシフトさせた位相を有する信号に、第1信号S1と第2信号S2との位相差に応じてバイアス電圧を加えた信号である第4信号S4を出力する第2回路6と、ソース端子がトランジスタ7のドレイン端子に接続されているとともにゲート端子に第4信号S4が入力されて、第1信号S1と第2信号S2との位相差に応じてデューティ比が変化する第5信号S5をドレイン端子から出力するトランジスタ9とを有する信号変換回路とする。

(もっと読む)

高周波増幅器

【課題】安定化を図りながらソース接地FET素子が本来持つ最大有能利得を十分に生かせる高周波増幅器を提供する。

【解決手段】高周波増幅器は、ソース端子が接地される増幅用ソース接地FET素子と、増幅用FET素子のゲート端子に接続され、増幅用ソース接地FET素子のドレイン端子の印加電圧が増えるに応じてインピーダンスが高くなるように変化する安定化回路と、を備える。安定化回路は、例えば、増幅用ソース接地FET素子のゲート端子に接続するコンデンサと、コンデンサにドレイン端子が接続し、ゲート端子が接地し、ソース端子が増幅用FET素子のドレイン端子に接続するインピーダンス調整用FET素子と、インピーダンス調整用FET素子のソース端子に接続され、接地される抵抗と、この抵抗に接続し、接地されるコンデンサと、を備える。

(もっと読む)

受信回路

【課題】正の単一電源で作動(動作)するオペアンプを用いて負の信号レベルの信号を含む受信信号を増幅することのできる受信回路を提供する。

【解決手段】受信回路100は、基準端子11と基準端子11の電圧を基準とする受信信号を出力する信号端子12とを有する信号部10と、正の入力端子21と負の入力端子22と出力端子23とを有し、正の単一電源E2から電圧が印加されて作動するオペアンプ20と、出力端子23と負の入力端子22との間に接続される第1負荷部30と、信号端子12と負の入力端子22との間に接続される第2負荷部40と、カソード側が接地され、アノード側が基準端子11と正の入力端子21とに接続されるダイオード52を含む基準電圧部50と、を備える。

(もっと読む)

受光回路

【課題】受光回路の消費電流を削減する。

【解決手段】一つの実施形態によれば、受光回路は、トランスインピーダンスアンプと出力回路が設けられる。トランスインピーダンスアンプは、フォトダイオード、帰還抵抗、及び第1のトランジスタが設けられる。フォトダイオードは、光信号を電気信号に変換する。帰還抵抗は、フォトダイオードと内部出力端子の間に設けられる。第1のトランジスタは、ゲートにフォトダイオードで光電変換された電気信号が入力され、ドレインが内部出力端子に接続される。出力回路は、第1のトランジスタと同一チャネル型であり、ゲートが内部出力端子に接続され、電流源負荷が接続されるとともにドレイン側から出力信号を出力する第2のトランジスタを含む。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

電力増幅装置

【課題】主信号の変調帯域と相互変調積の周波数範囲外となる周波数では高インピーダンスでスプリアス低減効果のある電力増幅装置を提供する。

【解決手段】実施形態によれば、入力信号を第1信号及び第2信号を含む伝送信号に電力増幅するFET103と、FET103から出力される伝送信号のインダクタ成分を低減する第1のデカップリング素子104と、FET103に対し駆動電力を供給する電源回路200と、電源回路200に対しFETの出力端子106から出力されるRF成分をカットする第2のデカップリング素子300と、第1のデカップリング素子104と第2のデカップリング素子300との間に接続され、第1信号の変調帯域とFETの出力信号における相互変調積の周波数領域では所定の第1インピーダンスで、第1信号の変調帯域と相互変調積の周波数領域外では第2インピーダンスを有するフィルタ400とを備える。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

1 - 20 / 988

[ Back to top ]