Fターム[5J500AQ01]の内容

Fターム[5J500AQ01]の下位に属するFターム

断面構造、積層構造 (186)

平面構造、レイアウト (202)

Fターム[5J500AQ01]に分類される特許

1 - 7 / 7

CMOS集積回路及び増幅回路

【課題】SOI基板にLNA回路を形成した場合や、バルクCMOSプロセスを用いてLNA回路を形成した場合に、NFの劣化の回避と高い線形性の達成とを実現することが可能なCMOS集積回路を提供する。

【解決手段】ゲート電極に信号入力端子が、ドレイン電極に電源端子が、ソース電極に接地端子がそれぞれ接続された電界効果トランジスタを備え、前記電界効果トランジスタはSOI(Silicon−On−Insulator)基板上に形成し、ボディ電位と、ソース電位以下の電位との間を、抵抗素子で接続することを特徴とする、CMOS集積回路が提供される。かかるCMOS集積回路を用いることで、NFの劣化の回避と高い線形性の達成とを実現することが可能となる。

(もっと読む)

電力増幅器

【課題】 電力増幅器に発生するホットキャリアの影響を抑制する。

【解決手段】 一つの実施形態の電力増幅器には、半導体層に形成され、少なくとも1つ以上から構成され、電力増幅動作する第1のグロースリングゲート構造体と、半導体層に形成され、第1のグロースリングゲート構造体を取り囲むように隣接配置され、第1の構造体が電力増幅動作するときに、逆バイアスが印加されて空乏化領域が形成され、第1の構造体を周囲からアイソレートする複数の第2のグロースリングゲート構造体とが設けられる。

(もっと読む)

カレントミラー回路

【課題】 プロセスの変動があったとしても、ヒューズトリミングを用いてミラーされた出力電流量を微調整することで精度の良いカレントミラー比が得られるカレントミラー回路の構成を提供する

【解決手段】 ミラー比1:100のカレントミラー回路において第2のMOSトランジスタのゲート幅を第1のMOSトランジスタの90倍で構成し、第1のMOSトランジスタの20倍分を細かく分割して第3のMOSトランジスタ群として第2のMOSトランジスタに並列に接続し、第3のMOSトランジスタ群に直列にトリミング工程にて切断可能なヒューズを接続することを特徴とする。

(もっと読む)

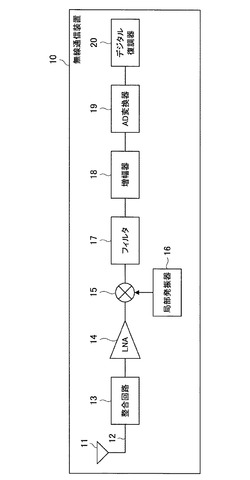

増幅回路及び信号処理装置

【課題】拡散抵抗で形成された抵抗素子でゲインを設定する増幅回路において、入力信号の電圧変化に関わらず、ゲイン及び入出力特性のリニアリティを安定化させ得る増幅回路を提供する。

【解決手段】基板上に形成される拡散層と、拡散層を囲むウェルとを有する拡散抵抗であって、複数の拡散抵抗R18,R19の抵抗値比に基づいてゲインを設定する増幅器15を備えた増幅回路において、ウェルの電位を、該拡散抵抗R18,R19の抵抗体のいずれかの端子から常時自己バイアスで供給する電位供給回路16a,16bを備えた。

(もっと読む)

増幅回路

【課題】外部端子数を増やすことなく、外部端子とエミッタバッドとを結ぶ接続導体の状態を個別に検査可能な増幅回路を提供すること。

【解決手段】増幅回路は、ベース及びコレクタがそれぞれ共通に、並列接続された複数のバイポーラトランジスタと、複数のバイポーラトランジスタの各ベースに接続され、信号が入力されるベースパッドと、複数のバイポーラトランジスタの各コレクタに接続され、複数のバイポーラトランジスタによって増幅された信号を出力するコレクタパッドと、複数のバイポーラトランジスタの各エミッタにそれぞれ接続された、複数のバイポーラトランジスタと同数のエミッタパッドと、エミッタパッド毎に接続された接続導体をエミッタパッドと同数含む接続導体群と、接続導体群に含まれる全ての接続導体が接続された外部端子とを備える。

(もっと読む)

アナログ回路、電子機器及びオペアンプ

【課題】低ノイズと低消費電力を両立できるアナログ回路、電子機器等の提供。

【解決手段】アナログ回路300は、増幅対象信号の周波数が第1の周波数である第1型のオペアンプOP1を有する第1の回路310と、増幅対象信号の周波数が前記第1の周波数よりも低い第2の周波数である第2型のオペアンプOP2を有する第2の回路320を含む。第1型のオペアンプOP1の差動部の差動段トランジスタのチャネル幅をW1aとし、チャネル長をL1aとし、差動部に流れるバイアス電流をIaとし、第2型のオペアンプOP2の差動部の差動段トランジスタのチャネル幅をW1bとし、チャネル長をL1bとし、差動部に流れるバイアス電流をIbとした場合に、W1b×L1b>W1a×L1a、Ia>Ibとなる。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】 信頼性の高い半導体集積回路装置を提供する。

【解決手段】 半導体基板10に設けられ、線対称な配列をなし、配列の外側から内側に向かって配列方向の寸法が大きくなっている複数のゲート電極20と、複数のゲート電極20のいずれか1つの第1のゲート電極を有する第1のトランジスタと、複数のゲート電極20の他の1つの第2のゲート電極を有する第2のトランジスタと、を有し、第1及び第2のトランジスタは、差動対を成し、第1及び第2のゲート電極の配置位置は、配列において、線対称になっている。

(もっと読む)

1 - 7 / 7

[ Back to top ]