Fターム[5J500AQ03]の内容

Fターム[5J500AQ03]に分類される特許

1 - 20 / 202

高周波増幅器

高周波増幅器

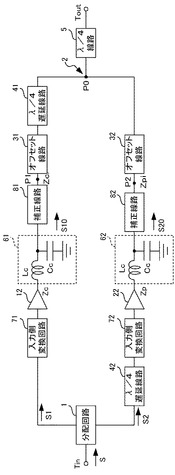

ドハティ増幅器

【課題】 単純な回路構成を有し、調整が容易なドハティ増幅器を提供する。

【解決手段】 第1の入力信号を増幅するキャリアアンプ12と、飽和出力電力がキャリアアンプと異なり、第2の入力信号を増幅するピークアンプ22とを有し、キャリアアンプは、第1のトランジスタと、第1のトランジスタと同一のパッケージ内に設けられた第1の内部変換回路とを含み、ピークアンプは、第2のトランジスタと、第2のトランジスタと同一のパッケージ内に設けられた第2の内部変換回路とを含み、第1及び第2の内部変換回路は、第1及び第2のトランジスタの出力インピーダンスを互いに異なる値に変換する。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

無線装置およびその製造方法

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

(もっと読む)

電力増幅回路および高周波モジュール

【課題】フィードバック制御を行っても、出力電力の低下を抑制できる電力増幅回路を実現する。

【解決手段】電力増幅回路を備える高周波モジュール10は、高周波電力増幅素子20、整合回路30、および駆動電源回路40を備える。高周波電力増幅素子20は、高周波増幅回路210、方向性結合器230を備える。方向性結合器230の主線路231の第1端は、高周波増幅回路210の後段増幅回路212の出力端子に接続されている。主線路231の第2端は、出力整合回路240を介して、高周波電力増幅素子20の高周波信号出力端子Poutに接続されている。後段増幅回路212の出力端子は、高周波電力増幅素子20

子20の第2駆動電源印加端子PV2にも接続されている。高周波信号出力端子Poutと高周波信号出力端子Poutとは、接続導体50で接続されている。

(もっと読む)

デブースト電流経路を有するマルチ線形性モードLNA

【課題】高線形性と低歪みの増幅器を提供する。

【解決手段】修正された微分重ね合わせ低ノイズ増幅器は、メイン電流経路とキャンセル電流経路を含む。キャンセル経路の三次歪みは、メイン経路の三次歪みをキャンセルするために使用される。新規な一側面では、分離されたソース・ディジェネレーション・インダクタが、2つの電流経路の各々につきあり、これにより他方の電流経路に影響を与えることなく、一方の電流経路の調整を容易にする。第2の新規な側面では、LNA負荷を通過しないデブースト電流経路が設けられる。デブースト電流は、ヘッドルームの問題を生じさせることなく、ネガティブ・フィードバックを増加させる。第3の新規な側面では、キャンセル電流経路及び/またはデブースト電流経路がプログラマブルにディセーブルとされて、高線形性を求めない動作モードにおいて電力消費を低減し、ノイズ量を改善する。

(もっと読む)

半導体パッケージ、及び半導体パッケージの製造方法

【課題】高周波電力増幅器の汎用性を確保しつつ、低コスト化及び小型化が可能な半導体パッケージ(P)を提供すること。

【解決手段】接地導体(131)と、前記接地導体(131)の上部に設けられた2層の高周波基板(130)と、上層の前記高周波基板(130)を挟むように設けられた一対の導体(134)と、を含む、半導体パッケージ(P)が提供される。また、この半導体パッケージ(P)を含む高周波電力増幅器(100)が提供される。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

電力増幅器

【課題】本発明は、発振電力を吸収する抵抗の抵抗値を容易に制御できる電力増幅器を提供することを目的とする。

【解決手段】本願の発明に係る電力増幅器10は、複数のトランジスタセルが形成された半導体基板12と、該半導体基板上に形成された、該複数のトランジスタセルのドレイン電極40と、該半導体基板上に該ドレイン電極と接続されるように形成された、ドレインパッド42と、該半導体基板に、該ドレインパッドに沿って該ドレインパッドと接するように形成されたイオン注入抵抗44と、該半導体基板上に該イオン注入抵抗を介して該ドレインパッドと接するように形成されたフローティング電極46と、該半導体基板の外部に形成された出力整合回路16と、該ドレインパッドと該出力整合回路を接続する配線18a,18b,18c,18dと、を備える。

(もっと読む)

高周波電力増幅器

【課題】レイアウト面積を増加させることなく、各トランジスタの負荷インピーダンスを均一にすることができる高周波電力増幅器を得る。

【解決手段】半導体チップ2上に、トランジスタ3a,3bと、トランジスタ3a,3bに隣接したコレクタパッド4a,4bとが設けられている。トランジスタ3a,3bとコレクタパッド4a,4bはそれぞれコレクタ配線6a,6bにより接続されている。半導体チップ2外に外部パッド8が設けられている。この外部パッド8に出力端子9が接続されている。コレクタパッド4a,4bと外部パッド8はそれぞれワイヤ10a,10bにより接続されている。コレクタパッド4aは、コレクタパッド4bよりも外部パッド8から遠い位置に配置されている。コレクタパッド4aから出力端子9までの電気長は、コレクタパッド4bから出力端子9までの電気長と同じである。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

光受信回路

【課題】受光素子の直近にインダクタンス素子を配置することなしに光受信回路を広帯域化する。

【解決手段】光受信回路は、光信号を電気信号に変換する受光素子3と、受光素子3のアノードと出力端子10との間を接続する電気線路4,6と、受光素子3のカソードを交流的に接地すると共に、カソードに直流バイアスを印加するバイアス分離回路5とを備える。電気線路4,6の特性インピーダンスは、出力端子10に接続される負荷抵抗7の抵抗値よりも高い。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

半導体素子の破壊を検知する検知回路

【課題】監視対象の素子の破壊を直接的に検知することを可能にする。

【解決手段】監視対象の半導体素子近傍にモニタ用配線を敷設する一方、所定のクロックを出力するクロック出力手段を当該モニタ用配線の一端に接続し、同モニタ用配線の他端に監視手段を接続する。そして、クロック出力手段からモニタ用配線へ出力されるクロックを伝播を監視手段に監視させ、クロックの伝播が途絶えたことを検出した場合に、監視対象の半導体素子の破壊が生じた旨を通知する破壊通知信号を出力させる。

(もっと読む)

電力増幅器

【課題】MMICとMMIC外部回路とを接続するボンディングワイヤの影響を比較的簡単な構成で低減し、かつ省スペース化された電力増幅器を提供する。

【解決手段】MMIC基板と、MMIC基板上に配置された高周波プローブパッドと、MMIC基板上に高周波プローブパッドに隣接して配置され、MMIC外部回路とのボンディングワイヤ接続用のメタルプレートとを備える。

(もっと読む)

電力分配合成器及び電力増幅器

【課題】入力の整合回路における損失の低減、並びに、回路の簡略化及び小型化が可能な電力分配合成器を提供する。

【解決手段】入力信号が入力される1次巻線としての環状の第1金属配線、及び、2次巻線としての複数の第2金属配線を有し、入力インピーダンスの整合をとるとともに、入力信号を複数の分配信号に分配する入力側トランスフォーマ120と、出力信号が出力される2次巻線としての環状の第3金属配線、及び、1次巻線としての複数の第4金属配線を有し、複数の分配信号を合成することで出力信号を出力するとともに、出力インピーダンスの整合をとる出力側トランスフォーマ130とを備え、入力側トランスフォーマ120が有する金属配線と出力側トランスフォーマ130が有する金属配線とは、互いに異なる金属配線層を用いて構成され、かつ、平面視した場合に交差している。

(もっと読む)

AB級増幅器

【課題】広い帯域に亘って高線形性でかつ高効率なAB級増幅器を提供することにある。

【解決手段】本実施の形態に係るAB級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)を超えて2・π(rad)未満のAB増幅器において、増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2、3倍波の負荷インピーダンスをZ3=R3+j・X3とし、X1とR1の関係を−0.5・R1≦X1≦0.5・R1、R1をR1=Vdc/Imax・{1−cos(θo/2)}・π/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−2・{θo−sin(θo)}/{sin(θo/2)−sin(1.5・θo)/3}に、X3/X1をX3/X1={θo−sin(θo)}/{sin(θo)/3−sin(2・θo)/6}に、あるいはそれぞれの近傍にする。

(もっと読む)

AB級増幅器

【課題】広い帯域に亘って高線形性でかつ高効率なAB級増幅器を提供することにある。

【解決手段】本実施の形態に係るAB級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)を超えて2・π(rad)未満のAB増幅器において、前記増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2とし、X1とR1の関係を−R1≦X1≦R1、R1をR1=Vdc/Imax・π・{1−cos(θo/2)}/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−{θo/2−sin(θo)/2}/{sin(θo/2)−sin(1.5・θo)/3}に、あるいはそれぞれの近傍にする。

(もっと読む)

1 - 20 / 202

[ Back to top ]