Fターム[5J500AT06]の内容

Fターム[5J500AT06]に分類される特許

1 - 20 / 1,275

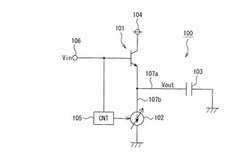

正帰還増幅器およびインターポレーション回路

トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】非反転アンプ14は、第3演算増幅器OA3および分圧回路R1、R2を含み、第1バッファ10の出力電圧を非反転増幅する。スイッチSW2は、第3演算増幅器OA3の出力端子とその反転入力端子の間に設けられる。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW2をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW2をオフする。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

スイッチング回路及び包絡線信号増幅器

【課題】複数のスイッチング素子にて増幅したPWM信号を低損失で合成し、変調信号を復調することが可能なスイッチング回路、及び該スイッチング回路を備える包絡線信号増幅器を提供する。

【解決手段】本発明の一実施形態のスイッチング回路33は、N個(Nは2以上の整数)のトランジスタM1〜Mnのスイッチングを制御するための各制御端子をN−1個のコイルL1を介して縦続接続する接続回路と、一端が直流電源に電気的に接続されるコイルL2の他端及びトランジスタM1〜Mnの各一端の間に各別に接続されたコイルL3とを備え、接続回路の入力端子に入力されるPWM信号にて、スイッチング素子M1〜Mnを順次スイッチングさせるようにしてある。また、スイッチング回路33は、コイルL2の一端側又は他端側に縦続接続されるように挿入されたトランジスタM0を更に備える。

(もっと読む)

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

スイッチドキャパシタ積分器

【課題】演算増幅器の充電にかかる負荷を抑え、低消費電力化を実現できるスイッチドキャパシタ積分器を提供する。

【解決手段】演算増幅器122を含む積分器102、演算増幅器122の入力端子122aに信号を入力するスイッチドキャパシタ回路101、演算増幅器122の出力端子122cと接続する出力端子443を有するスイッチドキャパシタ回路103を含み、積分器102及びスイッチドキャパシタ回路101がサンプリング動作と積分動作とを繰返し、スイッチドキャパシタ回路103は、キャパシタ133、キャパシタ133をサンプル、ホールド動作させるスイッチング素子131、132を含み、スイッチング素子131、132がキャパシタ133を、積分動作中にホールド動作させる。

(もっと読む)

EM級増幅器

【課題】高調波歪みを容易に低減させることのできるEM級増幅器を提供する。

【解決手段】本発明にかかるEM級増幅器は、主回路と、主回路に信号を入力する補助回路と、を有するEM増幅器であって、主回路は、プッシュプル構造を有することを特徴とする。この場合において、限定されるわけではないが、プッシュプル構造は、第一の主基礎回路と、第一の主基礎回路と同様な構造の第二の主基礎回路と、第一の主基礎回路と第二の主基礎回路に接続される負荷回路と、を有して構成される。

(もっと読む)

信号変換回路ならびにそれを用いた増幅回路,送信装置および通信装置

【課題】 入力された信号の位相差が大きいときの出力電力の低下を抑制した信号変換回路を提供する。

【解決手段】 第1信号S1,第2信号S2,第1信号S1をφ1だけ遅延させた第3信号S3,第2信号S2をφ2(φ2=φ1+φ3)だけ遅延させた第4信号S4を出力する第1回路4と、第1信号S1,第2信号S2がソース端子,ゲート端子に入力されて第5信号S5を出力するトランジスタ7と、第3信号S3,第4信号S4がソース端子,ゲート端子に入力されて第6信号S6を出力するトランジスタ8と、第6信号S6をφ4(φ4≧0)だけ遅延させた第7信号S7をスイッチ回路57を介して出力し、第5信号S5をφ5(φ5=180°+φ1+φ4)だけ遅延させた第8信号S8を出力する第2回路5と、スイッチ回路57を制御する第3回路6と、第7信号S7,第8信号S8を加算する第4回路9とを有する信号変換回路とする。

(もっと読む)

RFパルス信号生成用スイッチング回路、RFパルス信号生成回路、および物標探知装置

【課題】安定動作させながら、RFパルス信号の波形を高速に立ち下げることができるRFパルス信号生成用スイッチング回路を提供することにある。

【解決手段】ドレインスイッチング回路21は、n型からなる第1、第2、第3のFET211,212,213を備える。第1、第3のFET211,213のゲートには、制御パルスが印加され、ソースは接地されている。第1のFET211のドレインは、第2のFET212のゲートに接続し、第2のFET212のドレインには、駆動電圧Vdsが印加される。第2のFET212のソースと第3のFET213のドレインは接続され、接続点がパワーFET31のドレインに接続されている。第2のFET212のゲートソース間には、第2のFET212がオフ状態からオン状態へ遷移する際のゲート電圧を補償するための電荷を供給するコンデンサ215が接続されている。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

電子回路およびその制御方法

【課題】ドレインアイドル電流のドリフトを直接補償すること。

【解決手段】入力信号が入力するゲートと、出力信号が出力するドレインとを有するFETを含む電子回路の制御方法であって、前記FETのゲートに前記入力信号が入力してからの時間t経過後における前記入力信号x(t)に対応するドレインアイドル電流の変化量ΔIdq(t)を算出するステップS10と、前記変化量ΔIdq(t)を補償するためのゲートバイアス電圧Vgを算出するステップS12と、前記ゲートバイアス電圧を前記FETのゲートに印加するステップS14と、を含むことを特徴とする電子回路の制御方法。

(もっと読む)

信号変換回路ならびにそれを用いた増幅回路,送信装置および通信装置

【課題】 不要パルスの発生が抑制された信号変換回路およびそれを用いた増幅回路,送信装置,通信装置を提供する。

【解決手段】 第1信号S1がソース端子に、第2信号S2がゲート端子に入力されるトランジスタ7と、第1信号S1と第2信号S2とが入力されて、第1信号S1と第2信号S2との位相差の情報を有する第3信号S3を出力する第1回路5と、第1信号S1と第3信号S3とが入力されて、第1信号S1の位相を所定の値だけシフトさせた位相を有する信号に、第1信号S1と第2信号S2との位相差に応じてバイアス電圧を加えた信号である第4信号S4を出力する第2回路6と、ソース端子がトランジスタ7のドレイン端子に接続されているとともにゲート端子に第4信号S4が入力されて、第1信号S1と第2信号S2との位相差に応じてデューティ比が変化する第5信号S5をドレイン端子から出力するトランジスタ9とを有する信号変換回路とする。

(もっと読む)

イメージセンサー及びこれを備えるX線イメージセンシングモジュール

【課題】高品質のイメージが得られるイメージセンサーを提供する。

【解決手段】検出部で検出された電荷を増幅させ、入力端子、増幅端子、及び出力端子を含む電荷検出増幅部を備え、電荷検出増幅部は、入力端子と前記増幅端子との間に接続された第1キャパシタと、入力端子と前記増幅端子との間に接続された第1スイッチングユニットと、増幅端子と出力端子との間に接続された第2キャパシタと、出力端子と基準電圧端子との間に接続された第2スイッチングユニットと、を備えることを特徴とするイメージセンサー。

(もっと読む)

RF電力増幅器およびその動作方法

【課題】ランプアップまたはランプダウンにおいてスイッチングスペクトラムの劣化を軽減すること。

【解決手段】初段と最終段のバイアス回路81、83が、初段と最終段の増幅回路41、43のアイドリング電流を決定する。電力検出回路5、6は、最終段出力信号Poutの信号レベルに応答する電力検出信号VDETを生成する。誤差増幅器7に検出信号VDETと目標電力信号VRAMPが供給され、電力制御電圧VAPCが制御信号増強回路9の入力に供給され、出力から増強制御信号VENを生成する。制御信号増強回路9は、所定の非線型の入出力特性を有する。増強制御信号VENが初段と最終段のバイアス回路81、83とに供給され、初段と最終段の増幅回路41、43のアイドリング電流は増強制御信号VENによって制御され、RF電力増幅器の制御利得の低下が補償される。

(もっと読む)

電力増幅器および電力増幅方法

【課題】ACLRが劣化しないTDD方式用の無線送信用電力増幅器および電力増幅方法を提供する。

【解決手段】CPU7が、終段増幅部5からのループバック信号をFFT部22でスペクトラム分析し送信タイミングと同期してACLRモニタ部が測定したACLR値を監視し、送信開始直後のタイミングでもそのACLR値が所定の閾値以下になるように制御電源部23から終段増幅部5に印加するドレイン電圧を調整する。

(もっと読む)

チャージポンプ回路およびその制御回路、オーディオ信号処理回路、電子機器

【課題】昇圧率の切りかえの際に、電流の逆流を防止する。

【解決手段】コントローラ10は、第1スイッチSW1から第7スイッチSW7のオン、オフ状態を制御することにより、(1)第1モードにおいて、第3端子P3に入力電圧VDDを、第4端子P4に入力電圧VDDを反転した負電圧−VDDを発生させ、(2)第2モードにおいて、第3端子P3に入力電圧VDDの略1/2倍の電圧を、第4端子P4に、入力電圧VDDの略1/2倍の電圧を反転した負電圧−VDD/2を発生させる。コントローラ10は、第1モードから第2モードへの移行を指示されると、遷移期間にわたり、第3スイッチおよび第5スイッチをオンする第1状態と、第2スイッチおよび第4スイッチをオンする第2状態と、を交互に繰り返す第3モードで動作し、その後、第2モードで動作する。

(もっと読む)

RF電力伝送、変調および増幅のシステムおよび方法

【課題】ベクトル結合電力増幅のための方法およびシステムが、本明細書で開示される。

【解決手段】一実施形態では、複数の信号は個別に増幅され、次いで加算されて、所望の時変複素包絡線信号が形成される。1つまたは複数のこれらの信号の位相および/または周波数特性は、所望の時変複素包絡線信号の所望の位相、周波数、および/または振幅特性を提供するように制御される。別の実施形態では、時変複素包絡線信号は、複数の定包絡線成分信号に分解される。これらの成分信号は等しくあるいはほぼ等しく増幅され、次いで加算されて、元の時変包絡線信号の増幅されたバージョンが構成される。実施形態はまた、周波数アップコンバージョンをも行う。

(もっと読む)

光信号受信回路

【課題】耐ノイズ性を高めつつ、ノイズ光を誤検知しても消費電力を抑えることができる光信号受信回路を提供する。

【解決手段】光信号受信回路10は、光信号を受信して電流信号を出力するフォトダイオードPDと、復調信号を出力する信号処理回路20と、信号処理回路20の電流源を制御する電流源制御回路30とを備えている。電流源制御回路30は、フォトダイオードPDからの電流信号に応じて光信号を検出した場合に、光信号検出信号を出力する第1の制御回路32と、光信号検出信号に基づいて信号処理回路20のアクティブ型のバンドパスフィルタである第1のBPF回路23へバイアス電流を供給する第1の電流源回路33と、第1のBPF回路23からの信号でキャリア成分を検出した場合に、キャリア検出信号を出力する第2の制御回路35と、キャリア検出信号に基づいて信号処理回路20へバイアス電流を供給する第2の電流源回路36とを備えている。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

1 - 20 / 1,275

[ Back to top ]