Fターム[5J500CA01]の内容

Fターム[5J500CA01]に分類される特許

1 - 13 / 13

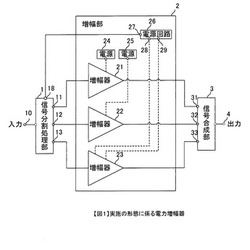

電力増幅装置

【課題】 平均電力に対するピーク電力の比が高い信号を増幅する際の電力変換効率を向上させることができる電力増幅装置を提供する。

【解決手段】 異なる入力レベルの信号を飽和に近い動作で増幅する増幅器21〜23と、入力信号をレベルに応じて適切な増幅器に出力する信号分割処理部1と、各増幅器からの出力を低損失で合成する信号合成部3とを備え、増幅器21〜23の出力インピーダンスを同一の値とし、信号合成部3の位相調整線路301〜303と出力線路304の特性インピーダンスを増幅器の出力インピーダンスと同一の値とし、合成点305におけるインピーダンスが、動作していない増幅器に対して開放となるよう位相調整線路301〜303のインピーダンスが調整され、動作している増幅器に対して増幅器の出力インピーダンスとなるよう出力線路304のインピーダンスが調整されている電力増幅装置としている。

(もっと読む)

液晶駆動用のソースドライバのオフセット低減出力回路

【課題】 出力アンプのオフセット電圧を適切に低減して表示品質の悪化を防止することができる液晶駆動用のソースドライバのオフセット低減出力回路を提供する。

【解決手段】 基準電圧がオペアンプの非反転入力端に印加されたオペアンプと、少なくとも通常出力動作時にオペアンプの反転入力端に接続される第1の接続点に各々の一端が接続された第1の入力コンデンサ及び第1の出力コンデンサと、リセット動作時に第1の入力コンデンサ及び第1の出力コンデンサ各々の両端を短絡してその両端に基準電圧を印加し、リセット動作後の通常出力動作時に第1の入力コンデンサの他端に階調電圧を印加しかつ第1の出力コンデンサの他端をオペアンプの出力端に接続する第1のスイッチ素子回路と、を備え、第1のスイッチ素子回路は、第1の接続点とオペアンプの出力端との間に接続され、リセット動作時にオンとなり、通常出力動作時にオフとなる直列接続の第1及び第2のスイッチ素子を有し、通常出力動作時には第1及び第2のスイッチ素子の直列接続点に基準電圧を印加する。

(もっと読む)

電荷電圧変換回路、検出装置及び電子機器

【課題】電荷電圧変換後の電圧信号のS/Nを向上する電荷電圧変換回路、検出装置及び電子機器等を提供すること。

【解決手段】電荷電圧変換回路は、キャパシターC1と、差動電流信号を構成する第1の信号ISPが供給される第1の入力ノードNI1と、キャパシターC1の一端側のノードである第1のノードN1との間に設けられる第1の入力用スイッチ素子NI1と、差動電流信号を構成する第2の信号ISMが供給される第2の入力ノードNI2と、第1のノードN1との間に設けられる第2の入力用スイッチ素子NI2と、キャパシターC1に蓄積された電荷に対応する電圧信号を出力するための出力用スイッチ素子SQ1と、を含む。

(もっと読む)

アナログスイッチ回路

【課題】切替え時のノイズを低減したアナログスイッチ回路を提供する。

【解決手段】入力信号をn個(nは、1以上)の出力信号としてそれぞれ出力するn個のスイッチ素子と、前記n個のスイッチ素子を制御するスイッチ制御回路と、前記入力信号の負荷となるインピーダンス素子と、前記インピーダンス素子を制御するインピーダンス制御回路と、を備え、前記スイッチ制御回路は、前記n個のスイッチ素子のすべてがオフ、またはいずれか1つがオンとなるように制御し、前記インピーダンス制御回路は、前記n個のスイッチ素子のいずれか1つがオンのときは、前記インピーダンス素子を最大のインピーダンスに制御し、前記n個のスイッチ素子がすべてオフのときは、前記インピーダンス素子を前記最大のインピーダンスよりも小さい第1のインピーダンスに制御する、ことを特徴とするアナログスイッチ回路が提供される。

(もっと読む)

差動増幅器及び演算増幅器

【課題】薄膜トランジスタで回路構成した場合であっても安定した動作をする差動増幅器やセンスアンプ等を提供する。

【解決手段】差動増幅回路(10)とイコライズ回路(20)とを有する差動増幅器において、差動増幅回路(10)は差動出力を発生する第一及び第二出力端(Vout1,Vout2)を有し、イコライズ回路(20)は、第一及び第二出力端相互間に接続された、NMOS TFT(TN3)及びPMOS TFT(TP3)の直列回路(20)によって構成される。

(もっと読む)

低雑音増幅回路

【課題】 低雑音で 100n秒以下の起動および停止による高速な間欠動作を可能とする。

【解決手段】 入力端子からトランジスタのゲートに容量を介して信号、第1の抵抗を介してバイアス電圧を入力し、ドレインから増幅した信号を出力する第1の増幅器と、第1の増幅器の出力信号を容量を介して差動接続された一方のトランジスタのゲートに、第2の抵抗を介して差動接続された他方のトランジスタのゲートに入力し、各ドレインから増幅した差動信号を出力する第2の増幅器と、第1および第2の増幅器と電源との間の接続状態を第1の制御信号に応じてオンオフし、第1および第2の増幅器の動作状態および休止状態を制御する間欠動作制御手段とを備えたLNAにおいて、動作状態から休止状態へ遷移するとき、または休止状態から動作状態に遷移するときに、第1および第2の抵抗の抵抗値を所定時間だけ下げた状態に設定して遷移させる状態遷移制御手段を備える。

(もっと読む)

スイッチトキャパシタ回路

【課題】スイッチトキャパシタ回路におけるシングル/差動変換時の演算増幅器の同相入力変動を抑制し、低電源電圧での変換、または高速の変換にも対応することが可能なスイッチトキャパシタ回路を実現する。

【解決手段】サンプリングモード時とホールドモード時とで第1の演算増幅器110の入力側のキャパシタC1〜C4をスイッチ回路SWで切り換えて単相入力信号を差動出力信号に変換するについて、ホールドモード時に非帰還用キャパシタC2、C3の一端側に供給する第2の参照信号(電圧VCMa)を第1の演算増幅器110の同相入力を所定の定常値とするような値にする第2参照信号生成部20(第2の演算増幅器120)を設けた。

(もっと読む)

オーディオ信号処理装置およびオーディオ信号処理方法

【課題】入力されるオーディオ信号について、直流成分が少ないオーディオ信号の音質を悪化させず、直流成分が多いオーディオ信号の音質を向上させることができるオーディオ信号処理装置およびオーディオ信号処理方法を提供すること。

【解決手段】本発明の実施形態に係るオーディオ信号処理装置100は、含まれる直流成分が多い低品質なオーディオ信号Sinが入力されたときには、直流成分除去部1においてその直流成分を除去したオーディオ信号Shを出力部2から出力させることができる一方、含まれる直流成分が少ない高品質なオーディオ信号Sinが入力されたときには、その品質を維持したままオーディオ信号Sinを出力部2から出力させることができる。

(もっと読む)

トランジスタ出力回路と方法

【課題】トランジスタ出力回路と方法を提供する。

【解決手段】トランジスタ回路は、第一出力トランジスタ、第二出力トランジスタ、及び、スイッチ装置、からなる。第一、第二出力トランジスタは、出力信号をトランジスタ回路のコモン出力端に提供する。スイッチ装置は、第一出力トランジスタの出力端と第二出力トランジスタの出力端をコモン出力端に順に結合する。第一、第二出力トランジスタは同じ定常状態出力を提供するように制御される。スイッチ装置の操作により、第一出力トランジスタの出力端がコモン出力端に結合される時、第一出力トランジスタの駆動状態電圧の変化が第二出力トランジスタから隔離される。

(もっと読む)

バイアス電圧生成回路およびこれを用いたレーダ装置

【課題】電力増幅から出力されるマイクロ波パルスの占有周波数帯域幅を所望の範囲まで狭くすることができるバイアス電圧生成回路を提供する。

【解決手段】入力されたマイクロ波パルスを電力増幅する電力増幅器11に供給するバイアス電圧を生成するバイアス電圧生成回路12であって、入力された制御信号に基づき駆動信号を生成する駆動回路21と、駆動回路で生成された駆動信号が所定電圧以下にならないようにクランプするクランプ回路22と、クランプ回路によってクランプされた信号の立ち上がり時間および立ち下がり時間を制御して波形整形する時定数回路23と、時定数回路によって波形整形された信号に応じて、電圧源から供給される電圧を制御し、バイアス電圧として電力増幅器に供給するトランジスタ24とを備える。

(もっと読む)

高周波電力増幅回路

【課題】パルス動作により間歇的に高周波電力増幅を行う、高周波用のパワーMOS・FETを用いた高周波電力増幅回路において、ゲートパルスによるバイアス電圧の掛け方を工夫することで、パワーMOS・FETの出力パルス幅を拡げて、かつ安全性の高い動作を期待できる、経済的に有利な回路構成とした。

【解決手段】波形成形回路20は、ゲートパルス入力端21に入力されたゲートパルスGP(in)を出力電位が漸減する所定幅のゲートパルスGP(out)に成形して、増幅回路10のパワーMOS・FET12,13のゲート電極(G)に供給する。

(もっと読む)

高周波電力増幅回路

【課題】経済的に有利な構成の高周波電力増幅回路を提供する。

【解決手段】高周波用パワーMOS・FET11がゲート−ドレイン間ショートの故障モードに陥り、電圧制限用バリスタ13に設定電圧を超える高電圧が印加されたとき、電圧制限用バリスタ13は印加された過剰電圧分を放電する。この放電電流により過電流保護ヒューズ14がゲート電極(G)−ゲートパルス入力端(Tgb)間の電流路を遮断する。

(もっと読む)

サンプルホールド増幅回路、相関二重サンプリング回路

【課題】消費電流及び回路実装面積を低減すると共に、前の信号処理がその後の信号処理に影響を与えることのないサンプルホールド増幅回路を提供する。

【解決手段】CCD出力信号CDSINのフィードスルー期間に同期したSHP信号でスイッチS11が閉じ、サンプリング用コンデンサC11にフィードスルーレベルをサンプルホールドする。同時に、SHP信号でスイッチS12及びスイッチS15を閉じて、差動増幅器A11及びインバータA12をリセットする。CDSINのデータ期間では、SHHバー信号でスイッチS13が閉じて差動増幅器A11とインバータA12を接続すると共に、SHHバー信号でスイッチS14を閉じ、データレベルとサンプルホールドしたフィードスルーレベルの差分を、サンプリング用コンデンサC11及びアンプ用コンデンサC12の各容量CS、CAの比、CS/CA倍に増幅する。

(もっと読む)

1 - 13 / 13

[ Back to top ]