Fターム[5J500DN11]の内容

Fターム[5J500DN11]の下位に属するFターム

能動素子を用いるもの(能動負荷) (301)

コレクタ(ドレイン)間挿入負荷 (12)

Fターム[5J500DN11]に分類される特許

1 - 13 / 13

高周波差動増幅回路

【課題】安定性が高く、かつ高い利得を有する高周波差動増幅回路を提供する。

【解決手段】本発明の一実施形態としての高周波差増増幅回路は、第1MOSトランジスタ、第2MOSトランジスタ、第1正帰還素子および第2正帰還素子を備える。前記第1MOSトランジスタおよび第2MOSトランジスタは、ソースがそれぞれ第1電源に接続され、ドレインがそれぞれ負荷を介して第2電源に接続され、互いに反転した位相関係にある第1および第2入力信号をゲートで受ける。前記第1正帰還素子は、前記第1MOSトランジスタのゲートと、前記第2MOSトランジスタのドレインとの間に直列接続された第1キャパシタおよび第1可変抵抗を含む。前記第2正帰還素子は、前記第2MOSトランジスタのゲートと、前記第1MOSトランジスタのドレインとの間に直列接続された第2キャパシタおよび第2可変抵抗を含む。

(もっと読む)

オペレイショナル・トランスコンダクタンス・アンプ、オペレイショナル・トランスコンダクタンス・アンプを用いたフィルタ回路

【課題】入力電圧範囲を広くしても線形性能の優れ、かつトランスコンダクタンス値精度の優れたOTA、OTAを用いたフィルタ回路を提供する。

【解決手段】I−V変換器と、内部抵抗素子の抵抗値に比例する増幅率でI−V変換器の出力電流を増幅する電流制御回路1、2とによってOTAを構成する。そして、電流制御回路1、2を、入力電流が入力されるドレイン、第1制御電圧が供給されるゲートを有するMOSトランジスタ10、出力電流が出力されるドレインを有するMOSトランジスタ13、第2制御電圧が供給されるゲートを有するMOSトランジスタ11、MOSトランジスタ10のドレインと接続される非反転入力端子、MOSトランジスタ13のゲートと接続される出力端子、MOSトランジスタ13のソース及びMOSトランジスタ11のドレインと接続される反転入力端子を有する差動増幅器12によって構成する。

(もっと読む)

増幅回路、集積回路装置及び電子機器

【課題】特性が安定し、増幅効率の良い増幅回路、集積回路装置及び電子機器等を提供すること。

【解決手段】増幅回路は、出力ノードNPに増幅信号VPを出力する増幅用トランジスター10と、インダクターLA及びキャパシターCA、CBにより構成され、インダクターのインダクタンス値及びキャパシターのキャパシタンス値の少なくとも一方が可変に設定されるLC負荷回路20と、増幅信号VPの電圧振幅を検出する振幅検出回路30と、振幅検出回路30の検出結果に基づいてインダクタンス値及びキャパシタンス値の少なくとも一方を設定し、増幅信号VPの電圧振幅値を極大値に近づける制御を行う制御回路40とを含む。

(もっと読む)

半導体集積回路

【課題】電源ノイズ耐性の優れた低消費電流の増幅器を提供する。

【解決手段】トランジスタ対(MN1,MN2)を用いて電流/電圧変換容量素子(CL1,CL2)を第1の電源(VSS)レベルにプリチャージする。このプリチャージ完了後、第2の電源から、差動トランジスタ対(MP1,MP2)を介して定電流を入力信号(VIP,VIN)に応じて振り分けて容量素子に供給する。

(もっと読む)

増幅回路および光変調器用ドライバ回路

【課題】大振幅出力および広帯域周波数特性を確保することができ、特に光変調器のドライバICに適用可能な増幅回路を提供する。

【解決手段】増幅回路は、入力段トランジスタ11と出力段トランジスタ12とを含み、入力された信号を入力段トランジスタ11および出力段トランジスタ12で増幅して出力する多段増幅部10と、多段増幅部10の出力を、該多段増幅部における出力段トランジスタ12の入力に帰還する帰還部20と、を備える。帰還部20は、第1帰還トランジスタ21a、第2帰還トランジスタ21bおよび帰還抵抗RFを含み、多段増幅部10の出力を、第1帰還トランジスタ21a、第2帰還トランジスタ21bおよび帰還抵抗RFを介して出力段トランジスタ12の入力に帰還する。

(もっと読む)

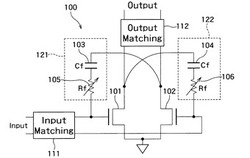

半導体装置

【課題】電源電圧の変動等に起因するゲインの変動を防ぐことが可能な半導体装置を提供する。

【解決手段】半導体装置100は、供給された電流を差動出力電圧に変換する負荷部1と、差動入力電圧を電流に変換して負荷部1に供給するトランスコンダクタンス回路2と、制御電圧に基づいて負荷部1に電流を供給する電圧制御電流源部3と、負荷部1で変換された差動出力電圧に基づいて電圧制御電流源部3に制御電圧を供給する出力電圧制御回路4とを備える。

(もっと読む)

多段差動増幅器

【課題】高出力増幅器のような高飽和特性が要求される差動増幅器において、入力信号の同相成分を除去する機能を改善し、差動利得特性の劣化を防止する。

【解決手段】半導体増幅素子から構成されるエミッタ接地形多段差動増幅器において、少なくとも最前段増幅器の入力バイアス回路には該増幅器を構成する半導体増幅素子の入力インピーダンスの絶対値の1/2以上のインピーダンスを有するフィード素子を用いる。

(もっと読む)

バイアス回路

【課題】個々のトランジスタの動作電圧の違いに起因する抵抗負荷差動増幅器の利得のバラつきを抑え、その利得が精度よく一定となるバイアス回路を提供する。

【解決手段】カレントミラー20は、差動対10を構成している一対のトランジスタM11及びM12の各々のドレインへ同量の電流を流し込む。電流源30は、利得安定化の対象である抵抗負荷差動増幅器の負荷抵抗に反比例している電流を流し出す。この電流は、差動対10の出力点である、トランジスタM12のドレインへ流し込まれる。テール電流調整回路40は、トランジスタM13のゲートに印加する電圧を変化させて差動対10のテール電流Iss1を制御し、差動対10の出力電流を電流源30が流し出す電流に一致させる。更に、利得安定化の対象である抵抗負荷差動増幅器を構成している差動対のテール電流を制御して、このテール電流をテール電流Iss1の変化に比例させる。

(もっと読む)

差動増幅回路

【課題】本発明は、広い入力電圧範囲に対して適切に動作可能であり、且つ低い電源電圧でも適切に動作可能な差動増幅回路を提供することを目的とする。

【解決手段】差動増幅回路は、第1の負荷と、第1の負荷にドレイン端が結合された第1のMOSトランジスタと、第2の負荷と、第2の負荷にドレイン端が結合された第2のMOSトランジスタと、第1及び第2のMOSトランジスタのソース端に共通に結合される第1の定電流源と、第1の負荷にソース端が結合された第3のMOSトランジスタと、第2の負荷にソース端が結合された第4のMOSトランジスタと、第3及び第4のMOSトランジスタのドレイン端に共通に結合される第2の定電流源を含み、第1及び第2のMOSトランジスタは第1の導通タイプであり、第3及び第4のMOSトランジスタは第2の導通タイプであることを特徴とする。

(もっと読む)

差動増幅器

【課題】高周波増幅回路の小形化と回路設計の容易化を図ること。

【解決手段】トランジスタQ1のエミッタ端子に接続されたコンデンサC1の他端はアースされている。同様に、トランジスタQ2のエミッタ端子に接続されたコンデンサC2の他端はアースされている。コンデンサC1とC2の容量は勿論同じである。また、トランジスタQ1のコレクタ端子は、インダクタL1を介して直流電源に接続される。同様に、トランジスタQ2のコレクタ端子は、インダクタL2を介して直流電源に接続される。図示する符号Vccは、その直流電源の給電電位(>0)を示している。トランジスタQ1,Q2のエミッタ端子は、何れもインダクタL0の同一端に接続されており、このインダクタL0の他端は、定電流路y1を介してアースされている。コンデンサC1、C2とインダクタL0によって、本差動増幅器100の共振周波数帯域が制限される。

(もっと読む)

テレビ用受信機の受信増幅器、および、その使用方法

【課題】広い周波数範囲に亘って狭帯域システムの利点を有する受信増幅器を提示する。

【解決手段】受信増幅器が、接続接点6と接続接点7とを有する半導体基板2、および、増幅回路1を含んでいる。増幅回路1は、少なくとも1つの電界効果トランジスタと、第1入力部12と、第2入力部13とを備えている。増幅回路1の入力部同士の間には、容量素子Cinが配置されている。増幅回路の上流には、共振周波数が調整可能な同調回路が設けられている。この同調回路は、半導体基板2に集積された、可変容量素子CTを含み、増幅回路1の容量素子Cinに対して並列に接続されている。さらに、2つの誘導素子L1´、L1が設けられている。第1誘導素子L1´は、接続接点6に接続されており、第2誘導素子L1は、接続接点7に接続されている。これにより、共振周波数での電圧が高い直列同調回路が形成され、受信増幅器の入力信号の信号対雑音比が改善される。

(もっと読む)

電圧電流変換回路及びこれを用いた平衡型増幅器

【課題】入力電圧の同相成分を除去する電圧電流変換回路において、低電圧電源条件下でも出力信号振幅の限界が高い回路を提供する。

【解決手段】電圧電流変換回路Gm1、Gm2への入力電圧をV1、V2、入力電圧の差動成分を2Vin、同相成分をVcmとすると、V1=Vin+Vcm、V2=-Vin+Vcmとなる。Gm1、Gm2のin2、Out2の4端子を接続した線上の電位をVaとすると、出力電流はI1=-Gm(V1+Va)、I2=-Gm(V2+Va)とあらわされる。Gm1、Gm2の入力インピーダンスは非常に大きいので、帰還された電流はGm1、Gm2のどちらの逆相入力端子in2にも流れ込むことができないからI1+I2=0となる。すなはち、逆相入力端子in2には同相成分を相殺する帰還がかかり、出力電流からは同相成分が除去されていることがわかる。

(もっと読む)

差動増幅器、2段増幅器及びアナログ/ディジタル変換器

【課題】差動増幅器、アナログ/ディジタル変換器の帯域を広げること。

【解決手段】本発明では、差動増幅器を一対のコンパレータで構成し、各コンパレータは、サンプリングコンデンサの入力側に入力電圧信号と参照電圧信号とを第1、第2のスイッチング手段を介してそれぞれ印加する一方、サンプリングコンデンサの出力側に出力トランジスタをソースフォロワ接続するとともに、第3のスイッチング手段の一端をサンプリングコンデンサの出力側に接続する。さらに、各第3のスイッチング手段の他端に共通のスイッチングトランジスタを接続する。そして、第1及び第3のスイッチング手段とスイッチングトランジスタとを接続状態に、第2のスイッチング手段を切断状態にした後に、第1及び第3のスイッチング手段とスイッチングトランジスタとを切断状態に、第2のスイッチング手段を接続状態にし、入力電圧信号と参照電圧信号との比較を行う。

(もっと読む)

1 - 13 / 13

[ Back to top ]