Fターム[5J500DN14]の内容

増幅器一般 (93,357) | 増幅部構成 (1,575) | 負荷回路構成 (326) | 能動素子を用いるもの(能動負荷) (301) | ベース(ゲート)共通接続能動負荷 (94)

Fターム[5J500DN14]に分類される特許

1 - 20 / 94

半導体装置

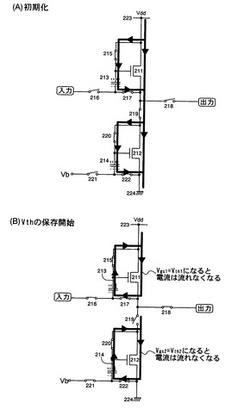

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

同相電圧帰還回路及び全差動演算増幅器

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

演算増幅器

【課題】所定のS/Nを維持しながら消費電流の増加を抑制することのできる演算増幅器を提供する。

【解決手段】実施形態の演算増幅器は、正相信号Vpと逆相信号Vmが入力される差動増幅回路100と、差動増幅回路100へ動作電流を供給するカレントミラー回路200とを有する。この演算増幅器は、入力信号電圧検出回路1が、正相信号Vpと逆相信号Vmとの間の電圧差を検出し、動作電流制御回路2が、その電圧差の大きさに応じた制御信号を出力する。この制御信号の制御により、可変定電流回路3が、カレントミラー回路200へ入力する定電流の大きさを変化させる。

(もっと読む)

半導体装置

【課題】消費電流を削減する。

【解決手段】第1及び第2の入力端子に現れる電位差を第1及び第2の電源に基づいて増幅する差動アンプ(図2のMN1、MN2が相当)と、差動アンプを動作させるバイアス電流を制御するバイアストランジスタ(図2のMN3が相当)と、差動アンプの負荷となるカレントミラー回路(図2のMP1、MP2が相当)と、カレントミラー回路のダイオード接続側と其々の制御端が接続されると共に第1及び第2の電源間に直列に接続される、バイアストランジスタと逆導電型の第1及び第2のトランジスタ(図2のMP4、MP6が相当)を有し、第1及び第2のトランジスタの間の接続ノードをバイアストランジスタの制御端に接続するバイアス制御回路と、を備える。

(もっと読む)

差動増幅回路及びコンパレータ

【課題】オフセット電圧の変動を低減した差動増幅回路及びコンパレータを提供する。

【解決手段】実施形態によれば、差動回路と、出力回路と、クリップ回路と、を備えたことを特徴とする差動増幅回路が提供される。前記差動回路は、一対の入力信号の電位差に応じた一対の差動電流を生成する。前記出力回路は、前記一対の差動電流を受けて、電流差に応じた出力電圧を生成する。前記クリップ回路は、前記出力電圧に応じてオンし、前記出力電圧をしきい値電圧を含みローレベルまたは前記ローレベルよりも高いハイレベルに変換できる範囲に抑制するクリップ素子を有する。

(もっと読む)

出力回路

【課題】より十分な出力電流を流せる出力回路を提供する。

【解決手段】PMOSトランジスタ12のドレイン電流が大きい場合、PMOSトランジスタ13は非飽和領域で動作する。このときNMOSトランジスタ14及び17のゲート電圧は電源端子電圧付近まで上昇している。このため、NMOSトランジスタ17のゲート・ソース間電圧は大きくなり、十分な出力電流が流れる。

(もっと読む)

電流源回路

【課題】回路面積が小さな電流源回路を提供する。

【解決手段】この電流源回路では、直流電圧V1に応じた値の参照電流I1を生成し、その電流I1のうちの電流IrをダイオードD1に流し、残りの電流I1−IrをダイオードD2に流し、ダイオードD1,D2のアノードの電圧VR1,VR2を差動増幅回路のトランジスタQ1,Q2のベースに与える。また、直流電圧V2に応じた値の参照電流I2を生成し、その電流I2を差動増幅回路の駆動電流とする。トランジスタQ1のコレクタに流れる定電流Io=Ir・(V2/V1)が電流源回路の出力電流Ioとなる。したがって、外付け用の端子および外部抵抗器が不要となる。

(もっと読む)

多入力差動増幅器

【課題】各動作モードにおいてレベルシフト回路を用いることなく所望の入力電圧範囲となる多入力差動増幅器を提供する。

【解決手段】差動部1は、バイアス部2と出力部3との間に設けられ、第一入力部10と第二入力部20とを有する。第一入力部10は、ソースがバイアス部2と接続され、ドレインが出力部3と接続された1個のn型MOSFET(M11)からなる。第二入力部20は、直列接続される2個のn型MOSFET(M21)、(M22)と、直列接続される2個のn型MOSFET(M23)、(M24)とが2列に並列接続される。また、入力端INaはM11のゲートに接続され、入力端INxはM22とM23のゲートに接続され、入力端INyはM21とM24のゲートに接続される。バイアス部2は1つの定電流源21を有し、出力部3は2つのp型MOSFET(Q1、Q2)で構成のカレントミラー回路を有する。

(もっと読む)

差動増幅器及びデータドライバ

【課題】従来の差動増幅器は出力誤差が増大する問題がある。

【解決手段】本発明の差動増幅器は、内挿機能を有し、第1導電型トランジスタで形成される第1、第2の差動対(21、22)と、第2導電型トランジスタで形成される第3、第4の差動対(23、24)と、第1、第2の差動対に動作電流を供給する第1、第2の電流源(41、42)と、第3、第4の差動対に動作電流を供給する第3、第4の電流源(43、44)と、第1、第2の差動対にそれぞれ流れる電流量が第1、第2の電流源が出力する動作電流よりも小さくなる第1の動作範囲において、第1の差動対に供給される動作電流の変化点を制御する第1の制御回路51と、第3、第4の差動対にそれぞれ流れる電流量が第3、第4の電流源が出力する動作電流よりも小さくなる第2の動作範囲において、第4の差動対に供給される動作電流の変化点を制御する第2の制御回路52と、を有する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力期間の切替時における出力信号の遅延発生を抑制する出力回路、データドライバと表示装置の提供。

【解決手段】出力回路は差動増幅回路110、105,出力増幅回路120と第1の制御回路160、入力端子101、出力端子104、第1乃至第3の電源端子VDD、VSS、VMLを備える。差動増幅回路は前記入力端子の入力信号と前記出力端子の出力信号を入力する差動入力段110と第1及び第2のカレントミラー130、140を備える。出力増幅回路120は第1の電源端子VDDと出力端子104との間に接続された第1導電型の第1のトランジスタ121と出力端子104と第3の電源端子VMLとの間に接続された第2導電型の第2のトランジスタ122とを備える。第1の制御回路160は、第1導電型の第3のトランジスタ161と第1のスイッチ162を備える。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

オペアンプ

【課題】出力電圧におけるひずみを低減すること。

【解決手段】制御回路27は、第1の差動対21と高電位電源VDとの間に接続されたトランジスタTP11に流れるバイアス電流ia1と等しい電流ia3を高電位電源VDとノードN13との間に生成する。また、制御回路27は、バイアス電圧VG1に応じた電流ib2をノードN13とグランドGNDとの間に生成する。ノードN13は、トランジスタTP13に接続され、電流源として動作するトランジスタTP12は、トランジスタTP13に流れる電流ia5と等しいバイアス電流ia2を第2の差動対22に供給する。そして、制御回路27は、入力電圧VPがゲートに供給されるトランジスタTN33により、ノードN13とグランドGNDとの間に流れる電流を制限する。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】出力信号遅延を抑制し、消費電流の増大を抑制する出力回路の提供。

【解決手段】入力端子101と出力端子102の電圧を差動入力する差動入力段110からなる差動増幅回路と、第1及び第2の電源端子VDD、VSSに接続された第1及び第2のカレントミラー130、140と、前記第1及び第2のカレントミラーの入力間、出力間に接続される第1、第2の連絡回路150L、150Rと、第1導電型の第1のトランジスタ121と第2導電型の第2のトランジスタ122とからなる出力増幅回路と、前記第1、第2の電源端子VDD、VSSの電源電圧の間の電圧が供給される第3の電源端子VMLの電圧に応じたバイアス信号を受ける第1導電型の第3のトランジスタ161からなる制御回路160と、を備えている。

(もっと読む)

オペレイショナル・トランスコンダクタンス・アンプ

【課題】MOSトランジスタのしきい値電圧の絶対値が低い場合でも優れた線形性能を確保しつつ、入力信号レベルを大きくすることができるオペレイショナル・トランスコンダクタンス・アンプを提供する。

【解決手段】信号が入力され、信号を出力するNMOSトランジスタ(以下、Tr)11、12、ドレインがTr11のソースに接続され、ゲートがTr12のソースに接続されるTr13、ドレインがTr12のソースに接続され、ゲートがTr11のソースに接続されるTr14、Tr13に電流を供給する電流源17、Tr14に電流を供給する電流源18、Tr13のソースとTr14のソースとの間に接続される抵抗素子19、Tr13、14に対し、それらトランジスタの動作点が飽和領域内の線形領域に近い側から遠い側に向かう方向にシフトするように電圧を印加する電圧源21、22によってOTAを構成する。

(もっと読む)

電源回路

【課題】比較的簡易な構成で、定電圧駆動と定電流駆動を所望に応じて選択可能な電源回路を提供する。

【解決手段】演算増幅器1の出力端子とグランドとの間に第1及び第2の抵抗器31,32が直列接続されて設けられ、演算増幅器1の非反転入力端子には、所定の基準電圧が印加され、演算増幅器1の出力端子には、外部からの信号により動作制御可能に構成されてなるバッファアンプ2が接続され、バッファアンプ2の出力端子とグランドとの間には、MOSトランジスタ11と第3の抵抗器33が順に直列接続されて設けられ、これらの接続が、切替制御回路4、及び、第1乃至第4のアナログスイッチ21〜24により切り替えられることで、定電圧駆動と定電流駆動が選択可能となっている。

(もっと読む)

差動増幅器

【課題】負荷側に出力を電流で受け渡すカレントミラー回路を備える差動増幅器の動作を高速化する。

【解決手段】差動増幅器を構成し、差動増幅器に対する2つの入力の内のそれぞれ1つが与えられる各トランジスタの端子の内で、差動増幅器の出力点となりうるそれぞれの端子の間に接続される回路素子を備える差動増幅器は、カレントミラー回路においてモニタ電流が流れるトランジスタに接続されるとともに、カレントミラー回路においてコピー電流が流れる第1のトランジスタと、前記出力が受け渡される負荷としての抵抗との間に接続される前記2つの入力のうちいずれか1つが与えられるトランジスタへの入力がLの時にオフとなる第2のトランジスタと、第1のトランジスタと第2のトランジスタとの接続点とアースとの間に接続される電流源とをさらに備えることにより、上記課題の解決を図る。

(もっと読む)

差動増幅回路及びA/D変換器

【課題】電源電圧が比較的小さい場合においても、性能劣化を起こさず、かつオーバードライブリカバリ可能な差動増幅回路を得る。

【解決手段】第1の出力部であるノードN1と電源Vddとの間にPMOSトランジスタMP1及びMP3が互いに並列に介挿され、第2の出力部であるノードN2と電源Vddとの間にPMOSトランジスタMP2及びMP4が互いに並列に介挿される。レプリカ回路4及びコンパレータ5によって、入力電圧Vinと基準電圧Vrefとの入力電位差が“0”のバランス状態時の出力電圧Voutp及びVoutnは共に基準出力コモン電圧Voutcm_idealに設定される。電源電圧Vddと出力コモン電圧Voutcmとの電位差がダイオード接続されたPMOSトランジスタMP1及びMP2の閾値電圧Vthよりも低い値となるように、レプリカ回路4の基準出力コモン電圧Voutcm_idealを設定する。

(もっと読む)

オペアンプ及びこれを用いた液晶駆動装置、並びに、パラメータ設定回路、半導体装置、電源装置

【課題】定常消費電流を大きくせずスルーレートを高速化したオペアンプを提供し、また、外部端子数を増大せず、閾値電圧などのパラメータを任意に設定することが可能なパラメータ設定回路、並びに、これを備えた半導体装置、電源装置を提供する。

【解決手段】オペアンプは、一対のトランジスタから成る差動対を用いて正相入力信号と逆相入力信号との電位差に応じた電圧信号を生成する少なくとも一の差動入力部10、20と、前記差動入力部で生成される前記電圧信号に応じた論理レベルの出力信号を生成して出力する出力部30と、前記正相入力信号または前記逆相入力信号が急峻に変動したことを検出して補助電流Id1、Id2を生成する少なくとも一の補助電流生成部40、50と、所定の基準電流Id0と前記補助電流Id1、Id2とを足し合わせて前記差動入力部の駆動電流Idを生成する駆動電流生成部60と、を有する。

(もっと読む)

演算増幅器、並びに、それを用いた表示パネルドライバ及び表示装置

【課題】出力端子の電位の変動が位相補償キャパシタを介して出力トランジスタのゲートの電位を変動させることによる貫通電流の発生を防ぐ。

【解決手段】演算増幅器1が、出力PMOSトランジスタMP6と、出力NMOSトランジスタMN6と、ノードN1と出力端子Voutの間に接続された位相補償キャパシタC1と、ノードN2と出力端子Voutの間に接続された位相補償キャパシタC2と、浮遊電流源6を構成しているPMOSトランジスタMP5A及びNMOSトランジスタMN5Aと、ノードN1と浮遊電流源6の間に接続されたPMOSトランジスタMP5Bと、浮遊電流源6とノードN2の間に接続されたNMOSトランジスタMN5Bとを備えている。PMOSトランジスタMP5A、MP5Bのゲートは共通に接続され、NMOSトランジスタMN5A、MN5Bのゲートは共通に接続されている。

(もっと読む)

差動入力段回路、差動入力段回路を備えた演算増幅器及び電圧レギュレータ回路

【課題】出力インピーダンスが大きい信号源を接続した場合でも大きなバイパスコンデンサを必要とせず、かつ電源電圧変動除去特性の良い差動入力段回路を提供する。

【解決手段】差動入力段回路を、差動入力部を構成し、ソースが結合されたトランジスタM1,M2と、トランジスタM1,M2とグランドとの間に接続された定電流源Icと、カレントミラー段を構成し、ソースが電源に接続されたトランジスタM3,M4と、トランジスタM3のドレーンにドレーンが接続され、トランジスタのドレーンにソースが接続され、ゲートが基準電圧源Vbiasに接続された、トランジスタM1と同一の導電型のトランジスタM5と、トランジスタM4のドレーンにドレーンが接続され、トランジスタM2のドレーンにソースが接続され、ゲートが基準電圧源Vbiasに接続された、トランジスタM2と同一の導電型のトランジスタM6と、で構成する。

(もっと読む)

1 - 20 / 94

[ Back to top ]