Fターム[5J500DN21]の内容

Fターム[5J500DN21]の下位に属するFターム

エミッタ(ソース)直結構成 (199)

定電流源を具備するもの (401)

エミッタ(ソース)帰還抵抗を具備するもの (43)

エミッタ(ソース)間にパスコンを備えるもの (3)

エミッタ(ソース)電流可変回路 (18)

Fターム[5J500DN21]に分類される特許

1 - 7 / 7

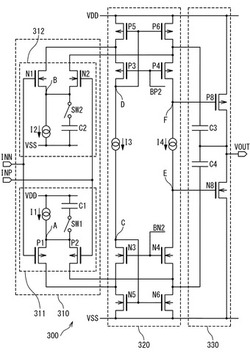

演算増幅回路、液晶パネル駆動装置

【課題】演算増幅回路を安定に動作させつつスルーレートを向上させる。

【解決手段】第1差動増幅部(311)は、P型差動対(P1/P2)のソースと正側電源電圧(VDD)との間に、並列に接続される第1電流源(I1)と第1容量(C1)とを備え、P型差動対(P1/P2)のソースと第1容量(C1)との間に挿入される第1スイッチ(SW1)をさらに備える。第2差動増幅部(312)は、N型差動対(N1/N2)のソースと負側電源電圧(VSS)との間に、並列に接続される第2電流源(I2)と第2容量(C2)とを備え、N型差動対(N1/N2)のソースと第2容量(C2)との間に挿入される第2スイッチ(SW2)をさらに備える。第1スイッチ(SW1)と第2スイッチ(SW2)とは、第1差動増幅部(311)および第2差動増幅部(312)に入力される入力差動信号に同期して交互に回路を開閉する。

(もっと読む)

オペレイショナル・トランスコンダクタンス・アンプ、オペレイショナル・トランスコンダクタンス・アンプを用いたフィルタ回路

【課題】入力電圧範囲を広くしても線形性能の優れ、かつトランスコンダクタンス値精度の優れたOTA、OTAを用いたフィルタ回路を提供する。

【解決手段】I−V変換器と、内部抵抗素子の抵抗値に比例する増幅率でI−V変換器の出力電流を増幅する電流制御回路1、2とによってOTAを構成する。そして、電流制御回路1、2を、入力電流が入力されるドレイン、第1制御電圧が供給されるゲートを有するMOSトランジスタ10、出力電流が出力されるドレインを有するMOSトランジスタ13、第2制御電圧が供給されるゲートを有するMOSトランジスタ11、MOSトランジスタ10のドレインと接続される非反転入力端子、MOSトランジスタ13のゲートと接続される出力端子、MOSトランジスタ13のソース及びMOSトランジスタ11のドレインと接続される反転入力端子を有する差動増幅器12によって構成する。

(もっと読む)

多段差動増幅器

【課題】高出力増幅器のような高飽和特性が要求される差動増幅器において、入力信号の同相成分を除去する機能を改善し、差動利得特性の劣化を防止する。

【解決手段】半導体増幅素子から構成されるエミッタ接地形多段差動増幅器において、少なくとも最前段増幅器の入力バイアス回路には該増幅器を構成する半導体増幅素子の入力インピーダンスの絶対値の1/2以上のインピーダンスを有するフィード素子を用いる。

(もっと読む)

電源補償電圧および電流源

【課題】電源補償電圧または電流を供給する装置および方法を提供する。

【解決手段】電源補償電流および電圧源は、バンドギャップ基準電圧およびスケールされた電源電圧に接続された差動増幅器106を利用する。電源が変動すると、差動増幅器が安定した補償出力を調整する。出力は補償電圧でも電流でもよい。さらに、差動増幅器から複数の電流および電圧が参照されてもよい。安定した補償出力は、外部回路のための基準バイアスとして供給されてもよい。さらに、補償出力は、電圧制御発振器に供給されてもよい。電源補償電圧および電流源は、電源電圧が第1および第2の抵抗器102に跨って分配される、基準ノード122で第2の抵抗器と直列に接続された第1の抵抗器と、電圧基準電源104と、第1および第2の電圧入力および補償出力を有し、前記第1の入力が前記基準ノードに接続され、前記第2の入力が前記電圧基準電源に接続される差動増幅器と、を備える。

(もっと読む)

電圧電流変換回路及びこれを用いた平衡型増幅器

【課題】入力電圧の同相成分を除去する電圧電流変換回路において、低電圧電源条件下でも出力信号振幅の限界が高い回路を提供する。

【解決手段】電圧電流変換回路Gm1、Gm2への入力電圧をV1、V2、入力電圧の差動成分を2Vin、同相成分をVcmとすると、V1=Vin+Vcm、V2=-Vin+Vcmとなる。Gm1、Gm2のin2、Out2の4端子を接続した線上の電位をVaとすると、出力電流はI1=-Gm(V1+Va)、I2=-Gm(V2+Va)とあらわされる。Gm1、Gm2の入力インピーダンスは非常に大きいので、帰還された電流はGm1、Gm2のどちらの逆相入力端子in2にも流れ込むことができないからI1+I2=0となる。すなはち、逆相入力端子in2には同相成分を相殺する帰還がかかり、出力電流からは同相成分が除去されていることがわかる。

(もっと読む)

差動増幅器、2段増幅器及びアナログ/ディジタル変換器

【課題】差動増幅器、アナログ/ディジタル変換器の帯域を広げること。

【解決手段】本発明では、差動増幅器を一対のコンパレータで構成し、各コンパレータは、サンプリングコンデンサの入力側に入力電圧信号と参照電圧信号とを第1、第2のスイッチング手段を介してそれぞれ印加する一方、サンプリングコンデンサの出力側に出力トランジスタをソースフォロワ接続するとともに、第3のスイッチング手段の一端をサンプリングコンデンサの出力側に接続する。さらに、各第3のスイッチング手段の他端に共通のスイッチングトランジスタを接続する。そして、第1及び第3のスイッチング手段とスイッチングトランジスタとを接続状態に、第2のスイッチング手段を切断状態にした後に、第1及び第3のスイッチング手段とスイッチングトランジスタとを切断状態に、第2のスイッチング手段を接続状態にし、入力電圧信号と参照電圧信号との比較を行う。

(もっと読む)

増幅回路、半導体集積回路及び電子機器

【課題】本発明は、容量結合のためのコンデンサを内部に搭載しても低域カットオフ周波数を十分に低くすることができる増幅回路、半導体集積回路及び電子機器を提供することを目的とする。

【解決手段】第1のコンデンサを介して入力される信号を増幅器により増幅する増幅回路において、第2のコンデンサを介して前記信号を入力し、抵抗を介して前記増幅器へ出力するエミッタフォロア回路を設け、しかも、エミッタフォロア回路の増幅素子としてMOSFETを採用したので、増幅回路に形成されるハイパスフィルタのカットオフ周波数を大幅に下がる。

(もっと読む)

1 - 7 / 7

[ Back to top ]