Fターム[5J500DN24]の内容

増幅器一般 (93,357) | 増幅部構成 (1,575) | エミッタ(ソース)回路構成 (671) | 定電流源を具備するもの (401) | 定電流源がカレントミラー構成 (85)

Fターム[5J500DN24]に分類される特許

1 - 20 / 85

同相電圧帰還回路及び全差動演算増幅器

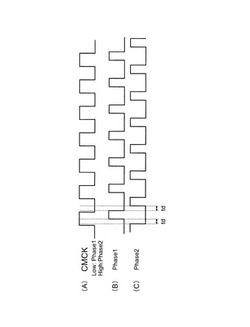

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

差動増幅回路及び集積回路装置

【課題】差動対を構成する2つのPMOSトランジスターにおけるNBTIの発生を可能な限り防ぐことにより出力オフセット電圧の発生を抑制可能な差動増幅回路及び集積回路装置を提供すること。

【解決手段】差動増幅回路1は、第1の信号が入力されるPMOSトランジスター10(第1のPMOSトランジスターの一例)と、第2の信号が入力されるPMOSトランジスター20(第2のPMOSトランジスターの一例)と、制御信号XSTBに基づいて、PMOSトランジスター10のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター14(第1のスイッチ部の一例)と、制御信号XSTBに基づいて、PMOSトランジスター20のゲートとバックゲートを同電位にするか否かを選択するPMOSトランジスター24(第2のスイッチ部の一例)と、を含む。

(もっと読む)

受信回路並びにそれを備えた半導体装置及び情報処理システム

【課題】 本発明は、低速信号よりも高速信号を増幅し、かつ、消費電力を抑える受信回路並びにそれを備えた半導体装置及び情報処理システムを実現することを目的とする。

【解決手段】 本発明の受信回路並びにそれを備えた半導体装置及び情報処理システムは、第1の増幅器と、第1の増幅器よりもカットオフ周波数の低い第2の増幅器とを有し、第1の増幅器及び第2の増幅器に受信信号を入力し、第1の増幅器の出力から第2の増幅器の出力を減じて出力する。

(もっと読む)

電流源回路

【課題】回路面積が小さな電流源回路を提供する。

【解決手段】この電流源回路では、直流電圧V1に応じた値の参照電流I1を生成し、その電流I1のうちの電流IrをダイオードD1に流し、残りの電流I1−IrをダイオードD2に流し、ダイオードD1,D2のアノードの電圧VR1,VR2を差動増幅回路のトランジスタQ1,Q2のベースに与える。また、直流電圧V2に応じた値の参照電流I2を生成し、その電流I2を差動増幅回路の駆動電流とする。トランジスタQ1のコレクタに流れる定電流Io=Ir・(V2/V1)が電流源回路の出力電流Ioとなる。したがって、外付け用の端子および外部抵抗器が不要となる。

(もっと読む)

差動増幅回路および液晶表示装置

【課題】消費電流を増加させずにスルーレートを向上する差動増幅回路、表示用駆動回路を提供する。

【解決手段】差動増幅回路は、差動信号を入力する入力段と、入力段の出力に基づいて容量性負荷を駆動する出力段とを具備する。入力段は、差動信号を入力する差動信号入力部(MN1/MN2、MN11/MN12/MP21/MP22)と、差動入力部にバイアス電流を供給する電流源(MN3、MN10/MP20)と、電流源(MN3、MN10/MP20)に並列に挿入される可変容量(Cs)を含むスルーレート調整部(414、415)とを備える。

(もっと読む)

回路ユニット、回路ユニットを有するバイアス回路、並びに第1及び第2の回路ユニットを有する差動増幅回路

ヘテロ接合バイポーラトランジスタ及びロングゲート疑似格子整合高電子移動度トランジスタを備える回路ユニット(CU)。前記ロングゲート疑似格子整合高電子移動度トランジスタのソース(S)又はドレイン(D)が、前記ヘテロ接合バイポーラトランジスタのコレクタ(C)又はエミッタ(E)に電気的に結合される。 (もっと読む)

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

オペアンプ

【課題】新規なオペアンプの回路を示す。

【解決手段】オペアンプの、負の入力端子と出力端子の間に、直列にRc1とRc2を、Rc1とRc2の間のノードと正の入力端子の間にCc1を、正の入力端子とグラウンド端子の間に位相補償容量Cc2を、つないだことを特徴とするオペアンプ回路を示す。容量値、抵抗値はいずれも使用プロセスにおける、チップ面積の極端な増大につながらない範囲内の値で設定できる。また設計後に事後的に容量、容量と抵抗を追加でき、チップ外部に接続することも出来る。

(もっと読む)

オペアンプ

【課題】プロセスばらつきによる影響を低減して動作が不安定になることを抑制することのできるオペアンプを提供する。

【解決手段】オペアンプは、電流源として動作するトランジスタTr2と、差動対11と、カレントミラー回路12とを含む第1差動増幅回路10と、差動対21と、電流源22と、カレントミラー回路23とを含む第2差動増幅回路20とを備える。差動対21のトランジスタTr11のゲートに供給されるトランジスタTr3,Tr5のドレイン電圧(ノードN1の電圧)を、電流源22であるトランジスタTr15,Tr16のゲートに供給する。

(もっと読む)

半導体集積回路

【課題】電源ノイズ耐性の優れ、かつ低消費電流でかつ多段接続が可能な増幅回路を実現する。

【解決手段】第1の電位変換用トランジスタ対(MN1,MN2)および第2のプリチャージトランジスタ対(MP3,MP4)を用いて電流/電圧変換用の容量素子(CL1,CL2)の対向電圧をそれぞれ第1の電源(VDD)レベルおよび第2の電源(VSS)レベルにプリチャージする。このプリチャージ完了後、第1の電源から差動トランジスタ対(MP1,MP2)を介して定電流を入力信号(VIP,VIN)に応じて振り分けて容量素子に供給する。この容量素子への電流供給停止後、第1のトランジスタ対(MN1,MN2)をオン状態、第2のトランジスタ対(MP3,MP4)をオフ状態に設定し、出力ノード(2a,2b)の電圧のレベルシフトをして、出力信号(VON,VOP)を生成する。

(もっと読む)

レシーバ回路

【課題】簡易な回路構成であり、かつ、レールツーレール入力の小振幅差動信号を受信して、低消費電力、低ゆがみ、高速に増幅出力することができ、電圧が異なる複数の電源が存在する系においても使用することができるレシーバ回路を提供する。

【解決手段】NMOS/PMOSの差動回路を有し、それぞれの差動回路により、レールツーレールの小振幅差動入力信号を受け取ってIO系電源のレールツーレールの差動出力信号を生成する差動増幅回路と、差動出力信号の同相入力電圧レベルに応じて、差動回路のテールカレントを補償する電流補償ミラー回路と、差動増幅回路によって生成されたIO系電源のレールツーレールの差動出力信号を、コア系電源のレールツーレールの差動信号にレベルシフトして出力するレベルシフタとを備えている。

(もっと読む)

プロセス変動に対してスルーレートを補償するためのプリドライバを有する出力バッファ

【課題】補償回路とプリドライバを組み込んでおり、プロセス変動に対して補償されるスルーレートを有する出力バッファを提供する。

【解決手段】補償回路370は、演算増幅器250と、増幅器の出力に結合されたゲートを有する第2のNFET240、第3のNFET371、及び実行抵抗381から構成される。出力バッファ300は、ICチップのコア150がプリドライバ310に制御信号をアサートする。これに応答して、プリドライバ310は、第1のNFET320にバッファリングされた制御信号をアサートし、第1のNFET320をオンにし、VSSレベルの出力信号をパット230にアサートする。

(もっと読む)

演算増幅器

【目的】位相変動を抑制させて安定した動作が可能な演算増幅器を提供することを目的とする。

【構成】第1及び第2入力信号各々に対応した電流を送出する入力段に対して電流を供給する第1トランジスタ、及び、入力段から送出された電流に応じた電位レベルを有する出力信号を生成する出力段に対して電流を供給する第2トランジスタに、夫々バイアス電圧を供給するにあたり、第1トランジスタにバイアス電圧を供給する為の配線と、第2トランジスタにバイアス電圧を供給する為の配線とを互いに電気的に絶縁する。

(もっと読む)

オペアンプ及び表示パネルの駆動装置

【課題】回路のレイアウト面積を小さくすることができるオペアンプ及び表示パネルの駆動装置を提供する。

【解決手段】ソースアンプ121は、差動回路300、カレントミラー回路210、出力回路212を含んで構成されている。差動回路300は、高耐圧のNMOSトランジスタN11A、N11Bがカレントミラー回路210と並列接続された差動対N11と、NMOSトランジスタN13と、を含んで構成されている。シンクアンプは、差動回路302、カレントミラー回路216、及び出力回路218を含んで構成されている。差動回路302は、高耐圧のPMOSトランジスタP12A、P12Bがカレントミラー回路216と並列接続された差動対P12と、PMOSトランジスタP15と、を含んで構成されている。

(もっと読む)

低周波透過回路、通信回路、通信方法、通信回路のレイアウト方法

【課題】透過周波数域における利得が一定かつ遮断周波数域への遷移における利得変化が急峻であって、かつ、帯域外抑圧比の大きい低周波透過回路を提供すること。

【解決手段】本発明の一態様は、インダクタ素子を有する低周波透過フィルタ101と、低周波透過フィルタ101に縦続接続され、低周波透過フィルタ101が透過から遮断へ遷移する周波数近傍かつ透過周波数域内に利得の盛り上がりを有する増幅器100と、を備える低周波透過回路である。

(もっと読む)

コンパレータ回路

【課題】フォールデッドカスコード接続の差動増幅段を有するコンパレータにおいて、オフセットの温度依存性を減らし検出精度を向上させる。

【解決手段】ソース共通接続された一対の差動MOSトランジスタを有する差動入力段(11)と、差動MOSトランジスタのドレイン端子にフォールデッドカスコード接続されたカスコード段(12)と、差動入力段とカスコード段に共通に接続された電流回路(Mn11〜Mn13,Mn21〜Mn23)と、カスコード段の出力ノードに接続された出力段(13)とを備えたコンパレータ回路において、前記電流回路は、カスコード段のMOSトランジスタのキャリア移動度の温度特性に起因する動作点の変動をキャンセルするような温度特性を付与された電流を流すように構成した。

(もっと読む)

差動増幅回路及びそれを用いた電源回路

【課題】オフセットが少なく、低ノイズの差動増幅回路及び電源回路を提供する。

【解決手段】本発明にかかる差動増幅回路は、反転入力端子IN−及び非反転入力端子IN+から入力される差動電圧を第1及び第2の電流I1、I2に変換する入力変換回路101と、第1の電流I1に対応する第3の電流I3と第2の電流I2との間で演算を行い、第4の電流I4を得る出力演算回路103と、反転入力端子IN−及び非反転入力端子IN+を同電位とするスイッチSW1と、反転入力端子IN−及び非反転入力端子IN+が同電位となった場合に出力演算回路103が第2及び第3の電流I2、I3間で演算を行ったときの電位を保持する容量Coffと、出力演算回路103から入力される第4の電流I4を外部に出力する出力バッファ回路104と、出力演算回路103から入力される第4の電流I4を記憶する容量Cbとを備える。

(もっと読む)

差動増幅器

【課題】トランジスタの製造ばらつき等があっても、低電源電圧で動作し、広範囲の入力電圧に対してプッシュプル動作の出力電流が得られる差動増幅器を提供する。

【解決手段】差動増幅器1は、第1の導電型のトランジスタで構成され、入力信号を受けて第1の差動電流I11、I12を出力する第1の差動対10と、第1の差動電流I11、I12に基づき、第1の吐き出し側出力電流I18及び第1の吸い込み側出力電流I16をそれぞれ第1の出力端子OP及び第2の出力端子ONに対して出力する第1の電流増幅部11と、第2の導電型のトランジスタで構成され、入力信号を受けて第2の差動電流I1C、I1Dを出力する第2の差動対20と、第2の差動電流I1C、I1Dに基づき、第2の吐き出し側出力電流I1K及び第2の吸い込み側出力電流I1Iをそれぞれ第1の出力端子OP及び第2の出力端子ONに対して出力する第2の電流増幅部21と、を有する。

(もっと読む)

オペアンプ位相補償回路及び位相補償方法

【課題】新規なオペアンプの位相補償回路及び位相補償方法を示す。

【解決手段】オペアンプの正の入力端子と、出力端子の間に、容量、または容量と抵抗を直列に接続することで、位相補償を行い、安定した動作のできるオペアンプ回路を示す。容量値、抵抗値はいずれも使用プロセスにおける、チップ面積の極端な増大につながらない範囲内の値で設定できる。また設計後に事後的に容量、容量と抵抗を追加でき、チップ外部に接続することも出来る。

(もっと読む)

1 - 20 / 85

[ Back to top ]