Fターム[5J500DP02]の内容

Fターム[5J500DP02]に分類される特許

1 - 20 / 395

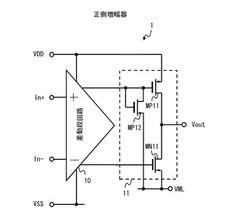

正帰還増幅器およびインターポレーション回路

全差動型帰還増幅回路および電気機器

制御回路および位相変調器

出力回路及びそれを備えた増幅器

【課題】出力波形に付加される遅延の増大を抑制することが可能な出力回路を提供すること。

【解決手段】本発明にかかる出力回路は、高電位側電源端子と外部出力端子Voutとの間に設けられ、電源電圧VDD〜接地電圧VSS間の電圧範囲を振幅する一対の増幅信号の一方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMP11と、低電位側電源端子と外部出力端子Voutとの間に設けられ、一対の増幅信号の他方に基づいてソース−ドレイン間に流れる電流が制御される出力トランジスタMN11と、電源電圧VDDより低く接地電圧VSSより高い中間電圧VMLが供給されている低電位側電源端子と、出力トランジスタMP11のゲートと、の間に設けられ、出力トランジスタMP11のゲート電圧と中間電圧VMLとの電圧差に基づいて出力トランジスタMP11のゲートをクランプするクランプ用トランジスタMP12と、を備える。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

【課題】差動入力を有する直交出力低雑音トランスコンダクタンス増幅器を提供する。

【解決手段】低雑音トランスコンダクタンス増幅器200は、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部110と、PMOSトランスコンダクタンス部に結合されたPMOSカスコード部130と、RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部120と、NMOSトランスコンダクタンス部に結合されたNMOSカスコード部140と、を含み、PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号gmpq、gmnq及び差動同相出力信号gmpi、gmniを提供する。RF信号を増幅するための方法は、差動RF入力信号を受信することと、差動RF入力信号を電流信号に変換することと、電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供する。

(もっと読む)

可変調整精度を有する増幅器回路

【課題】 増幅器回路の可変精度の調整を実現するシステム及び方法を提供する。

【解決手段】 本開示の一態様によると、システムは、増幅器の利得を離散的な利得レベルに設定する複数の調整段を有する増幅器を有する。特定の実施形態では、調整段は直列に接続され、調整段の各々は、スイッチに並列に接続された抵抗器を有し、該スイッチはオフにされ、増幅器に利得を隣接する利得レベルに設定させる。特定の実施形態では、複数の利得レベルのうちの隣接する各々間の利得の差は、低い利得レベルより高い利得レベルにおいて大きい。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

全差動増幅器

【課題】初期動作を安定させるスタートアップ回路を備え、消費電力を低減すると共に、回路規模の増加を抑制した全差動増幅器を提供する。

【解決手段】図1に示す全差動増幅器は、入力信号を受け付ける差動対を含み、差動信号を出力する差動増幅器と、差動信号を増幅し、差動出力信号から出力コモンモード電圧を生成する出力コモンモード電圧生成回路と、出力コモンモード電圧と所定の基準電圧を比較することでコモンモードフィードバック信号を生成し、コモンモードフィードバック信号を差動増幅器にフィードバックすることで、出力コモンモード電圧と基準電圧を実質的に一致させるコモンモードフィードバック回路と、入力信号に基づいて、差動信号を略電源電圧にプルアップ又は略接地電圧にプルダウンするスタートアップ回路と、を備える。

(もっと読む)

電力分配回路

【課題】差動入力信号を入力し1対の差動出力信号を出力する際、差動出力信号間の回路誤差を低減する。

【解決手段】電力分配回路10はトランス2A、2B及び加算回路3を含む構成である。トランス2Aの出力信号は、正相信号(Vout2Ap)の位相θ1+90°、逆相信号(Vout2An)の位相θ1−90°の差動信号として出力される。トランス2Bの出力信号は、正相信号(Vout2Bp)の位相θ2+90°、逆相信号(Vout2Bn)の位相θ2−90°の差動信号として出力される。加算回路3は、トランス2A,2Bからの2対の差動信号を、正相信号及び逆相信号毎にベクトル加算し、1対の差動出力信号に合成する。差動出力信号は、トランス2A,2Bにおいて生じた位相誤差(θ1−θ2)が補正された信号として得られる。

(もっと読む)

差動トランスインピーダンス増幅器

【課題】同相入力電流成分に対する耐性を大きくする。

【解決手段】差動トランスインピーダンス増幅器は、入力信号合成回路12で得られた、入力端子IT,ICのそれぞれの信号を合成した同相入力電圧と、出力信号合成回路15で得られた、出力端子OT,OCのそれぞれの信号を合成した参照電圧との差電圧に応じた制御信号を制御用増幅器13で生成し、可変電流源IS1,IS2で、この制御信号に応じた量の電流を入力電流信号から引き抜く。入力信号合成回路12は、抵抗R31〜R33と、容量C31とから構成される。出力信号合成回路15は、抵抗R41〜R43と、容量C41とから構成される。

(もっと読む)

完全差動型オペアンプ

【課題】完全差動型オペアンプの動作の安定度を向上し、高速動作を可能にする。

【解決手段】差動増幅部は、第1ステージの第1の差動増幅回路と、第2ステージの第2の差動増幅回路2から構成される。位相補償回路5は、第2の差動増幅回路2の差動入力端子と差動出力端子との間に接続されている。第1のCMFB回路3は、第1ステージの差動増幅回路1の差動出力電圧VP,VNの第1の同相電圧VC1が第1の基準電圧になるように、第1の差動増幅回路1をフィードバック制御する。第2のCMFB回路4は、第2の差動増幅回路2の差動出力電圧VOUTP,VOUTNの第2の同相電圧VC2が第2の基準電圧になるように、第2の差動増幅回路2をフィードバック制御する。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

半導体装置

【課題】シングルエンド−差動変換器を備えた半導体装置において、理想的な出力差動電流特性が得られる周波数の上限を向上させる。

【解決手段】入力電圧Vinを、パッケージ3の外部電極PIN1に入力し、外部電極PIN1、ボンディングワイヤWire1、チップ2の入力端子PAD1、シングルエンド−差動変換器1の入力端子Tin1を介してゲート接地のMOSトランジスタM1のソースに伝達する。また、外部電極PIN1、ボンディングワイヤWire2、チップ2の入力端子PAD2、シングルエンド−差動変換器1の入力端子Tin2を介してソース接地のMOSトランジスタM2のゲートに伝達する。

(もっと読む)

ソースフォロア回路

【課題】雑音特性を改善したソースフォロア回路を提供すること。

【解決手段】このソースフォロア回路は、電界効果型トランジスタ(M1,M2)によって構成されるソースフォロア回路部と、電界効果型トランジスタ(M3,M4,M5)によって構成されるカレントミラー回路部と、を備える。電界効果型トランジスタ(M4,M5)のゲートにクロスカップルに容量(C1,C2)を接続することにより、カレントミラー回路部をアンプとして機能させる。

(もっと読む)

電子回路及び光受光回路

【課題】 入出力信号のオフセットを補償して、入力電流が増大しても増幅動作を行うことができる電子回路及び光受光回路を提供する。

【解決手段】 本発明の電子回路30は、相補的な入力電流を、相補的な電圧信号に変換して出力する差動トランスインピーダンスアンプ10と、出力を入力し、出力が差動トランスインピーダンスアンプ10の入力に接続される差動回路18であって、差動回路18の電流源Is5が入力電流の平均値I2に基づいて制御される差動回路18と、を備えることを特徴とする。

(もっと読む)

差動増幅回路

【課題】基本波周波数のゲイン変化を生じさせることなく、2次高調波のみを抑圧および低減した回路面積の小さい差動増幅回路の実現。

【解決手段】差動対をなし、差動信号S,ZSが入力される2個のMOSトランジスタTr1,Tr2と、2個のMOSトランジスタTr1,Tr2のドレイン間に直列に接続された2個の容量素子C1,C2と、2個の容量素子C1,C2の接続ノードとバイアス電源端子GND間に接続されたインダクタンス素子L1と、を有する差動増幅回路。

(もっと読む)

差動増幅回路

【課題】チップ面積を小さくする。

【解決手段】一端がグランド端子14に接続される定電流源13と、ソースが共通に定電流源13の他端に接続され、ゲートが入力端子A、Bにそれぞれ接続される第1および第2の差動対(Q11、Q12およびQ13、Q14に相当)と、第1の差動対のそれぞれのドレインにそれぞれのソースを接続するnMOSトランジスタQ15、Q16と、nMOSトランジスタQ15、Q16のそれぞれのドレインを出力端子C、Dとし、出力端子C、Dと電源端子11との間に接続される負荷部(図1のQ17、Q18に相当)と、を備え、第1の差動対のそれぞれのドレインを第2の差動対の逆相となるそれぞれのドレインに接続し、nMOSトランジスタQ15、Q16のそれぞれのゲートは、nMOSトランジスタQ15、Q16のドレインにそれぞれ接続する。

(もっと読む)

オフセット調整差動増幅回路

【課題】オフセット調整差動増幅回路において、オフセット調整値を温度に対して安定して維持することを提供する。

【解決手段】オフセット調整差動増幅回路は、差動対を構成する第1、第2のMOSトランジスタM1、M2と、第1のMOSトランジスタM1のソースに一端が接続される第1の抵抗R1と、第2のMOSトランジスタM2のソースに一端が接続され、第1の抵抗R1の他端に他端が接続される第2の抵抗R2と、第1、第2の抵抗R1、R2の接続点と第1の電源端子との間に接続され、差動対の動作電流を供給する電流源M6と、第1のMOSトランジスタM1のソースにソースが接続され、第2の電源端子にドレインが接続され、ゲートにオフセット調整電圧VTが与えられ、第1の抵抗R1の両端に生じる電圧を調節するオフセット調整電流I7をオフセット調整電圧VTに応じて制御する第3のMOSトランジスタM7と、を有する。

(もっと読む)

増幅回路

【課題】動作電流を減少させることが可能となり、低消費電力化が可能となる増幅回路の提供。

【解決手段】この発明は、差動対を構成し、互いに逆相の差動入力信号vipx、vinxが入力されるMOSトランジスM1、M2と、MOSトランジスタM1、M2のそれぞれの負荷となるMOSトランジスタM3、M4とを備えている。また、MOSトランジスタM3のバルクには、抵抗R5を介してバイアス電圧が印加されるととともに、キャパシタC3を介して反転出力信号vonが入力される。さらに、MOSトランジスタM4のバルクには、抵抗R6を介してバイアス電圧が印加されるととともに、キャパシタC4を介して出力信号vopが入力される。

(もっと読む)

1 - 20 / 395

[ Back to top ]