Fターム[5J500DP03]の内容

Fターム[5J500DP03]に分類される特許

1 - 20 / 59

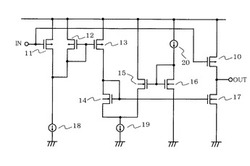

出力回路

【課題】より十分な出力電流を流せる出力回路を提供する。

【解決手段】PMOSトランジスタ12のドレイン電流が大きい場合、PMOSトランジスタ13は非飽和領域で動作する。このときNMOSトランジスタ14及び17のゲート電圧は電源端子電圧付近まで上昇している。このため、NMOSトランジスタ17のゲート・ソース間電圧は大きくなり、十分な出力電流が流れる。

(もっと読む)

送信装置および送受信システム

【課題】受信装置の終端抵抗器の抵抗値がばらついている場合であっても安定した通信を行うことができる送信装置を提供する。

【解決手段】送信装置10Aは、第1トランジスタ11、第2トランジスタ12、電流源13、送信回路14、差演算部15および電流調整部16を備える。トランジスタ11,12は差動対を構成している。差演算部15は、トランジスタ11,12のうちの一方がオン状態で他方がオフ状態であるときの第1出力端10aおよび第2出力端10bそれぞれからの出力電圧値を入力して、これら2つの出力電圧値の差(対象電圧)を求める。電流調整部16は、この対象電圧を入力するとともに、参照電圧入力端10dに入力された参照電圧を入力して、参照電圧に基づいて対象電圧を評価し、その評価結果に基づいて、対象電圧が目標値または目標範囲内となるように電流源13の出力電流値を調整する。

(もっと読む)

電源回路

【課題】比較的簡易な構成で、定電圧駆動と定電流駆動を所望に応じて選択可能な電源回路を提供する。

【解決手段】演算増幅器1の出力端子とグランドとの間に第1及び第2の抵抗器31,32が直列接続されて設けられ、演算増幅器1の非反転入力端子には、所定の基準電圧が印加され、演算増幅器1の出力端子には、外部からの信号により動作制御可能に構成されてなるバッファアンプ2が接続され、バッファアンプ2の出力端子とグランドとの間には、MOSトランジスタ11と第3の抵抗器33が順に直列接続されて設けられ、これらの接続が、切替制御回路4、及び、第1乃至第4のアナログスイッチ21〜24により切り替えられることで、定電圧駆動と定電流駆動が選択可能となっている。

(もっと読む)

オペアンプ及び表示パネルの駆動装置

【課題】回路のレイアウト面積を小さくすることができるオペアンプ及び表示パネルの駆動装置を提供する。

【解決手段】ソースアンプ121は、差動回路300、カレントミラー回路210、出力回路212を含んで構成されている。差動回路300は、高耐圧のNMOSトランジスタN11A、N11Bがカレントミラー回路210と並列接続された差動対N11と、NMOSトランジスタN13と、を含んで構成されている。シンクアンプは、差動回路302、カレントミラー回路216、及び出力回路218を含んで構成されている。差動回路302は、高耐圧のPMOSトランジスタP12A、P12Bがカレントミラー回路216と並列接続された差動対P12と、PMOSトランジスタP15と、を含んで構成されている。

(もっと読む)

半導体装置

【課題】抵抗素子の抵抗値の基板電圧依存性をなくす。

【解決手段】基板領域(25A,25B)上に互いに直列に接続される抵抗素子(R1、R2)において、抵抗素子の基板領域と対応の抵抗素子の間の平均電位が逆極性でかつ大きさが等しくなるように、抵抗素子端部と対応の基板領域とをバイアス配線(27A,27B)で接続する。

(もっと読む)

演算増幅器

【課題】Rail to Rail動作する演算増幅器のトランスコンダクタンスを一定にする。

【解決手段】Rail to Railオペアンプ50には差動入力段1と出力段2が設けられる。差動入力段1には、第1の差動増幅部11、第2の差動増幅部12、及びバイアス切替部13が設けられる。第1の差動増幅部11には差動対をなすNch MOSトランジスタNT1及びNT2が設けられ、第2の差動増幅部12には差動対をなす定電流源14とPch MOSトランジスタPT1及びPT2が設けられる。バイアス切替部13は、入力電圧Vinレベルに応じて第1の差動増幅部11のバイアス電流Ib6と第2の差動増幅部12のバイアス電流Ib1とを切り替え、第1の差動増幅部11及び第2の差動増幅部12が共に動作する領域でのバイアス電流Ib6及びバイアス電流Ib1を補正する。

(もっと読む)

差動増幅器

【課題】トランジスタの温度差に起因する非直線性増幅誤差を広い周波数範囲に亘って低減する。

【解決手段】入力信号をバッファリングするトランジスタQ1,Q2と、該トランジスタQ1,Q2のコレクタ端子側にコレクタ電流に依存した電圧降下を発生させる電圧発生回路と、トランジスタQ1,Q2の出力をバッファリングするエミッタフォロワ回路と、トランジスタQ1,Q2にたすきがけ接続されると共にエミッタフォロワ回路によって駆動される第1の差動増幅回路と、エミッタフォロワ回路によって駆動される第2の差動増幅回路と、トランジスタQ1,Q2と第1の差動増幅回路との間に設けられたトランジスタQ9,Q10と、第2の差動増幅回路の出力に設けられたトランジスタQ11,Q12と、トランジスタQ1,Q2及び第1、第2の差動増幅回路のコレクタ-エミッタ間電圧を等しくするバイアス電圧をトランジスタQ9〜Q12に出力するバイアス回路とを具備する。

(もっと読む)

コンパレータ回路

【課題】フォールデッドカスコード接続の差動増幅段を有するコンパレータにおいて、オフセットの温度依存性を減らし検出精度を向上させる。

【解決手段】ソース共通接続された一対の差動MOSトランジスタを有する差動入力段(11)と、差動MOSトランジスタのドレイン端子にフォールデッドカスコード接続されたカスコード段(12)と、差動入力段とカスコード段に共通に接続された電流回路(Mn11〜Mn13,Mn21〜Mn23)と、カスコード段の出力ノードに接続された出力段(13)とを備えたコンパレータ回路において、前記電流回路は、カスコード段のMOSトランジスタのキャリア移動度の温度特性に起因する動作点の変動をキャンセルするような温度特性を付与された電流を流すように構成した。

(もっと読む)

差動増幅器

【課題】トランジスタの製造ばらつき等があっても、低電源電圧で動作し、広範囲の入力電圧に対してプッシュプル動作の出力電流が得られる差動増幅器を提供する。

【解決手段】差動増幅器1は、第1の導電型のトランジスタで構成され、入力信号を受けて第1の差動電流I11、I12を出力する第1の差動対10と、第1の差動電流I11、I12に基づき、第1の吐き出し側出力電流I18及び第1の吸い込み側出力電流I16をそれぞれ第1の出力端子OP及び第2の出力端子ONに対して出力する第1の電流増幅部11と、第2の導電型のトランジスタで構成され、入力信号を受けて第2の差動電流I1C、I1Dを出力する第2の差動対20と、第2の差動電流I1C、I1Dに基づき、第2の吐き出し側出力電流I1K及び第2の吸い込み側出力電流I1Iをそれぞれ第1の出力端子OP及び第2の出力端子ONに対して出力する第2の電流増幅部21と、を有する。

(もっと読む)

オペアンプ回路及びオペアンプ回路の駆動方法

【課題】CMOSオペアンプ回路において、パワーダウン状態の解除後に定常状態に安定するまでの動作速度を高速化することができるオペアンプ回路及びオペアンプ回路の制御方法を提供する。

【解決手段】パワーダウン時はSW1により電圧VDD2をノードN1に印加し、出力端OUT1から電圧VDD2が出力されるため、位相補償用コンデンサC1の両電極に電位差が生じ、電荷が蓄積され、定常状態に切り替わると蓄積されていた電荷が放電され、Nチャネル型MOSトランジスタTN3のゲートがONするため、瞬時に出力端OUT2の出力値が引き下げられた後、安定状態に落ち着く。

(もっと読む)

CMOS差動増幅回路および電源制御用半導体集積回路

【課題】入力オフセットを低減できるとともに動作点の設定が容易に行なえるCMOS差動増幅回路を提供する。

【解決手段】一対の差動MOSトランジスタ(Mp1,Mp2)と、該差動MOSトランジスタのドレイン端子に各々接続された一対の負荷MOSトランジスタ(Mn1,Mn2)と、上記差動MOSトランジスタの共通ソースに接続された電流源と、を有する差動入力段(11)と、上記差動MOSトランジスタのドレイン側の電位をゲート端子に受けるように接続された一対のN型MOSトランジスタ(Mn3,Mn4)と、該MOSトランジスタの各々と直列をなしソース端子が第1電源電圧端子に接続された一対のP型MOSトランジスタ(Mp3,Mp4)と、該P型MOSトランジスタと前記N型MOSトランジスタとの間に接続されゲート端子に各々定電圧が印加されたP型MOSトランジスタ(Mp5)およびN型MOSトランジスタ(Mn5)とを有する出力段(12)とによりCMOS差動増幅回路を構成した。

(もっと読む)

差動増幅回路

【課題】差動増幅回路のオフセット電圧を小さくする。

【解決手段】本発明の差動増幅回路は、差動入力信号を受け取るNMOSトランジスタ対を備えるN型入力段2と、N型入力段2に接続された出力段4と、前記差動入力信号を受け取るPMOSトランジスタ対を備えるP型入力段3と、P型入力段3に接続された出力段5と、出力端子OUTとを備えている。出力段5は、出力段4に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、PMOSトランジスタをNMOSトランジスタに置き換え、接地端子を電源端子に置き換え、電源端子を接地端子に置き換えた構成を有している。出力端子OUTは、出力段4の出力と出力段5の出力に共通に接続されている。

(もっと読む)

差動駆動回路および通信装置

【課題】簡単な構成で、トランジスタのゲート電圧−ドレイン電流特性は非線形であっても、またその特性が、極性が異なるトランジスタで違う特性であっても、コモンモード成分の無い差動信号が出力可能な差動駆動回路および通信装置を提供する。

【解決手段】第1および第2のトランジスタQ1,Q2のソースと電源電位源VDDの間に第1の抵抗素子R1および第2の抵抗素子R2が接続され、第3および第4のトランジスタQ3,Q4のソースと基準電位源VSS間に第3の抵抗素子R3および第4の抵抗素子R4が接続され、第1および第2のトランジスタQ1、Q2のソースと第3および第4のトランジスタQ3,Q4のソースの電圧が各々の駆動目標電圧V1〜V4に等しくなるようにフィードバックをかけて第1および第2のトランジスタQ1,Q2のゲート、第3および第4のトランジスタQ3,Q4のゲートを駆動しドレインから出力を取り出す。

(もっと読む)

増幅回路

【課題】有効動作範囲が広く、位相補償用の容量の小容量化、貫通電流の抑制を実現できる増幅回路を得る。

【解決手段】入力増幅段32と、P型MOSトランジスタ36及びN型MOSトランジスタ38がプッシュプル回路として動作する出力段34を備えた増幅回路30に、入力端が増幅回路30の出力端と接続され、出力端が第1の位相補償容量52を介してP型MOSトランジスタ36のゲート電極に接続されると共に、第2の位相補償容量54を介してN型MOSトランジスタ38のゲート電極に接続された第1の電圧バッファ40と、入力端が増幅回路30の出力端と接続され、出力端が第3の位相補償容量56を介してP型MOSトランジスタ36のゲート電極に接続されると共に、第4の位相補償容量58を介してN型MOSトランジスタ38のゲート電極に接続された第2の電圧バッファ46を付加する。

(もっと読む)

出力装置及び半導体集積装置

【課題】データパターンに関わらず、低消費電流を図ることができる出力装置を提供する。

【解決手段】外部から入力されたデータ信号を差動信号に変換して出力するドライバ回路9からの差動信号を出力する出力装置であって、ドライバ回路9から入力された差動信号を低振幅で差動出力する中継バッファ部11と、中継バッファ部11から出力される差動信号が入力され、振幅を増幅して出力する増幅アンプ部12と、ドライバ回路9に比べて高い駆動力で差動出力をするデータ出力部13とを備える。

(もっと読む)

コンパレータ

【課題】 電源電圧VDDが低い状態においても、正確に入力電圧の比較を行うことができるコンパレータを提供する。

【解決手段】 差動増幅回路10の後段のソース接地増幅回路20Aにおいて、差動増幅回路10の出力信号V2がゲートに与えられるNチャネル電界効果トランジスタ21と、その定電流負荷としてのPチャネル電界効果トランジスタ22との間にはPチャネル電界効果トランジスタ23が介挿されている。Pチャネル電界効果トランジスタ23のゲートには、電圧B=VDD/2が与えられる。Pチャネル電界効果トランジスタ23は、電源電圧VDDが低い状態において、差動増幅回路10に対する入力電圧VrefおよびVinが一致したときに、Pチャネル電界効果トランジスタ22の動作点を差動増幅回路10のPチャネル電界効果トランジスタ13の動作点に近づける。

(もっと読む)

バイアス電流発生回路およびそれを用いた差動回路

【課題】半導体プロセスに起因する遅延時間および消費電力のばらつきを小さくすることができるバイアス電流発生回路およびそれを用いた差動回路を提供する。

【解決手段】バイアス電流発生回路は、半導体プロセスによって出力電流がばらつく第1の電流発生回路14と第2の抵抗21a〜21n、第3の抵抗22を直列接続し、半導体プロセスによって出力電流がばらつかない第2の電流発生回路16と第1の抵抗20a〜20mを直列接続して、第1の電流発生回路と第3の抵抗の接続点の電圧と、第1の抵抗と第2の電流発生回路の接続点の電圧を増幅器に入力して、この増幅器の出力によって第2の抵抗と第3の抵抗の接続点から電流を引き出すと共に、この電流に関連する電流を出力する。また、このバイアス電流発生回路の出力電流で差動回路の出力段の駆動電流を決める。

(もっと読む)

増幅器及びそれを備えた液晶駆動回路

【課題】回路規模や消費電流の増加を抑えつつ、安定度を向上しつつスルーレートを改善することができるレールトゥレール型の増幅器を提供する。

【解決手段】入力にそれぞれ接続されたNMOSトランジスタの差動対MN1,2及びPMOSトランジスタの差動対MP1,2を有し、差動対を構成する各NMOSトランジスタのドレイン−ソース間に並列にドレイン−ソースを接続し、かつ所定のバイアス電圧をゲートに入力した一対のNMOSトランジスタMN21,22と、差動対を構成する各PMOSトランジスタのドレイン−ソース間にそのドレイン−ソースを接続し、かつ所定のバイアス電圧をゲートに入力した一対のPMOSトランジスタMP21,22とを設け、出力段のDCバイアスを一定にする。

(もっと読む)

演算増幅回路

【課題】広い出力電圧範囲において、一定のオフセットを実現する演算増幅回路を提供する。

【解決手段】従来の演算増幅回路30に対し、オフセット一定化回路200を設ける。オフセット一定化回路は、演算増幅回路の入力段が備えるPMOS差動電流源MP1のオン、オフを切換える第1のスイッチと、入力段が備えるNMOS差動電流源MN1のオン、オフを切換える第2のスイッチと、第1、2スイッチを切換えるタイミングを決定する電圧生成部23と、第1、2スイッチを制御する制御信号を出力する電圧比較器21を備え、入力電圧に応じPMOS差動電流源MP1とNMOS差動電流源MN1の電流を制御する。

(もっと読む)

レールトゥレール型増幅回路及び半導体装置

【課題】レールトゥレール増幅回路の消費電力の低下と小面積化の実現。

【解決手段】DACからのアナログ信号を増幅するレールトゥレール型増幅回路100であり、nチャネル型トランジスタ対を備える差動入力Ninと、pチャネル型トランジスタ対を備える差動入力Pinを備え、差動入力Pinと高電圧側の電源Vccとの間に電流源Csp1が設けられ、電流源Csp1と差動入力Pinとの間に、DACへの入力デジタルデータの所定ビット位置のデータに応じて、差動入力Pinへの電流供給を制御するPin用電流制御部Swp1を備える。低電圧側の電源Vssと差動入力Ninとの間に、電流源Csn1が設けられ、電流源Csn1と差動入力Ninとの間に、DACへの入力デジタルデータの所定ビット位置のデータに応じて、差動入力Ninへの電流供給を制御するNin用電流制御部Swn1を備える。

(もっと読む)

1 - 20 / 59

[ Back to top ]