Fターム[5K029AA01]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | 誤動作防止;誤り率の低減 (907)

Fターム[5K029AA01]の下位に属するFターム

ノイズ対策 (199)

波形劣化、符号間干渉対策 (407)

Fターム[5K029AA01]に分類される特許

1 - 20 / 301

電子装置

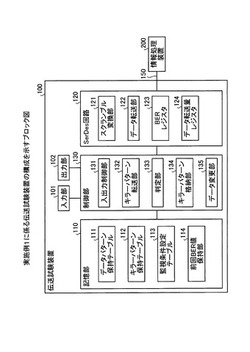

伝送試験装置、伝送試験方法及び伝送試験プログラム

【課題】伝送路にエラーを継続的に発生させること。

【解決手段】伝送路における伝送試験を行う伝送試験装置100は、判定部133と、キラーパターン転送部132とを有する。判定部133は、伝送路において試験データに生じた異常の割合を示す異常発生率を取得し、該異常発生率が所定の基準値を下回ったか否かを判定する。キラーパターン転送部132は、判定部133により異常発生率が所定の基準値を下回ったと判定された場合、試験データを変更して送信する。

(もっと読む)

二値化回路

【課題】動作速度の低下を抑えつつ、ハイレベル及びローレベルの判定精度を高めることができる二値化回路を提供する。

【解決手段】二値化回路20は、ダイオード31及びコンデンサ32を有するピークホールド回路部30と、ダイオード41及びコンデンサ42を有するボトムホールド回路部40と、コンデンサ32とダイオード31との間のノードN1の電圧、及びコンデンサ42とダイオード41との間のノードN2の電圧の平均電圧VAと入力信号Vinの電圧とを比較して入力信号Vinを二値化する比較回路部70と、上記平均電圧VAに比例する電圧を出力する基準電圧生成回路部60とを備える。ボトムホールド回路部40は、基準電圧生成回路部60から出力された電圧を基準電位VSとして用いる。

(もっと読む)

信号変換回路、その信号変換回路を備えるアイソレータ回路及び信号変換方法

【課題】高い周波数の差動信号をシングルエンドの信号に変換可能な信号変換回路、当該信号変換回路を備えたアイソレータ回路及び信号変換方法を提供すること

【解決手段】本発明にかかる信号変換回路10は、差動信号である信号D1及び信号D2が入力されるヒステリシスコンパレータ1、2及び変換バッファ3を備える。ヒステリシスコンパレータ1は、信号D1の電位V1と信号D2の電位V2との大小の比較結果を信号E1として出力する。ヒステリシスコンパレータ2は、電位V1と電位V2との大小を比較し、当該比較結果を信号E1の反転信号である信号E2として出力する。変換バッファ3は、信号E1及び信号E2をシングルエンド信号Fに変換する。

(もっと読む)

符号化装置及び符号化方法

【課題】データ値の変化頻度の低下を防止し、且つコマンドコードの設定を柔軟に行うことができる符号化装置を提供する。

【解決手段】4B5Bエンコーダ3は、入力される4ビットデータを、データ値「0」が、冒頭側,末尾側にそれぞれ1ビットまで、且つ全体では連続して2ビットまでとなる5ビットのデータパターンに変換し、5Nビットコマンドエンコーダ4は、5Nビットのビット列中において、データ値「0」が連続して2ビットまでとなるコマンドパターンに変換する。そして、変換されたデータ及びコマンドを、NRZIエンコーダ7によりNRZI符号に変換する

(もっと読む)

信号伝達装置及びこれを用いたモータ駆動装置

【課題】ドライバチップの異常検出期間が短過ぎると、異常パルス信号のパルス生成が停止された後、異常判定期間の経過前に異常パルス信号のパルス生成が再開されてしまい、コントローラチップでドライバチップの異常を認識することができなくなるおそれがあり、2つの回路を絶縁しつつ一方の異常を確実に他方に伝達することのできる信号伝達装置、及びこれを用いたモータ駆動装置を提供する。

【解決手段】信号伝達装置100は、第1回路110と第2回路120との間を絶縁しながら信号伝達を行うものであり、第1回路110は、第2回路120から伝達される異常パルス信号Sbを監視して第2回路120の異常有無を判定し、第2回路120は、第2回路120で異常が検出されてから少なくとも第1回路110で第2回路120の異常有無が判定されるまで異常パルス信号Sbを異常状態に保持する。

(もっと読む)

リンギング抑制回路

【課題】簡単な構成で波形歪みのエネルギーを消費させ、リンギングを確実に抑制できるリンギング抑制回路を提供する。

【解決手段】一対の信号線3P,3N間に、PチャネルMOSFET4及びNチャネルMOSFET5の直列回路を接続し、制御回路11は、差動信号のレベルがハイからローに変化したことを検出すると、PチャネルMOSFET4及びNチャネルMOSFET5を同時に一定期間オンさせる。これにより、差動信号のレベルが遷移する期間に信号線3P,3N間のインピーダンスを大きく低下させ、差動信号波形の歪みエネルギーをFET4及び5のオン抵抗により吸収させてリンギングの発生を抑制する。

(もっと読む)

中継装置およびコネクタ

【課題】バス型のネットワークにおいて、接続するノード数を増加させることができる中継装置およびその中継装置を備えたコネクタを提供する。

【解決手段】中継装置としてのASC1に、ビット歪み補正回路15と、リンギングパルス吸収回路16と、を備えて、ビット歪み補正回路15でビット単位にビット歪みを補正し、リンギングパルス吸収回路16で通信フレーム終端のリンギングパルスの吸収除去を行う。

(もっと読む)

回路間の無線通信デバイス、システム、及び方法。

【課題】回路間の通信に有線の相互接続を利用すると、寄生抵抗、キャパシタンス、及び/または、インダクタンスを生じさせてしまうおそれがあり、速度制限につながり、及び/または、半導体デバイスのサイズを効率的に縮小したりできなくなるため、信頼度の高い無線による相互接続をおこなう。

【解決手段】回路間の無線通信のためのデバイス、システム、及び/または、方法を含む。例えば集積チップは、所定のタイムスロットシーケンス中に、共通のウルトラワイドバンド(UWB)を介して無線パルス位置変調(PPM)信号を通信する、無線を利用して相互接続される複数の電子回路と、複数の電子回路に複数の有線フィードバックリンクを介して接続され、無線チャネルを監視して、タイムスロットシーケンスに対応するイベントフィードバックシーケンスを、フィードバックリンクを介してフィードバックするモニタ回路とを備える。

(もっと読む)

差動出力バッファ

【課題】本発明は、差動データ信号の変化を強調した強調済み差動データ信号を出力する差動出力バッファに関し、負荷容量や回路構成を大きく増やすことなく複数段にわたる高精度な強調を可能にする。

【解決手段】差動データ信号VIN,VIN_Bと、差動データ信号を所定の時間だけ遅延し、反転した、反転遅延差動データ信号EVIN_B,EVINとを、所定の比率で混合した、混合差動データ信号VB1,VB2を生成する混合回路12を有する混合段10Aと、複数の差動増幅等の組合せからなる出力段20Aとを備え、混合段10Aが、所要の強調量に応じて、混合回路12での差動データ信号と反転遅延差動データ信号との混合比を1:0、1:1、0:1のいずれかに設定する混合比設定回路を含む。

(もっと読む)

通信装置およびフィールド機器システム

【課題】異なる周波数を用いて信号の値を表現して通信するときに、正確な通信を行うことを目的とする。

【解決手段】本発明の通信装置は、第1の周波数FLと第2の周波数FHとを用いて二値の信号を通信する通信装置1であって、一定の判定周期JTの間に変化する入力信号rxdのエッジ数を検出して、出力信号sigの論理を生成する信号生成部を備えている。エッジとエッジとの間隔ではなく、一定の判定周期JTの間のエッジ数を検出して、このエッジ数に基づいて入力信号rxdが第1の周波数FLであるか第2の周波数FHであるかを認識でき、入力信号rxdの論理の判定を行うことができる。これにより、出力信号sigを生成することができる。

(もっと読む)

リング型ネットワークシステム

【課題】電気的には接続されていながら正常に通信ができないような論理的な断線状態が発生した場合であってもループバックを行なうことを可能にし、通信を継続することができるようにする。

【解決手段】マスタ局1は、送信が連続して失敗したことを検知したときに断線検出フレームを生成して隣接するスレーブ局#1(2)、#4(5)に送信する。スレーブ局#4(5)では、断線検出フレームを受信したときに応答し、自局が末端局でない場合に、送信元局以外の隣接局#3(4)に対して断線検出フレームを送信する。そして、スレーブ局#4(5)では、断線検出フレームを送信してから所定時間経過しても隣接局#3(4)からその応答を受信できない場合に、自局を末端局としてループバックを行う。

(もっと読む)

信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

(もっと読む)

伝送距離延伸装置および通信装置

【課題】10BASE−T信号の伝送距離を延伸することが可能な伝送距離延伸装置を得ること。

【解決手段】入力した10BASE−T信号のSOI(Start Of Idle)位置を検出するSOI位置検出部12と、SOI位置において、10BASE−T信号の振幅レベルを検出するレベル検出部13と、レベル検出部13によって検出された振幅レベルに基づいて、10BASE−T信号に対して、伝送路ケーブルの減衰量に対応したケーブル等価処理を施す可変等価部11と、SOI位置において、可変等価部11によってケーブル等価処理が施された信号の振幅レベルを検出するレベル検出部14と、ケーブル等価処理が施された信号を増幅する増幅部16と、レベル検出部14によって検出された振幅レベルに基づいて、増幅部16の増幅率を制御するゲイン制御部15と、を備える。

(もっと読む)

リピータ装置

【課題】簡易な構成でありながら、自動的に適切な高域ゲインに調整することのできるHDMIリピータ装置を提供する。

【解決手段】第1認証判断手段4は、ライン18のDDC信号を監視し、HDCP第1認証が行われるか否かを判断する。HDCP第1認証が行われると判断すると、高域ゲイン調整手段6は、イコライザ部2の高域ゲインを調整する。強制ホットプラグ手段8は、強制的にホットプラグ検出信号を出力し、調整された高域ゲインによって、HDMIソース装置SOからHDMIシンク装置SKにTMDS信号を送信させるようにする。

(もっと読む)

情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体

【課題】調歩同期式のシリアル通信における通信データのサンプリングタイミングを簡単な回路構成によって制御することで通信データ単位でのサンプリング誤差の累積を防止し、通信データの受信エラーの発生を抑止することができるようにした情報受信制御装置、情報受信制御方法、情報受信制御プログラムおよび記録媒体を提供する。

【解決手段】調歩同期式のシリアル通信に用いられるビット単位の通信データの受信の際に、「基準クロックを分周したカウンタークロック」のカウンタークロック数に対する、「基準クロックから算出される分周値をもとにハード特性を考慮した特性分周値」を計算する。分周値と特性分周値を用いて算出されるそれぞれのカウンタークロックに基づく誤差からビット単位での誤差量を算出し、その誤差量をもとにカウンタークロック数の計数を行う際の初期値を決定する。

(もっと読む)

差動信号出力装置、差動信号出力装置のテスト方法、および、テスタ

【課題】差動信号とコモンモード信号をより適切に評価することが可能な差動信号出力装置を提供する。

【解決手段】差動信号を評価する差動信号テストモードにおいて、差動信号出力装置の第1の制御回路は、第1の制御信号に応じて、差動信号生成回路にデータ信号に応じた差動信号を生成させて第1および第2の送信端子に出力させ、且つ、差動信号出力装置の第2の制御回路は、第2の制御信号に応じて、コモンモード信号生成回路の動作を停止する。コモンモード信号を評価するコモンモード信号テストモードにおいて、第1の制御回路は、第1の制御信号に応じて、差動信号生成回路に固定の差動信号を生成させて第1および第2の送信端子に出力させ、且つ、第2の制御回路は、第2の制御信号に応じて、コモンモード信号生成回路にクロック信号に応じたコモンモード信号を生成させて第1および第2の送信端子に出力させる。

(もっと読む)

電気信号の伝送回路、IC、プリント配線板、機器およびシステム

【課題】CMOS伝送回路において、レシーバの動作を不安定にしたり不要輻射を放出したりするリンギングの発生を抑制した電気信号の伝送回路を提供する。

【解決手段】本発明の一態様は、CMOSドライバと伝送線とCMOSレシーバとを有する電気信号の伝送回路において、CMOSドライバのPMOS FET1と並列にアノード電極がドライバ出力端子につながれるように第1のダイオード6を接続し、CMOSドライバのNMOS FET2と並列にカソード電極がドライバ出力端子につながれるように第2のダイオード7を接続し、PMOS FET1のデバイストランスコンダクタンスと第1のダイオード6の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにし、NMOS FET2のデバイストランスコンダクタンスと第2のダイオード7の(飽和電流)/(理想係数×熱電圧)2とが等しくなるようにしたことを特徴とする電気信号の伝送回路である。

(もっと読む)

信号断検出回路、信号断検出方法及び光受信器

【課題】異なるビットレートの信号を時分割で受信した場合においても、ビットレートに関係なく信号断検出時のビットエラーレートを等しくし得る信号断検出回路を提供する。

【解決手段】信号断検出回路1は、複数のビットレートのそれぞれに固有の光受信レベルの閾値(201,601)を用い、信号入力部10の出力信号102に含まれる当該各ビットレートの信号についてその有無を検出する信号検出部(20,60)と、信号入力部10の出力信号102が複数のビットレートのいずれに属するかを判別するビットレート判別部70と、ビットレート判別部70で判別されたビットレートについて信号検出部(20,60)が信号の無を検出した場合に、信号断を示す信号(ローレベル電圧のLOS信号804)を出力する信号断アラーム生成部80と、を備えたことを特徴とする。

(もっと読む)

メモリ制御回路及びそれを用いたデータ伝送システム

【課題】送信機、受信機の双方において新たな入力端子を設ける必要がないデータ伝送システムを提供すること。

【解決手段】本発明に係るメモリ制御回路は、それぞれが第1及び第2の入力端子を備え、各前記第1の入力端子に外部メモリから受信したデータ信号が入力される複数のコンパレータと、前記外部メモリから受信した差動ストローブ信号の正相及び逆相の双方から、各前記第2の入力端子に入力される複数の基準電圧を生成する基準電圧発生回路と、を備えるものである。

(もっと読む)

1 - 20 / 301

[ Back to top ]