Fターム[5K029AA11]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | 高速動作化;伝送速度の向上 (263)

Fターム[5K029AA11]に分類される特許

21 - 40 / 263

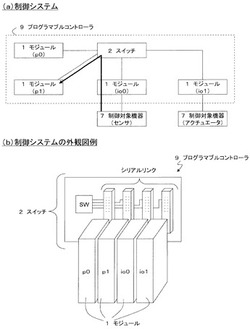

プログラマブルコントローラ、および、通信制御方法

【課題】スイッチを介して制御データを伝送するときに、その伝送効率およびリアルタイム性を向上させること。

【解決手段】複数のモジュール1と、モジュール1間通信を中継するスイッチ2とを含めて構成されるプログラマブルコントローラ9であって、構成制御部31は、複数の周期的フローについて、その送信元と、送信先と、周期とが入力されると、送信元および周期の組み合わせが一致する複数の周期的フローと、送信先および周期の組み合わせが一致する複数の周期的フローとをそれぞれ衝突するフロー群として抽出し、衝突するフロー群における送信タイミングについて、互いに異なるタイミングを計算して、切替順序データ35および送受信順序データ42に書き出す。

(もっと読む)

長距離光伝送装置、及び長距離光伝送システム

【課題】長距離伝送路区間における通信速度がより高速化しても、比較的簡素な構成で安定した通信を実現する。

【解決手段】40Gbpsで通信を行うメディアコンバータ6,8は、光トランシーバ20、フレーム処理部22、FEC24〜30、長距離TR32〜38、及び波長フィルタ40を備えている。また、これらの間では、電気信号を4本のレーンでパラレル転送する。FEC24〜30、及び長距離TR32〜38は10Gbpsの通信速度に対応しており、各レーン別に転送された電気信号に対してFECを生成し、電気信号を光信号に変換する。

(もっと読む)

送信装置、送信方法、受信装置、受信方法、送受信システムおよびケーブル

【課題】後方互換性を確保しつつ、高いデータレートでの信号伝送を可能する。

【解決手段】ソース機器110およびシンク機器120をHDMIケーブル200により接続する。ソース機器110は、現行HDMIおよび新HDMIの双方に対応している。ビデオデータ等のデジタル信号を伝送するための差動信号チャネルは、現行HDMIが3チャネルであるのに対して、新HDMIでは例えば6チャネルとされる。ソース機器110の制御部113は、ケーブル200が新HDMIに対応し、かつシンク機器120が新HDMIに対応している場合、データ送信部112を新HDMIの動作モードに制御する。一方、制御部113は、少なくとも、シンク機器120が現行HDMIにのみ対応していると判断する場合、あるいはケーブル200が現行HDMIに対応していると判断する場合、データ送信部112を現行HDMIの動作モードに制御する。

(もっと読む)

データ伝送装置、システム、方法及びプログラム

【課題】高速伝送を実現するための伝送制御値を効率的に特定すること。

【解決手段】本発明のデータ伝送装置は、高速伝送路を介してデータを伝送するめの伝送制御値における複数の候補値を格納する記憶部と、設定された伝送制御値に基づいて高速伝送路を介してデータを送信する第1のデータ処理回路と、第1のデータ処理回路から高速伝送路を介してデータを受信する第2のデータ処理回路と、記憶部から一の候補値である伝送制御値を取得し、当該取得した伝送制御値を第1のデータ処理回路に設定する設定部と、を備え、第2のデータ処理回路は、第1のデータ処理回路との高速伝送路を介したデータ伝送中にエラーを検出した場合、設定部へ割込み信号を出力し、設定部は、第2のデータ処理回路から割り込み信号を受け取った場合に、記憶部に格納された複数の候補値の中から未取得の伝送制御値を取得し、当該取得した伝送制御値を第1のデータ処理回路に設定する。

(もっと読む)

出力バッファ回路及び半導体装置

【課題】デエンファシス機能を有する出力バッファ回路において、デエンファシス設定を行うと、デエンファシス非設定時には発生しなかったACコモンモードノイズの発生や、デエンファシス強度の低下が起きる。

【解決手段】電流補正回路により、デエンファシス機能を実現するための2つのバッファ回路に供給する電流を補正する。この補正回路により、デエンファシス設定時のACコモンモードノイズの発生を抑制し、デエンファシス強度の低下を防止する。

(もっと読む)

半導体回路及び半導体回路の信号取込方法

【課題】異なる入力方式で入力される信号を入力方式に応じて適切に取り込むことができる、半導体回路及び半導体回路の信号取込方法を提供する。

【解決手段】差動入力方式の場合には、差動入力回路16は、P側入力端子12に入力されたデータ信号及びN側入力端子14に入力されたデータ信号が入力される差動アンプ30の出力信号outから、DFFN32がクロック信号の立ち下がりのタイミングでEVENデータを取り込む。また、出力信号outから、DFF34がクロック信号の立ち上がりのタイミングでODDデータを取り込む。シングル入力方式の場合には、シングル入力回路18は、P側入力端子12に入力されたODDデータを取り込むためのデータ信号からDFF44がODDデータを取り込むと共に、N側入力端子14に入力されたEVENデータを取り込むためのデータ信号からDFF45がEVENデータを取り込む。

(もっと読む)

アライメントマーカ重複判定回路、アライメントマーカ重複判定方法およびプログラム

【課題】データを複数のレーンに振り分け、レーン毎にアライメントマーカを挿入して行われるデータ通信における、アライメントマーカの誤設定を検出する。

【解決手段】受信装置に含まれる整列同期回路において、アライメントマーカ検出回路110−0〜110−(n−1)がライン0〜ライン(n−1)に含まれるアライメントマーカを検出する。そして、検出されたアライメントマーカの示すレーン番号が複数のラインについて同一であると判定した場合に、レーン番号重複判定回路130がアライメントマーカ重複を示す信号を出力する。

(もっと読む)

受信装置及び該装置を備えた機器

【課題】 制御情報の種類や制御情報量の増加に伴い、データ転送の高速化を実現する。

【解決手段】 クロック信号に基づいて、複数ビットで構成される第1情報と前記複数ビットより少ないビット数で構成されている第2情報と少なくとも1ビットのフラグを含むデータ信号を入力する第1シフトレジスタと、トリガ信号に基づいて、第1情報をラッチする第1ラッチ回路と、第1パルス信号に基づいて、第1シフトレジスタから前記第2情報を入力する第2シフトレジスタと、第2パルス信号に基づいて、第2情報をラッチする第2ラッチ回路と、フラグがセットされていれば前記トリガ信号の入力に応じて第1パルス信号を出力し、フラグがセットされていなければ前記トリガ信号の入力に応じて第2パルス信号を出力する制御回路とを備える受信装置。

(もっと読む)

高速送信器ドライバ回路のための構成可能なエンファシス

【課題】シリアルデータ信号において、シリアルデータ信号内の直前のビットのデータ値とは異なる各ビットにプレエンファシスを与える回路を提供すること。

【解決手段】シリアルデータ信号において、該シリアルデータ信号内の直前のビットのデータ値とは異なる各ビットにプレエンファシスを与える回路であって、該回路は、各次のビットのデータ値を示す方向に回路要素内に第1の電流を流す第1の回路と、1つのビットが、該1つのビットの直前にあるビットと同一のデータ値を有する条件に応答して、該第1の電流とは反対の方向に該回路要素内において流れるように第2の電流を流す第2の回路と、該回路要素における正味の電流の量および方向に基づいて、シリアルデータ出力信号を生成する第3の回路とを備える、回路。

(もっと読む)

信号送信装置及び信号送信方法

【課題】RGBフル画素構造とした撮像素子から受け取った画像信号を現行の伝送フォーマットを用いて伝送する。

【解決手段】1サンプルに配置されたR,G,B画素がそれぞれR,G,Bの画像信号を出力する画素配列としたRGBフル画素構造の撮像素子であって、撮像素子から順に所定のサンプル数でライン方向に読出されて入力する画像信号に処理を施す。SAV/EAV多重部19−1〜19−12は、同一のサンプルに配置されたB,R画素から読出された画像信号を交互にCch相当のアクティブ領域に多重してB/Rchを生成する。合わせて、ライン方向に隣り合うサンプルのG画素から読出された画像信号を順にYch相当のアクティブ領域に多重してGchを生成する。そして、8B/10Bエンコーダ21は、B/Rch及びGchにおけるアクティブ領域並びに補助データ領域を8B/10Bエンコーディングし、変換したシリアル・デジタルデータを出力する。

(もっと読む)

バッファ回路およびそれを用いた半導体装置、出力回路および電子機器

【課題】高速信号を確実に伝送可能なバッファ回路を提供する。

【解決手段】電流源312は、定電流Icを生成する。第1トランジスタM1は、その一端が電流源312と接続され、その制御端子に入力信号SINが入力される。反転回路314は、入力信号SINを反転および遅延させ、反転入力信号SIN#を生成する。第2トランジスタM2は、その一端が電流源312と接続され、その制御端子に反転入力信号SIN#が入力される。バッファ回路310は、第1トランジスタM1および第2トランジスタM2の、電流源312と共通に接続された一端に生ずる信号SOUTを出力する。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

電子回路装置

【課題】信号の遅延時間を調整することにより、インピーダンス不整合によって発生するディターミニスティックジッタを低減することが可能な電子回路装置を提供することを目的とする。

【解決手段】本発明の代表的な構成は、高速シリアル伝送により伝送路106を通じてドライバ104からレシーバ108へ信号を伝達する電子回路装置100であって、伝送路106上のインピーダンス不整合点の上流側または下流側の近傍に、このインピーダンス不整合点のキャパシタンスとの間で遅延回路を構成するインダクタ112、LC回路114またはLCR回路を備えていることを特徴とする。

(もっと読む)

空調機

【課題】伝送路の残留電荷を放電させるための放電抵抗による電力消費を抑制する空調機を提供する。

【解決手段】2つの放電抵抗R5,R6の間にアナログスイッチを介挿しておき、伝送路4の2線(P1,P2)にAMI信号を送出する際に、高レベルの信号電圧を出力するときはアナログスイッチS1をオフの状態とし、低レベルの信号電圧を出力するときはアナログスイッチS1をオンの状態とする放電制御を、MCU30により行う。

(もっと読む)

無線通信装置

【課題】変調効率が高い無線通信装置を提供することを課題とする。

【解決手段】無線通信装置は、ベースバンド信号生成器により生成されたNビットのデジタルデータに応じて、クロック発生器により生成された2N個のパルス信号のうちの1個のパルス信号を選択するセレクタと、セレクタにより選択されたパルス信号のパルス幅を短くする短パルス発生器と、短パルス発生器によりパルス幅が短くされたパルス信号に含まれる周波数成分の中から通過周波数帯域の周波数成分のみを通過させ、通過周波数帯域以外の周波数成分を減衰させるバンドパスフィルタとを有し、クロック発生器により生成される2N個のパルス信号は、第1のパルス及び第2のパルスを含む全期間非送信パルス(S0)、第3のパルス及び第4のパルスを含む全期間送信パルス(S7)、並びにパルス幅が同じであって位相が異なる2N−2個の一部期間送信パルス(S1〜S6)を含む。

(もっと読む)

高電圧差動信号方式のためのドライバ回路

高電圧差動信号方式のためのドライバ回路(200)。この回路は、入力に応答して第1の出力で第1の正の遷移を生成する第1の正のドライバ(205A)を含む。この回路は更に、第1の正のドライバに結合され、電流の生成を可能にする第1の電流要素(210A)を含む。更に、この回路は、第1の電流要素(210A)に結合され、第1の電流要素に起因して、入力及び電流に応答して、第1の正の遷移の速度に類似する速度で、第2の出力で第1の負の遷移を生成する、第1の負のドライバ(215A)を含む。  (もっと読む)

(もっと読む)

信号制御装置および信号制御方法

【課題】異なるトリガー点における電圧のオフセットの発生を抑止でき、回路のバラツキの影響を防止でき、精度の向上を図れる信号制御装置および信号制御方法を提供する。

【解決手段】入力信号のトリガー点が異なる複数の電圧と可変のバイアス信号とを順次間欠的に比較する比較部12と、比較部12の比較結果に応じてバイアス信号、並びに、入力信号を制御するための入力信号制御信号を生成する機能を有する制御部16と、を有し、制御部16は、バイアス電圧がトリガー点の異なる複数の電圧より小さいときはバイアス電圧の値を大きくするように制御し、バイアス電圧がトリガー点の異なる複数の電圧より大きいときはバイアス電圧の値を小さくするように制御し、バイアス電圧がトリガー点の異なる複数の電圧の間にあるときは、前のトリガー点の電圧が後のトリガー点の電圧に近づくように入力信号制御信号を生成する。

(もっと読む)

信号受信装置及び信号処理方法

【課題】簡易な構成で、PPM信号を確実に再生するために正確にPPM信号をサンプリングできる信号受信装置を提供する。

【解決手段】パルス位置変調信号のうち検出対象区間から任意のHパルスの立ち上がりまたは立ち下がりエッジを開始点として設定する第1の設定手段と、前記検出対象区間における複数のHパルスの間隔に基づいてサンプリング周期を算出する算出手段と、前記検出対象区間について、前記開始点から前記サンプリング周期の倍数を基準点とし、前記基準点からの前記複数のHパルスの発生位置を検出する検出手段と、前記複数のHパルスの発生位置についてヒストグラムを生成する生成手段と、前記基準点に前記ヒストグラムでピークとなる値を加えた位置を前記パルス位置変調信号における再生対象信号区間のサンプリング点と決定する決定手段と、前記サンプリング点に基づいて前記再生対象信号区間を再生する再生手段とを有する。

(もっと読む)

半導体装置

【課題】動作用クロックの周波数にかかわらず、所要のビットレートに近いビットレートでシリアル通信を行えるようにする。

【解決手段】半導体装置は、所定の動作用クロックに従って動作するシリアルコミュニケーションインタフェース(109)を含む。上記シリアルコミュニケーションインタフェースに、上記動作用クロックをカウントし、それに基づいて、上記単位転送時間を規定するための基本クロックを生成するボーレートジェネレータ(202)と、生成された基本クロックに従って送受信制御を行うための送受信コントローラ(201)とを設ける。さらに上記シリアルコミュニケーションインタフェースに、上記動作用クロックの上記ボーレートジェネレータへの供給を部分的にマスクすることで所望のビットレートを実現可能なビットレートモジュレータ(203)を設けることで、所要のビットレートに近いビットレートでのシリアル通信を実現する。

(もっと読む)

プリント回路板及び情報処理装置

【課題】環境温度が急に変化した場合等にも伝送エラーが発生しないプリント回路板を提供する。

【解決手段】プリント回路板1のプリント配線板を、伝送路20の近傍に、キャパシタンス測定用の測定パターン25が形成されているものとすると共に、プリント回路板1のプリント配線板上に、測定パターン25によるキャパシタンスの測定結果に基づき、良好な信号伝送が行えるように、送信回路21及び/又は受信回路22の送信タイミング、受信タイミング等を制御する監視回路10を搭載する。

(もっと読む)

21 - 40 / 263

[ Back to top ]