Fターム[5K029AA11]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | 高速動作化;伝送速度の向上 (263)

Fターム[5K029AA11]に分類される特許

121 - 140 / 263

送信基準パルスを使用する信号方式

信号方式は、変化する位相を有する送信基準パルスを使用する。基準パルスの位相は、ランダムな形で、またはデータストリームに従って変化させることができる。いくつかの態様では、送信機は、送信基準信号中に追加のデータストリームを符号化するために基準パルスの位相を変調する。いくつかの態様では、これらの技術は、コヒーレント受信機および非コヒーレント受信機を含む異種ネットワークで使用される。いくつかの態様では、これらの技術は超広帯域システムで使用できる。  (もっと読む)

(もっと読む)

送信方法、送信装置および受信装置

【課題】データを送信するのに必要とするデータ伝送速度に対し、無線通信速度がはやい場合、周波数、時間という通信資源を有効に活用していないことになる。

【解決手段】送信装置は複数のデータ伝送速度に対応した無線送信部を複数具備し、受信装置も同様に複数のデータ伝送速度に対応した無線受信部を複数具備し、ユーザが必要としているデータ伝送速度に対し、送信装置は最適な無線送信部を使用し、受信装置も同様に最適な無線受信部を使用して通信を行うことで、周波数、時間などの通信資源を効率よく使用することが可能となる。

(もっと読む)

信号伝送回路

【課題】複数のレーンを有し、各レーンからの出力振幅が可変する信号伝送回路において、回路規模の増大を抑制し、マージンテストの実施を容易にする。

【解決手段】4つのレーンを有する信号伝送回路100は、定電圧を生成する定電圧回路110と、電流供給回路120と、レーン毎に設けられた差動ドライバ回路130A〜130Dを備える。定電圧回路110は、定電圧回路110からの定電圧を受けて、所定の電圧電流変換率に応じた大きさの電流を4つ生成して並列に出力する。差動ドライバ回路130A〜130Dは、電流供給回路120から出力された電流をそれぞれ受けて、所定の電流電圧変換率に応じた振幅の電圧を出力する。電流供給回路120は、分圧回路115とアナログセレクタ126を備え、それらにより電圧電流変換率を変更可能な電流供給制御回路を構成する。

(もっと読む)

バースト制御パルス発生回路、バースト制御パルス発生回路を備えたデジタル変調回路及び電子機器

【課題】低消費電力で動作するバースト制御パルス発生回路。

【解決手段】通信に用いるパルス信号を発生するバースト制御パルス発生回路100であって、バースト制御パルス発生回路100は、通信のオン/オフを制御するバースト信号Burstに基づき周期信号を発振するタイミング発生回路200と、タイミング発生回路200から出力される周期信号に基づきパルス信号Pulseを生成するパルス発生論理回路300と、を有し、バースト信号Burstがオン状態のとき1回以上のパルス信号Pulseを発生し、バースト信号Burstがオフ状態のときパルス信号Pulseの発生を停止する。

(もっと読む)

信号送信方法、信号受信方法および送信回路、受信回路

【課題】より確実な信号処理を可能とする信号伝送技術を提供する。

【解決手段】送信回路20のパラレルシリアル変換部22は、同期クロックCK_SYNCよりもn倍(nは2以上の整数)以上高速な伝送クロックに同期してn本の信号を多重化してシリアル形式へ変換する。パラレルシリアル変換部22は、タイミング上の制約が厳しい信号を最初に処理することにより、その信号が最初に含まれる形で信号フレームを形成する。受信回路30のシリアルパラレル変換部32は、伝送クロックCK_TRSに同期して、シリアル形式の信号を、パラレル形式の信号に展開する際、シリアル形式にて受信した各信号のタイミングに応じて、順次、後段の回路へ出力する。

(もっと読む)

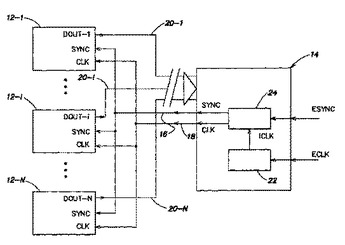

シリアルディジタルデータ通信インターフェイス

伝播遅延が数クロックサイクル長までおよび、ゆっくりと変動する可能性のある、データ送信機12からデータ受信機14へのデータ伝送のシリアルプロトコルおよびインターフェイス。データ受信機は、データ送信機にクロックを供給する。受信機または送信機のいずれかによって供給される同期信号は、クロックによって制御される転送レートで、データ伝送のフレームを始動させる。同期信号は、フレーム長として知られている、データヘッダーとそれに続く所定の数のデータビットの送信を調整する。データ受信機は、ヘッダービットを使用して、後続のデータビットをサンプリングする時間を決定する。フレームの長さは、ビット誤りを発生させるほど大きく伝播遅延ライン特性が変化しないことの十分な見込みを得るように限定される。システムは、各フレームの始点において、再同期する。  (もっと読む)

(もっと読む)

オーバーサンプリング回路及びオーバーサンプリング方法

【課題】等間隔の位相でオーバーサンプリングされたデータを生成することができるオーバーサンプリング回路及びオーバーサンプリング方法を提供する。

【解決手段】多相クロックを生成する際に、全ての回路が等価であるとは考えず、それぞれ異なる遅延時間を持つ遅延部を用いて多相クロックを生成し、そのサンプリングデータを元に等間隔の位相でオーバーサンプリングされたデータを生成するものである。また、位相の検出にはサンプリングされたデジタルデータを用いるので、小さい回路規模で高精度な位相検出を行う事ができる。従って、等間隔の位相でオーバーサンプリングされたデータを生成することができる。

(もっと読む)

1ビット高速デジタルサンプラーおよびビット決定ウィンドウを用いた超広帯域インパルス無線通信システム

【課題】超広帯域インパルス及び1−ビットデジタルサンプラーを使用する超広帯域インパルス無線通信システムにおいて、簡単なOOK(ON−OFF−Keying)変調またはパルス位置変調(PPM)方式を実現する。

【解決手段】インパルス発生器の出力を増幅するための増幅器とを含む送信RFモジュールと、受信された信号のエンベロープを検出するための2段包絡線検波器と、検出された信号を球形パルスに変換する比較器とを含む受信RFモジュールと、前記受信RFモジュールから伝送される信号を1−ビットデジタルサンプラーを用いてデジタル信号に復元するためのデジタル信号復元部と、インパルス変調またはパルスマッピングのための送信信号処理部と、デジタル信号を同期化し且つシンボル同期を追跡するための受信信号処理部と、超広帯域インパルス信号を送受信するための超広帯域アンテナと、を含む。

(もっと読む)

高速LVDS通信の同期のための方法及びシステム

方法及びシステムは、複数の低電圧差動信号(LVDS)チャネル(50)を介してペイロードデータを伝達する。第1装置(100)は、ペイロードデータ及び同期情報を、ペイロードデータに同期するワードクロックと共に、N個のLVDSチャネル(50)を介して第2装置(150)へ送信する。第2装置は、ワードクロックからM個のLVDS受信クロックを生成する。各LVDS受信クロックは、ワードクロックの周波数のP倍である同じ周波数を有し、且つ、異なる位相を有する。第2装置(150)のN個のLVDS受信器(160)の夫々は、M個のLVDS受信クロックの夫々について相関値を生成するようM個のLVDS受信クロックの夫々を用いて同期データを基準ワードと関連付け、最大相関値を生成する選択されたLVDS受信クロックを選択し、この選択されたLVDS受信クロックにより対応するLVDSチャネルについてペイロードデータを受信する。  (もっと読む)

(もっと読む)

信号伝送回路、CMOS半導体デバイス、及び回路基板

【課題】大規模集積回路内に形成される長い信号線路或いは接続される被駆動回路の数が多数存在する等により形成される静電容量の容量値が大きい信号線路の信号伝送特性を改善する。

【解決手段】駆動回路及び被駆動回路の電源電圧の中点電圧を出力し、出力インピーダンスが低い付加回路を信号線路に接続し、信号線路の電位を電源電圧の中点電圧に維持すると共に、駆動回路から出力される駆動信号を中点電圧(被駆動回路の閾値電圧)を中心に小振幅で励振させ、この小振幅に制限された駆動信号により被駆動回路を駆動させる。

(もっと読む)

Qモニターを持つデジタル信号受信機

高ビットレートデジタル信号のためのデジタル信号受信機は、1つの直列信号入力20、20’およびN>1として複数のN個の並列デジタル信号出力26を有する。その受信機は、少なくともN+1個のデジタルサンプリングチャネル31−35と、前記サンプリングチャネル31−35の少なくとも2つの出力信号を比較するためのQモニター37、38と、前記サンプリングチャネル31−35のうちのN個を前記出力リード36に、および前記サンプリングチャネル31−35のうちの少なくとも2つを前記Qモニター37、38に制御可能に接続するためのスイッチ構成36とを含む。これは、N個の出力信号を提供するためにサンプリングチャネルのうちのN個を使用することを許容し、一方で同時に、少なくとも1つの残りのサンプリングチャネルが、アイダイアグラムを走査するためにQモニターによって使用されてもよい。  (もっと読む)

(もっと読む)

送信装置、受信装置、伝送システム、変調方法、および復調方法

【課題】コスト高、大型化を招くことなく、スキューの発生を抑止でき、多値信号の伝送を、分解能を劣化させることがなく、効率的に行うことができる送信装置、受信装置、伝送システム、変調方法、および復調方法を提供する。

【解決手段】3ビット(8値)の振幅多値変調信号に変換し、その変調信号の先頭または最後尾に2値で反転するフレーム同期信号FSYNCを付加して伝送することで1本のシリアルデータとして伝送する送信装置2と、送信装置2から受信したフレーム同期信号FSYNCに基づいて、クロック信号CLK2を再生し、再生したクロック信号CLK2に基づいて受信したデータ信号のサンプリング等によりアナログ・デジタル変換を行って、データ再生(復調)を行う受信装置3とを有する。

(もっと読む)

送信装置およびそれを利用した伝送装置ならびに電子機器

【課題】データ伝送を高速化する。

【解決手段】送信装置100は、送信すべき差動信号Sout+、Sout−を、第1、第2出力端子T1、T2を介して、電流信号として送信する。第1スイッチングトランジスタMsw1および第1出力トランジスタMo1は、電位が固定された接地端子と第1出力端子T1との間に直列に接続される。第2スイッチングトランジスタMsw2および第2出力トランジスタMo2は、接地端子と第2出力端子T2との間に直列に接続される。第1、第2バイアストランジスタMb1、Mb2は、第1、第2スイッチングトランジスタMsw1、Msw2と並列に設けられ、所定のバイアス電流を生成する。送信すべき差動信号Sin+、Sin−のペアを、第1、第2スイッチングトランジスタMsw1、Msw2のゲートに入力し、第1、第2出力トランジスタMo1、Mo2のゲートを、所定の第1電圧Vbias1にバイアスする。

(もっと読む)

受信装置およびそれを利用した伝送装置ならびに電子機器

【課題】高速なデータ伝送を実現する。

【解決手段】第1入力トランジスタM5、第1抵抗R1、第1受信バイアストランジスタM7は、第1入力端子T3と電源電圧Vddが印加される電源端子T5との間に直列に接続される。第2入力トランジスタM6、第2抵抗R2、第2受信バイアストランジスタM8は、第2入力端子T4と電源端子T5との間に直列に接続される。差動アンプAMP1は、第1電圧Vx1と、第2電圧Vx2と、を差動増幅する。第2入力トランジスタM6のゲートに、第3電圧Vx3を印加するとともに、第1入力トランジスタM5のゲートに、第4電圧Vx4を印加する。受信バイアス回路16は、第1、第2受信バイアストランジスタM7、M8のゲートに、電源電圧Vddに応じて変化するバイアス電圧Vbias3を印加する。

(もっと読む)

出力制御回路

【課題】高速動作でも安定して動作する、回路規模の小さい出力制御回路を提供すること。

【解決手段】出力制御回路は、入力信号の電圧レベルを反転した電圧レベルを有する信号を出力する、直列に接続された第1のインバータ部及び第2のインバータ部と、第2のインバータ部からの出力信号の電圧レベルに応じて出力が制御される第1の出力部と、第2のインバータ部からの出力信号の電圧レベルを反転した電圧レベルを有する信号を出力し、出力側が第1のインバータ部の出力側に接続された第3のインバータ部と、第1のインバータ部からの出力信号の電圧レベル及び第3のインバータ部からの出力信号の電圧レベルに応じて出力が制御される第2の出力部とを備える。

(もっと読む)

信号伝送システム、信号伝送方法及びプログラム

【課題】シリアルデータバスを用いた多対1ノード間のデータ転送を簡単な構成で良好に行うことができる信号伝送システム、信号伝送方法及びプログラムを提供する。

【解決手段】シリアルバス4を介して複数のスレーブノード3から1つのマスターノード1へのデータ伝送する際、シリアルデータに埋め込まれるクロック信号の位相を予めマスターノード1側の基準クロック信号に合わせることにより、スレーブノード3が切り換わっても再同期のオーバーヘッドが生じないようになる。

(もっと読む)

受信装置、伝送システム、および受信方法

【課題】振幅方向の多値変調通信において、高速なデータ伝送速度であっても、ジッタの少ないクロック再生を簡単な回路構成で実現することが可能な受信装置、伝送システム、および受信方法を提供する。

【解決手段】受信装置3は、受信信号の最小値から最大値までの間に、2n−1個のしきい値を設定し、設定したしきい値と受信信号とを比較器によりそれぞれ比較して2n−1個の比較器出力を得、2n−1個の比較器出力のうち、受信信号の最小値に近い第1のしきい値が第1レベルLから第2レベルHに変化するタイミングと、受信信号の最大値に近い第2のしきい値による比較出力が第2レベルから第1レベルに変化するタイミングの、二つのタイミングからクロックを再生し、この再生クロックを位相調整したクロックCLK2に同期して2n−1個の比較出力をラッチする。

(もっと読む)

送信装置、通信システム、およびインパルス無線変調方法

【課題】インパルス無線通信において、繰り返しデータから生じる離散成分を抑圧すること。

【解決手段】プレフィックスビット生成部104は、1つまたは複数のプレフィックスビットをランダムに生成し、プレフィックスビット結合部106は繰り返しソースデータにプレフィックスビットを付加する。最初のプレフィックスビットは、繰り返しソースデータの先頭に付加する。差動符号化部108は、プレフィックスビットが付加されたシーケンス107に対し差動符号化を施し、IR変調部110は差動符号化後のシーケンス109に対しインパルス無線変調を施し、RF送信部112は、インパルス無線変調信号に所定の無線送信処理を施し、アンテナ114を経由して送信する。

(もっと読む)

データ処理装置

【課題】入力データを二値化した二値化出力のデューティを高精度に制御し、正しく入力データを復元し受信特性を向上させるデータ処理装置を提供することを目的とするものである。

【解決手段】データ処理装置200は、二値化部21により入力された入力データをスレッショルド電圧に基づき二値化して二値化出力とし、この二値化出力からデータを取り込む。そして、データ処理装置200は、この二値化出力のデューティを検出するデューティ検出部22を有し、デューティ検出部22により検出されたデューティに基づいて入力データのレベルを制御する。

(もっと読む)

差動信号駆動回路及び差動信号駆動方法

【課題】差動出力信号のばらつきを短時間で抑制することができる。

【解決手段】本発明による差動信号駆動回路は、2つの電流源P1、N1から供給される電流に基づき、入力される差動入力信号(Vin1−Vin2)に応じた差動出力信号(Va−Vb)を出力するドライバ回路1と、差動出力信号(a−Vb)に基づき2つの電流源P1、N1を制御して2つの電流源P1、N1から供給される電流の値を決定するコモンフィードバック回路2Aとを具備する。

(もっと読む)

121 - 140 / 263

[ Back to top ]