Fターム[5K029HH05]の内容

直流方式デジタル伝送 (8,390) | 受信部 (1,135) | 等化 (135)

Fターム[5K029HH05]の下位に属するFターム

量子化帰還 (4)

Fターム[5K029HH05]に分類される特許

1 - 20 / 131

信号伝送システムおよび信号伝送方法

【課題】通信装置等のデータ伝送を行うシステムにおいて、その運用中に、データの伝送を妨げることなく、伝送損失を補正することのできる信号伝送システムを提供することを目的とする。

【解決手段】伝送システムは、第1の回路と、第2の回路と、第1の回路から第2の回路に差動信号によってデータを伝送する伝送線路と、差動信号の伝送の間隙を監視する監視部と、監視部によって監視された間隙において、差動信号の伝送損失を補正する補正部と、を備える。

(もっと読む)

基準電圧変換回路及び半導体装置

【課題】回路規模を削減することが可能な基準電圧変換回路を提供する。

【解決手段】基準電圧変換回路100は、VDDとGNDとの間に接続され、伝送路を介して入力される差動入力信号RXP/RXNの基準電圧を変換した差動出力信号OUTP/OUTNを出力する変換部101と、VDDまたはGNDと変換部101との間に接続され、差動入力信号RXP/RXNの伝送路により減衰した周波数成分を補正するイコライザ部102と、を備えるものである。

(もっと読む)

電子機器

【課題】基板接続用のスロット位置の変更等によって伝送距離が変わった場合でも、必要なパラメータ設定を比較的簡単に判別し再設定する。

【解決手段】電子回路基板13iがマザーボード10の任意のフリースロットに装着された初期状態で、電子回路基板13iは、監視制御部B4にて送受信回路部B1の受信状態を監視して、当該受信状態が規定状態となるようにパラメータ設定部B3に送受信回路部B1の受信パラメータを変更させ、受信状態が規定状態とならない場合にはその旨をホスト制御基板11に通知する。当該ホスト制御基板11は、スイッチ処理基板12に、電子回路基板13iの受信状態が規定状態となるように送信パラメータの変更を指示する。スイッチ処理基板12の監視制御部C4は、ホスト制御基板11からの指示に応じてパラメータ設定部C3に送受信回路部C1の送信パラメータを変更させる。

(もっと読む)

データリカバリ方法およびデータリカバリ装置

【課題】入力されたシリアル信号のジッタが大きい場合であっても、復調エラーの発生を抑制することができるデータリカバリ方法およびデータリカバリ装置を提供すること。

【解決手段】入力されたシリアル信号が表すデータを復元するデータリカバリ装置を用いたデータリカバリ方法において、シリアル信号をイコライズするイコライジング工程(S1)と、イコライジング工程でイコライズされたシリアル信号をオーバーサンプルするオーバーサンプリング工程(S2)と、オーバーサンプリング工程で得られたオーバーサンプルデータに基づいてイコライジング工程でイコライズされたシリアル信号のパターン長を演算し、演算したパターン長によってイコライズ工程の処理結果を評価する評価工程(S3)と、評価工程における評価結果に基づいてイコライズ工程のイコライズ量を調整するイコライズ量調整工程(S4)とを有する。

(もっと読む)

4値PPM信号の伝送方法及び伝送装置

【課題】データレートを高めることなく、ノイズの影響を低減する。

【解決手段】PPMパルス列の信号に、各PPMパルスとは逆極性の同じパルス幅で所定の振幅を有するパルス列をPPMパルス列の前位置に付け加えた複合信号を用いて伝送を行う。送信信号である(a)の4値PPM信号より、(b)の複合信号を生成する。この複合信号は、各スロットに逆極性の前置パルスを組み合わせる。スロット1に対応する前置パルスがスロット1´であり、このスロット1´は、スロット1と同一パルス幅、波高値はスロット1のM倍、極性は逆極性とする。スロット2〜4及び7も同様に前置パルスであるスロット2´〜4´及び7´を追加する。スロット5及び6は、前置スロットとして2倍のスロット長のスロット5´及び6´を追加する。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

映像信号多重伝送装置およびそれを具備する撮像装置

【課題】映像信号多重デジタル伝送システムのケーブル長が延びたときの伝送波形を改善する。

【解決手段】一つの75Ω伝送路にデジタル映像信号を時分割双方向切換送受する多重伝送装置において、伝送路両側の終端に時分割で双方向を切換えるNMOSバススイッチICを有し、受信側に波形等化器または波形等化器を含む受信器を有し、NMOSバススイッチICの正電源Vccを+3.3Vとし負電源Veeを−1.7Vとし、NMOSバススイッチICの導通抵抗の平均値7Ω分差し引いた75−7=68Ωを終端抵抗値Rzとする。さらに、アナログ切換器の導通抵抗が低い信号波形極性を圧縮する接地されたショトキーバリアダイオードと抵抗の直列接続を有する。

(もっと読む)

受信光信号のクロスポイント検出回路およびそれを用いた光受信装置

【課題】受信光信号のクロスポイントを簡易に検出するクロスポイント検出回路を提供し、検出されたクロスポイント値を用いて光受信装置の電気的波形等化回路や光学的可変分散補償回路を最適制御する光受信装置を提供する。

【解決手段】受信光信号から光電変換された電気信号をAC結合してDC成分を遮断した信号にバイアス電圧を重畳する。バイアス電圧を重畳された信号を自動利得制御増幅回路で増幅し、その出力信号の平均電圧を検出する。また、検出された平均電圧値を用いて電気的波形等化回路のタップ係数を最適制御する。

(もっと読む)

判定帰還型等化器を用いた受信機のためのクロック回復回路

【課題】 本発明は、判定帰還型等化器を用いた受信機のためのクロック回復回路を提供する。

【解決手段】 特定の実施形態では、方法は、判定帰還型等化器(DFE)により、送信データを有する第1の信号を受信し、前記DFEにより、前記送信データを有する等化信号に前記第1の信号を調整し、位相誤り検出器により、前記送信データの4分の1のデータ・レート以下のデータ・レートで位相誤りを検出し、前記位相誤り検出器により、前記検出された位相誤りに基づき位相誤りレベルを生成し、前記DFE及び前記位相誤り検出器のためのクロック回復回路により、前記位相誤りレベルに基づき前記送信データに関連するクロック信号を回復する。

(もっと読む)

伝送回路、プリント回路基板

【課題】搭載する部品を回路毎に変更することなく、伝送経路の特性に合わせて回路の周波数特性を平滑化することのできる、低消費電力の伝送回路を提供する。

【解決手段】本発明に係る伝送回路は、信号伝送線に並列接続されたインダクタを有するパッシブイコライザを備え、インダクタは回路基板のスルーホール側面に形成された導体部分を用いて構成されている。

(もっと読む)

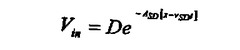

制御可能な減衰と伝播速度とを有する波形を伝送する方法

【課題】波形を伝送する方法を提供する。

【解決手段】制御可能な減衰と伝播速度とを有する波形を伝送する装置と方法とを説明する。例示的な方法は指数波形を生成することを含み、この指数波形は、(a)次の式

で表され、ただし、Dは大きさ、Vinは電圧、tは時間、ASDは減衰係数、vSDは伝播速度であり、(b)最大値で切り欠かれる。例示的な機器は、指数波形発生器と、指数波形発生器の出力に結合する入力記録器と、指数波形発生器の出力に結合するテスト対象の伝送路と、テスト対象の伝送路に結合する出力記録器と、テスト対象の伝送路に結合する別の伝送路と、別の伝送路と接地とに結合する終端インピーダンスとを備える。

(もっと読む)

判定帰還型自動等化器評価装置および判定帰還型自動等化器評価方法

【課題】従来の判定帰還型自動等化器(DFE)の評価装置では、DFEの各タップ係数が実際に最適な値に決定されているのかを個別に客観的に評価することはできなかった。

【解決手段】

既知のデジタル入力信号を受けてDFEから出力されるデジタル信号をDFEの各タップに対応する信号タイミングにおいてサンプリングする信号サンプリング部と、

サンプリングされた前記デジタル信号から各タップ毎にデジタル信号のビット誤り率を測定するビット誤り率測定部とを備える。

(もっと読む)

プログラム可能な、レシーバの等化回路および方法

【課題】伝送媒体によって起こる減衰を好適に補償する等化回路を提供する。

【解決手段】伝送媒体を介して送信されるデータ信号は、その伝送媒体によって起こる減衰をこうむる。等化回路(106)は、直列に配列される複数のステージ(202)を含み、それによって、ステージ(202)の周波数応答を共に統合することを可能にする。各ステージ(202)は、ゼロを挿入するようにプログラム可能であり得、それによって、ステージ(202)の周波数応答の大きさは、20dB/decade大きくなる。ゼロの周波数位置はまた、プログラム可能であり得、それによって、各ステージ(202)が、特定の周波数に対する特定の量のゲインを与えることを可能にする。各ステージ(202)は、高周波ノイズの低減およびクロストーク消去に対する極の位置を決定するようにプログラム可能でもあり得る。

(もっと読む)

受信回路

【課題】補間誤差を低減することができる受信回路を提供することを課題とする。

【解決手段】受信回路は、入力データ信号をクロック信号に基づいてサンプリングしてサンプリング信号を出力するサンプリング回路(201)と、前記入力データ信号に対する前記サンプリング信号の位相情報に基づいて前記サンプリング信号を補間して補間データ信号を出力するデータ補間回路(202)と、前記サンプリング信号と前記位相情報とに基づいて補間誤差を出力する補間誤差判定回路(203)と、前記補間誤差に基づいて設定される等化係数によって前記補間データ信号を等化し、前記等化された補間データ信号を判定して判定信号を出力する判定等化回路(204)と、前記判定信号又は前記等化された補間データ信号に基づいて前記位相情報を生成し、前記データ補間回路及び前記補間誤差判定回路に前記位相情報を出力する位相検出回路(205)とを有する。

(もっと読む)

受信回路

【課題】ビット幅の広いデジタル演算を必要とせずに、小さい回路面積及び消費電力で適応等化処理を実現できる受信回路を提供する。

【解決手段】受信回路は、等化係数に応じた等化処理を受信信号に施して等化された信号を出力する等化回路と、等化された信号と第1閾値との大小関係に応じた0及び1の信号値を有する第1の信号を求め、等化された信号と第2閾値との大小関係に応じた0及び1の信号値を有する第2の信号を求め、第1の信号中に現れる所定の0及び1のパターンの出現回数と第2の信号中に現れる所定の0及び1のパターンの出現回数との差分を計算する誤差計算回路と、差分に応じて等化係数を調整する適応等化制御回路とを含む。

(もっと読む)

信号波形の品質改善方式

【課題】電子計算機およびその周辺機器に接続された通信用ケーブルの長さに応じて、良好な波形品質が確保できるように通信信号の波形を調整する。

【解決手段】通信用ケーブルにケーブルの長さを識別可能なID情報を保存したメモリを内蔵し、電子計算機または周辺機器に搭載された制御用マイコンが通信用ケーブルのID情報を読み出し、読み出したID情報から通信用ケーブルの長さを判別し、通信用LSIを良好な波形品質を得られるように設定する。

(もっと読む)

判定帰還型波形等化器

【課題】直前ビットの受信判定データを利用することなく、第1ポストカーソルのISIを補正する判定負帰還型波形等化器を提供する。

【解決手段】判定帰還型波形等化器は、受信データを入力する増幅回路と、フリップフロップを含み、増幅回路の出力がフリップフロップに入力され、フリップフロップにより増幅回路の出力を判定するデュオバイナリ信号判定器と、フリップフロップに保持された判定結果を逐次シフトさせるシフトレジスタと、シフトレジスタの各出力を入力とし、出力を増幅回路の出力に帰還し、その電位を制御する複数の電流制御ブロックとを有し、フリップフロップに保持された判定結果をシフトレジスタでシフトさせることなく増幅回路の出力の出力に帰還しない。

(もっと読む)

データ伝送装置、システム、方法及びプログラム

【課題】高速伝送を実現するための伝送制御値を効率的に特定すること。

【解決手段】本発明のデータ伝送装置は、高速伝送路を介してデータを伝送するめの伝送制御値における複数の候補値を格納する記憶部と、設定された伝送制御値に基づいて高速伝送路を介してデータを送信する第1のデータ処理回路と、第1のデータ処理回路から高速伝送路を介してデータを受信する第2のデータ処理回路と、記憶部から一の候補値である伝送制御値を取得し、当該取得した伝送制御値を第1のデータ処理回路に設定する設定部と、を備え、第2のデータ処理回路は、第1のデータ処理回路との高速伝送路を介したデータ伝送中にエラーを検出した場合、設定部へ割込み信号を出力し、設定部は、第2のデータ処理回路から割り込み信号を受け取った場合に、記憶部に格納された複数の候補値の中から未取得の伝送制御値を取得し、当該取得した伝送制御値を第1のデータ処理回路に設定する。

(もっと読む)

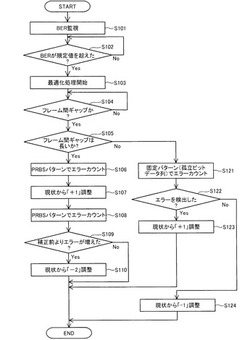

パルスマスク試験機能を備えた伝送システム

【課題】接続線路等の外的要因を考慮して波形整形できるとともに、自局装置と対向局装置が双方向接続されない場合でもパルスマスク試験を行うことを可能にする。

【解決手段】自局装置2は、送信線6a、6bにパルスマスク信号を送出するパルスマスク信号送信部6と、対向局装置3から送信される調整情報に基づいてパルスマスク信号の出力レベルを調整するパルスマスク信号調整部13と、送信線6b又はパルスマスク信号調整部13を第2の接続線路5に選択的に接続するスイッチ部11とを備える。対向局装置3は、受信線21a、21bを介してパルスマスク信号を受信するパルスマスク信号受信部21と、受信したパルスマスク信号をマスクデータと照合するパルスマスク照合部26と、パルスマスク信号の出力レベルの調整量を演算する演算部27と、受信線21b又は演算部27を第2の接続線路5に選択的に接続するスイッチ部30とを備える。

(もっと読む)

受信回路

【課題】消費電力及びノイズを低減することができる受信回路を提供することを課題とする。

【解決手段】入力データをサンプリングすることによりデジタルデータを出力するサンプリング回路(401)と、前記サンプリング回路により出力されたデジタルデータに対して無限インパルス応答フィルタを用いて等化処理を行う等化回路(402)と、前記等化回路により等化処理されたデータの位相を検出する位相検出回路(404)と、前記位相検出回路の出力信号に対してフィルタリングを行う第1のフィルタ(405)と、前記第1のフィルタの出力信号を基に前記無限インパルス応答フィルタのフィードバックするデータのビット数を調整する制御回路(403)とを有する受信回路が提供される。

(もっと読む)

1 - 20 / 131

[ Back to top ]