Fターム[5K029JJ08]の内容

直流方式デジタル伝送 (8,390) | 伝送路との接続部 (350) | 整合;反射波抑圧 (222)

Fターム[5K029JJ08]に分類される特許

21 - 40 / 222

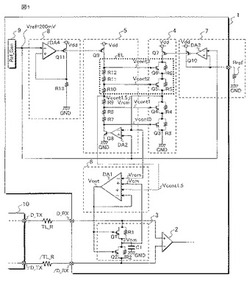

半導体集積回路およびその動作方法

【課題】伝送線路の特性インピーダンスと終端抵抗のインピーダンス整合を容易とする。

【解決手段】差動終端抵抗回路3は直列の第1と第2の素子Q1、Q2を含み、レプリカ抵抗回路4は直列の第3と第4の素子Q3、Q4を含み、制御電圧生成回路5は制御差動増幅器DA2と直列の制御素子Q8と第1と第2の電圧降下回路R7、8;R9とを含む。増幅器DA2の非反転入力と反転入力に、基準電圧Vrefと回路4の素子Q3、Q4のレプリカ抵抗電圧Vrcmがそれぞれ供給される。回路5の第1と第2のレプリカ抵抗制御電圧Vcont0、1は、回路4の素子Q3、Q4の制御入力にそれぞれ供給される。差動終端抵抗回路3の素子Q1、Q2は、第2のレプリカ抵抗制御電圧Vcont1と第2の電圧降下回路R9の電圧降下との合計電圧である差動終端抵抗制御電圧Vcont1.5に基づく制御出力電圧Voutによって制御される。

(もっと読む)

信号波形の品質改善方式

【課題】電子計算機およびその周辺機器に接続された通信用ケーブルの長さに応じて、良好な波形品質が確保できるように通信信号の波形を調整する。

【解決手段】通信用ケーブルにケーブルの長さを識別可能なID情報を保存したメモリを内蔵し、電子計算機または周辺機器に搭載された制御用マイコンが通信用ケーブルのID情報を読み出し、読み出したID情報から通信用ケーブルの長さを判別し、通信用LSIを良好な波形品質を得られるように設定する。

(もっと読む)

プリント回路板

【課題】受動部材にてデエンファシス機能を実現することで、伝送線路で減衰する信号の高周波成分を補正し、符号間干渉によるタイミングジッタを低減する。

【解決手段】送信回路131と伝送線路111との接続点101aに、送信回路131の出力インピーダンス値と伝送線路111のインピーダンス値の並列インピーダンス値以上のインピーダンス値の補正線路113の一端が接続される。補正線路113の他端には、補正線路113のインピーダンス値よりも低い抵抗値の補正抵抗器110が接続される。補正線路113の信号伝播時間をTd、信号の最小のパルス幅をTmin、信号の立ち上がり時間をTrとしたとき、信号伝播時間Tdが0.5×Tr≦Td≦0.5×Tminの条件を満たすように、補正線路113の長さが設定されている。

(もっと読む)

電気回路、差動信号送信装置および差動信号受信装置

【課題】ディファレンシャルモードおよびコモンモードのインピーダンスが異なる差動配線を接続する場合に、双方のモードにおけるインピーダンスを共に整合させること。

【解決手段】本発明の実施形態に係る電気回路は、送信回路から出力される差動信号を伝送する2本の配線を有する第1差動配線と、差動信号を受信回路に伝送する2本の配線を有しディファレンシャルモードインピーダンスおよびコモンモードインピーダンスが第1差動配線より小さい第2差動配線とを接続し、第1差動配線および第2差動配線のディファレンシャルモードインピーダンスおよびコモンモードインピーダンスを共に整合させるように抵抗体が配置された接続部を具備する。

(もっと読む)

受信回路、信号伝送回路、及び信号受信方法

【課題】単相で振幅が小さいクロック信号を的確に検出可能な受信回路を提供する。

【解決手段】受信回路は、第1端と第2端との間をAC結合するAC結合回路22と、第1端に印加される第1の信号に応じて第2端に現れる第2の信号をローパスフィルタリングして第3の信号を生成するローパスフィルタ回路23,25と、第2の信号と第3の信号とが入力されるコンパレータ21とを含む。

(もっと読む)

アダプタ装置および伝送路評価システム

【課題】パッド付の伝送路の伝送特性についての評価装置による評価を可能にする、評価装置に接続されるアダプタ装置およびこれを備える伝送路評価システムを実現する。

【解決手段】アダプタ装置1は、伝送路DUTにおける入力端信号から試験信号の反射損失を抽出して拡大した拡大反射損失信号を生成する反射損失抽出手段11と、伝送路DUTにおける出力端信号から試験信号の通過損失を抽出して拡大した拡大通過損失信号を生成する通過損失抽出手段12であって、第1のしきい値より大きい信号レベルを有するかあるいは第2のしきい値より小さい信号レベルを有する拡大通過損失信号については信号レベルを圧縮して出力し、第2のしきい値より大きく第1のしきい値より小さい信号レベルを有する拡大通過損失信号はそのまま出力する通過損失抽出手段12と、試験信号から拡大反射損失信号および拡大通過損失信号を減算して評価信号を生成する評価信号生成手段13と、を備える。

(もっと読む)

通信ネットワーク

【課題】簡易な構成でありながら、伝送路あるいは分岐路に接続される電子制御ユニットの間の信号の波形歪みを解消するようにした通信ネットワークを提供する。

【解決手段】ECU14a(第1電子制御ユニット)と、ECU14b(第2電子制御ユニット)と、ECU14a,14bを接続するバス(伝送路)16と、バス16から分岐される分岐路20に接続されてECU14a,14bの少なくともいずれかと通信可能なECU14c(第3電子制御ユニット)とを有すると共に、ECU14a,14bはバス16の特性インピーダンスに応じた終端回路22で終端される通信ネットワーク10において、前記分岐路20に導線(スタブフィルタ)24を一端で接続すると共に、前記導線24の他端を開放する。

(もっと読む)

差動通信装置

【課題】伝送される信号のレベルがハイレベルからローレベルに切り替わった後に発生するリンギングのプラス側への振幅を、伝送信号のハイレベル未満の所定の波高値に抑制する。

【解決手段】伝送信号のレベルがハイレベルからローレベルに切り替わったことが検出されたときに、第1トランジスタ52及び第2トランジスタ56により、所定時間だけ、2本の伝送線BP,BM間を、高電位伝送線BPから低電位伝送線BMに向かう方向を順方向とするダイオード60を介して接続する。このため、リンギングにより高電位伝送線BPの電位が低電位伝送線BMの電位よりもある程度大きくなると、その電位差がダイオード60の順方向降下電圧を超えた時点で、ダイオード60がオンする。その結果、リンギングのプラス側の波高値をダイオード60の順方向降下電圧に制限することができる。

(もっと読む)

通信装置

【課題】反射歪みの補正を行う際の補正処理時間間隔および補正処理対象時間範囲を、伝送路の信号伝播状態に応じて最適に制御することにより、回路規模の小型化や演算量の効率化を図る。

【解決手段】複数の通信装置が伝送路を介して接続される通信システムで用いられる通信装置であって、複数の通信装置が接続されることにより生じる信号波形の反射歪みを、既知の信号波形の送信に基づいて推定した反射歪み特性に基づいて補正する反射歪み補正手段と、上記反射歪み補正手段による補正処理を行うための補正処理時間間隔および補正処理対象時間範囲を上記伝送路の信号伝播状態に応じて制御する反射歪み補正制御手段とを備え、上記反射歪み補正手段は、上記反射歪み補正制御手段により決定された上記補正処理対象時間範囲内で、上記補正処理時間間隔毎に、上記信号波形の反射歪みを補正することを特徴とする。

(もっと読む)

絶縁型信号伝送装置

【課題】直流電流信号を一方向に絶縁伝送する絶縁型信号伝送装置において、交流通信信号を双方向に適切に絶縁伝送できるようにする。

【解決手段】直流電流信号を検出する電流検出抵抗を含み、検出された直流電流信号を一方向に絶縁伝送する直流信号経路を備えた絶縁型信号伝送装置であって、直流電流信号を遮断し、絶縁トランスによって交流通信信号を双方向に絶縁伝送する通信信号経路と、電流検出抵抗と通信信号経路との間に設けられたインダクタ部材とを備えた絶縁型信号伝送装置。インダクタ部材は、巻線コイルあるいは半導体回路で構成することができる。

(もっと読む)

入出力回路、半導体制御システム、および入出力回路の制御方法

【課題】デジタル信号を高速で送受信するための入出力回路を、EM耐性を保ちつつ、小さな回路面積で、実現する。

【解決手段】出力バッファ21は、電源−グランド間に接続されたトランジスタTP1,TN1と、ノードn1と入出力端子23との間に接続された抵抗素子R1とを備え、出力バッファ22は、電源−グランド間に接続されたトランジスタTP2,TN2と、ノードn2と入出力端子23との間に接続された抵抗素子R2とを備えている。信号入力モードにおいて、出力バッファ21,22によって1つの終端回路を構成する。例えば、トランジスタTP1,TN2をON、トランジスタTN1,TP2をOFFにし、抵抗素子R1,R2を通る電流パスを形成する。

(もっと読む)

ノイズ対策回路

【課題】送,受信装置の動作に必要な差動信号とコモン信号を伝送して、コモンモードノイズのみを低減させることができるノイズ対策回路を提供する。

【解決手段】ノイズ対策回路1−1を2つのフィルタ回路2,3で構成した。フィルタ回路2(3)は、逆方向に巻回されたコイル25(35),26(36)を有し、コイル25,26(35,36)の両端が、入力端子21,22(31,32)と出力端子23,24(33,34)とに接続されている。フィルタ回路2(3)にディファレンシャルモード電流が流れると、高インピーダンスになり、コモンモード電流が流れると、低インピーダンスになる。フィルタ回路2を差動伝送路100に接続し、フィルタ回路3をフィルタ回路2とグランド線路110とに接続した。そして、フィルタ回路3の出力側をグランド領域120に接続した。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

インターフェイス装置

【課題】インピーダンスの不整合による終端反射の影響を軽減し、良好な信号伝達特性を確保する。

【解決手段】信号伝送経路20の受信経路から送られてくる信号を受信する受信回路1と、受信経路を終端するインピーダンス値可変の受信用可変インピーダンス素子2と、受信信号を4つ以上の閾値電圧に基づきレベル弁別するレベル弁別回路3と、レベル弁別回路3の検出結果から各弁別レベルごとの期間を算出するレベル別期間算出回路4と、レベル別期間算出回路4による弁別レベルごとの期間の大小比較に基づいて受信用可変インピーダンス素子2のインピーダンス値を調整するインピーダンス値調整回路5とを備える。

(もっと読む)

電子回路装置

【課題】信号の遅延時間を調整することにより、インピーダンス不整合によって発生するディターミニスティックジッタを低減することが可能な電子回路装置を提供することを目的とする。

【解決手段】本発明の代表的な構成は、高速シリアル伝送により伝送路106を通じてドライバ104からレシーバ108へ信号を伝達する電子回路装置100であって、伝送路106上のインピーダンス不整合点の上流側または下流側の近傍に、このインピーダンス不整合点のキャパシタンスとの間で遅延回路を構成するインダクタ112、LC回路114またはLCR回路を備えていることを特徴とする。

(もっと読む)

多重反射補償回路

【課題】一つのドライバから、複数の負荷までの途中まで1本の線で配線し、途中から分岐して複数の負荷に分配する、いわゆるトーナメント方式と呼ばれる信号の伝送方法は、複数の異なる特性インピーダンスの線路を縦続接続した等価回路に置き換えられ、多重反射による極めて複雑な波形乱れを生じるが、多重反射の原因を解明し、回避する方法を見つけることができれば、簡単かつ高品質の波形を得ることができる。

【解決手段】複数の異なる特性インピーダンスの線路を縦続接続した際の伝達関数は、複雑で、その逆関数は数学的には求まっても、実際の回路に適用することは一見困難にみえる。ところが、この逆関数は、元の信号ν10(t)に対して、例えば、[数8]のような簡単な時間遅れと重みを加えた加減算のみで表される簡単な式であり、平坦な周波数特性、さらには、乱れのない波形伝送を行えることが分かった。

(もっと読む)

制御装置及び方法、並びに信号処理装置

【課題】信号処理部が備える波形整形機能に対して、使用環境の変化に応じて適切な設定を行う。

【解決手段】制御装置は、筐体)内に実装された信号処理部であって且つ入力された信号に対する波形整形処理を行う波形整形部を備える信号処理部を制御する制御装置であって、(i)信号処理部の実装状態を示す実装情報、(ii)信号処理部の温度を示す温度情報、及び(iii)信号処理部に固有の特性を示す処理部特性情報を取得する取得手段と、実装情報、温度情報及び処理部特性情報に基づいて、波形整形部における波形整形特性を調整する調整手段とを備える。

(もっと読む)

半導体集積回路装置、インタフェース回路

【課題】EMIを低減する半導体集積回路、インタフェース回路を提供する。

【解決手段】半導体集積回路装置(100)は、抵抗値を切り替え可能な可変抵抗部(10)と、可変遅延部(20)と、データ取り込み部(26)とを具備する。抵抗値を切り替え可能な可変抵抗部(10)は、入力されるデータ信号(DT)をダンピングする。可変遅延部(20)は、データ信号(DT)の入力タイミングを示すクロック信号(CLK)に変更可能な遅延を与える。データ取り込み部(26)は、可変抵抗部(10)によってダンピングされた信号から可変遅延部(20)によって遅延された遅延クロック信号によって示されるタイミングでデータを取り込む。

(もっと読む)

誘導雷が原因の過電圧の抑制

直流電圧フリーかつ差動の、EIA−485/EIA−422準拠の、TTPプロトコルに従った信号伝送を備えたフィールドバスのバスライン(102)へのバス接続ユニット(101)のための結合回路であって、バス接続ユニット(101)の送信/受信コンポーネント(104)の両方の入力部/出力部(108、109)が信号発信装置(103)の第一のコイルと、およびバスライン(102)の両方の極が信号発信装置第二のコイルと、接続されており、第一のコイルが中心タップ(107)を備え、この中心タップ(107)がバス接続ユニット(101)のローカル規準ポテンシャルとコンデンサー(105)とを接続しており、このコンデンサーの容量が少なくとも発信装置(103)の寄生容量(110)の100倍である結合回路。 (もっと読む)

半導体集積装置、及びその調整方法、並びに終端抵抗調整回路

【課題】第1の伝送路及び第2の伝送路間のDuty比の高精度化を実現できる終端抵抗調整回路、及び半導体集積回路を提供する。

【解決手段】本発明に係る終端抵抗調整回路71は、差動入力信号の第1及び第2の伝送路21、22それぞれに挿入され、制御信号に応じて抵抗値が調整される終端抵抗郡1,2と、第1及び第2の伝送路21、22の内、少なくともいずれかの伝送路であって、終端抵抗郡1,2の後段に挿入され、終端抵抗郡1、2を介して接続する伝送路の電位の調整を行う可変抵抗郡3と、可変抵抗郡3の後段、若しくは、当該可変抵抗郡3が配設されていない場合には終端抵抗郡1,2の後段に挿入され、第1及び第2の伝送路21、22の電位差を比較する比較器4と、比較結果に基づいて可変抵抗郡3の抵抗値を制御することによって伝送路の電位を調整する伝送路電位調整部5と、を備える。

(もっと読む)

21 - 40 / 222

[ Back to top ]