Fターム[5K029JJ08]の内容

直流方式デジタル伝送 (8,390) | 伝送路との接続部 (350) | 整合;反射波抑圧 (222)

Fターム[5K029JJ08]に分類される特許

141 - 160 / 222

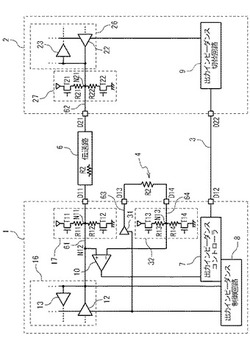

出力インピーダンス調整回路、半導体装置及び出力インピーダンス調整方法

【課題】OCD機能を有する半導体集積回路に対して、外部伝送路のシリーズ抵抗の有無に関わらず、OCD機能を実現する。

【解決手段】比較回路30と、インピーダンス制御回路32とを具備する出力インピーダンス調整回路を用いる。比較回路30は、第1伝送路24−36−39の第1出力と第1伝送路を模擬する第2伝送路41−25−40の第2出力とを比較する。ここで、第1伝送路は、外部半導体集積回路2に設けられ、出力インピーダンス調整対象の第1出力回路24を含む。第2伝送路は、設定された出力インピーダンスを有し、第1出力回路24を模擬する第2出力回路41を含む。インピーダンス制御回路32は、比較回路30の比較結果に基づいて、第1出力と第2出力とが等しくなるように、第1出力回路24の出力インピーダンスを調整する制御信号を外部半導体集積回路2へ出力する。

(もっと読む)

帯域幅制限負荷用のトライステートドライバ

CMOS駆動回路が所定の回数の同値データビットが伝送された後に、トライステート状態を提供するように構成され、伝送チャネルに沿った符号間干渉(ISI)の存在を低減させる。伝送チャネルが帯域制限される場合、トライステート技術の使用が所定のビット期間中の供給線路への完全な移行を可能にする。 (もっと読む)

差動通信ネットワーク

【課題】本発明は、差動通信ネットワークに関し、差動通信においてコモンモードノイズによる影響をできるだけ簡易な構成で小さく抑えることにある。

【解決手段】複数のノード10を互いに接続する差動通信線路12の各相導体12a,12b間に、差動通信線路12を介したノード10間での通信がコモンモードノイズにより妨害されるのを低減するフィルタ回路30を挿入する。そして、フィルタ回路30を、差動通信線路12への挿入位置近傍にあるノード10の各相の不平衡を補償すべく、両導体12a,12b間で対称となるように、導体12a,12bとボデーグラウンド14との間で互いに直列接続された、コモンモードノイズの周波数帯域でインピーダンスを小さくするインピーダンス回路32,34と、ノード10の内部インピーダンスよりも十分に小さいインピーダンスを有するインピーダンス回路36と、から構成する。

(もっと読む)

終端負荷設定装置、プリント基板及び情報再生装置

【課題】プリント基板上の配線パターンから放射される電磁波ノイズを効果的に低減する。

【解決手段】終端負荷設定装置9(コンピュータ92のCPU922)は、予め設定された複数の抵抗値の内、予め設定された順に1の抵抗値を選定し、選定された抵抗値を有する抵抗を終端負荷として接続して、プローブ91を介して電磁波ノイズを検出する検出部922aと、スペクトラムアナライザ93に対して測定結果の周波数分析を実行させる周波数分析部922bと、予め設定された特定の周波数(=クロック信号の3倍の周波数)のゲインを最小とする抵抗値を、配線パターンに接続する終端抵抗の抵抗値として求める抵抗値算出部922cとを備えている。

(もっと読む)

情報処理システム、情報処理装置、インピーダンス調整方法及びプログラム

【課題】 従来の技術によると、固定的な外部抵抗によりインピーダンスを調整しているので、配線のインピーダンス特性のばらつき等の種々の要因に基づく信号伝送経路のインピーダンス特性のばらつきに対応できないという問題がある。

【解決手段】 上記課題を解決するため、本発明の情報処理システムは、伝送経路で発生したエラー数を検出及び計数し、当該エラー数を出力インピーダンスの調整にフィードバックさせる構成を備えることを特徴とする。

(もっと読む)

半導体送受信装置システム、メモリカードおよびメモリカードホスト機器

【課題】インピーダンス調整、ドライブ能力調整の柔軟性があり、かつ高速な信号伝送が可能な半導体送受信装置システムを小面積にて得ること。

【解決手段】双方向に信号の送受信を行なう半導体送受信装置システムであって、1つのマスター半導体送受信装置と少なくとも1つのスレーブ半導体送受信装置で構成され、前記マスター半導体送受信装置、前記スレーブ半導体送受信装置ともに信号の送受信を行なうための送信回路と受信回路と、伝送線路とのインピーダンスの整合を図る終端回路を具備し、前記マスター半導体送受信装置のみに信号駆動用の電流源を持たせる構成とした。

(もっと読む)

リモートIOシステムおよびマスタ並びにスレーブ及び中継器並びに終端器

【課題】 クロストーク対策が施されていないフィールドバス用の通信ケーブルを用いても通信速度の速い伝送を可能としたリモートIOシステムを提供すること

【解決手段】 フィールドバスを介して接続されるマスタユニット10とスレーブ20との間で制御データを送受し、スレーブの駆動電源はフィールドバスを構成する通信ケーブル6経由で供給される。通信ケーブルは、電力供給するための通信電源線6aと、制御データを送受するための通信信号線6bとを備える。マスタと、スレーブと、通信ケーブルの終端に接続される終端器30と、リピータ40の内部に、通信電源線の+/−のライン間に接続される整合回路50〜53を設けた。この整合回路は、通信電源線と通信信号線間に発生するクロストーク成分を減らすように設定される。

(もっと読む)

終端抵抗調整方法、半導体集積回路及び半導体装置

【課題】本発明は、終端抵抗調整方法、半導体集積回路及び半導体装置に関し、半導体装置内の終端抵抗を最適な抵抗値に設定するためのキャリブレーションを正確に行うことを目的とする。

【解決手段】第1のノードと電源電圧及び接地電圧の一方との間に接続された電流源回路と、第1のノードと電源電圧及び接地電圧の他方との間に並列接続可能に設けられた複数の第1の抵抗を備えたモニタ用抵抗部と、第2のノードと前記他方との間に並列接続可能に設けられた複数の第2の抵抗を備えた終端抵抗部と、第1のノードの電圧と基準電圧とを比較して比較結果を出力する比較回路と、キャリブレーションを行う時には、比較結果に基づいてモニタ用抵抗部の第1の抵抗を選択的に並列接続する制御部と、第2のノードに接続された外部端子とを備え、終端抵抗部の抵抗値を制御する時には、制御部は比較結果に基づいて終端抵抗部の第2の抵抗をモニタ用抵抗部の第1の抵抗と同様の構成に選択的に並列接続するように構成する。

(もっと読む)

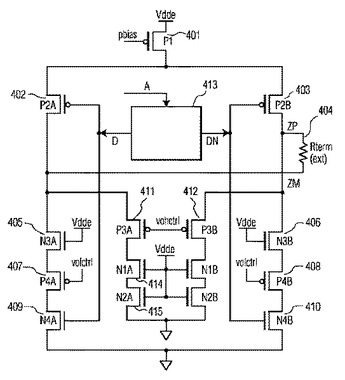

出力インピーダンスを整合した低電圧で低消費電力の差動ドライバ

本発明は、差動データ入力端と、前記差動データ入力端に依存する電流をステアリングするための電流源に結合した複数のスイッチと、少なくとも複数のスイッチのうちの2つと結合している第1の差動出力端および出力インピーダンスを制御するための第2の差動出力端と、前記第1の差動出力端および前記第2の差動出力端に結合される第1のソースフォロワおよび第2のソースフォロワとを具える、差動信号を駆動するためのシステムおよび方法を提供する。このアーキテクチャは、前記ドライバから反射したコモンモード雑音が差動信号になることを防止し、1.62V以下までのLVDSおよびサブLVDS規格の要件を満足する。またこのアーキテクチャは、Gbpsレンジで動作することが可能であり、極めて低い消費電力で高速差動ドライバとなる。  (もっと読む)

(もっと読む)

出力バッファ回路と差動出力バッファ回路並びに伝送方法

【課題】プリエンファシス機能を有する出力バッファ回路の出力インピーダンスを、調整可能なプリエンファシス量とプリエンファシスタップ数、及び動作タイミングに依らず一定で、伝送線路の特性インピーダンスと整合して出力バッファの出力端子で再反射することなく、高速動作可能な出力バッファ回路を提供する。

【解決手段】インバータ1〜3と、一定の時間遅延させる遅延回路1〜3と、バッファ1〜3とを備え、伝送径路に論理信号を送信し、伝送径路の信号減衰量に応じて、送信側で4種以上の信号電圧を有する波形を生成する機能を有する出力バッファ回路で、プリエンファシス量を可変とし、バッファのオン抵抗Rsを一定とする。バッファの前段にセクレタ回路1〜3を有し、インバータは、セレクタ論理によりバッファに入力する信号を選択可能で、データ信号を反転し、セレクタ論理のセレクト信号により、プリエンファシス量とプリエンファシスタップ数を調整する。

(もっと読む)

バックボード伝送方法、バックボード伝送装置及び基板ユニット

【課題】高速度のバックボード伝送において、コネクタ部分でのインピーダンス不整合による反射波の影響を除去し、パルスを正確に受信し、ビットを正確に判別可能とするバックボード伝送方法、バックボード伝送装置及び基板ユニットを提供する。

【解決手段】本発明のバックボード伝送方法は、基板ユニット間で受け渡される信号波と同一特性のキャンセル波生成用信号波をモニタし、該信号波に対する反射波の遅延時間及び利得を検出する信号波モニタ工程と、信号波モニタ工程で検出された遅延時間に基づいてキャンセル波生成用信号波の遅延調整を行う遅延調整工程と、信号波モニタ工程で検出された利得に基づいてキャンセル波生成用信号波の利得調整を行う利得調整工程と、遅延調整工程及び利得調整工程によるキャンセル波生成用信号波の波形調整により生成されたキャンセル波を信号波に重畳して反射波をキャンセルする反射波キャンセル工程とを含んだ。

(もっと読む)

信号伝送装置及び画像形成装置

【課題】データバスで通信されるパラレル信号に対して、シリアルに変換しLVDSによる双方向伝送を行うことで、低ノイズの長距離伝送を実現する。

【解決手段】信号伝送装置は、LVDSドライバ1、LVDSレシーバ2、パラレル/シリアル変換部3及びシリアル/パラレル変換部4を備える。そして、ドライバ/レシーバコントロール信号9が各部に入力されて作動が制御されることにより、信号送受信の機能の切替えを行い、双方向の信号伝送を実行する。

(もっと読む)

半導体集積回路および無線通信用半導体集積回路

【課題】クロック信号を必要とする回路ブロックと、低雑音受信特性を必要とする回路ブロックが同一チップ内に配置しても、所望の受信特性を確保することができる半導体集積回路の技術を提供する。

【解決手段】クロック信号を必要とするPLL130、低雑音受信特性を必要とするLNA20などを有する無線通信用半導体集積回路を適用したダイレクトコンバージョン方式の受信回路において、PLL130の入力段のクロック信号バッファ110と120の間に可変結合線路180が設けられ、クロック信号の高調波の周波数における可変結合線路180とLNA20の入力端子、GND端子の結合を等しくする。LNA20の入力端子、GND端子が同位相で励起されるのであれば、LNA20の出力には何も出力されないので、LNA20の出力はクロック信号高調波は存在しない。

(もっと読む)

半導体集積回路

【課題】外部寄生抵抗の抵抗値に応じて、プログラマブルに外部から終端抵抗の抵抗値を調整し、高精度のインピーダンス整合を実施することが可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路100は、電源Vccに接続された電流回路3、この電流回路3と接地との間に接続され電流回路3が出力する主電流Iが入力される可変抵抗4、この可変抵抗4の電位と第1の基準電位Vref1とを比較し信号を出力するコンパレータ回路5、および、コンパレータ回路5の出力信号に基づいて可変抵抗4の抵抗値を制御する制御回路6、を有する終端抵抗調整回路1と、電源Vccと可変抵抗4との間に接続され、終端抵抗と伝送線路との間の外部寄生抵抗の抵抗値に応じた外部信号Sに基づいて可変抵抗4に付加電流Iadを出力する付加電流調整回路2と、を備える。

(もっと読む)

信号伝送装置

【課題】信号伝送装置に関し、クロストークにより発生する信号のエッジ部の時間的な揺らぎを抑制することを課題とする。

【解決手段】複数の信号を送信する送信部と、複数の信号を受信する受信部と、送信部から出力された複数の信号をそれぞれ受信部へ伝送する複数の配線を収容したケーブルと、信号を遅延させる少なくとも2つの遅延部とを備え、第1の遅延部が、前記送信部と、第1の信号を伝送するケーブル内の第1の配線との間に配置され、第2の遅延部が、第2の信号を伝送するケーブル内の第2の配線と前記受信部との間に配置され、前記ケーブルの第1の配線と前記ケーブルの第2の配線との伝播遅延時間が等しく、前記第1の遅延部と第2の遅延部との信号遅延時間が等しく、第1の信号と第2の信号とが遅延部の遅延時間分ずれたタイミングでケーブル内を伝送されることを特徴とする。

(もっと読む)

構成可能なオンダイ終端

記載されるのは、2つ以上の終端トポロジからユーザが選択できるようにする構成可能なオンダイ終端要素を用いるシステムである。1つのトポロジは、レールツーレールまたは半電源終端をサポートするようにプログラム可能である。別のトポロジには、固定または可変フィルタ要素が選択的に含まれ、それによって、終端特性は、異なるレベルの速度性能および電力消費に対して調整可能になる。終端電圧およびインピーダンスもまた調整可能である。  (もっと読む)

(もっと読む)

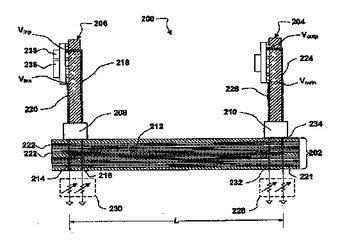

バックプレーン信号チャネルにおけるインピーダンス整合のための装置及び方法

前面及び裏面を有し、その中で複数の導電層を有し、各導電層は1又はそれ以上の信号チャネルを有するプリント回路基板と、前面から裏面へ延在し、少なくとも1つの信号チャネルへ電気的に結合されるスタブと、スタブ及び接地へ電気的に結合されるインピーダンス整合端子とを有する装置を開示する。前面及び裏面を有し、且つ、1又はそれ以上の信号チャネルを各々有する複数の導電層と、前面から裏面へ延在し、少なくとも1つの信号チャネルへ電気的に結合され、当該プリント回路基板へ取り付けられる部品から信号を受信するよう設計されるスタブとを有するプリント回路基板を設ける段階と、スタブ及び接地へインピーダンス整合端子を結合する段階とを有する処理を開示する。  (もっと読む)

(もっと読む)

双方向伝送装置および双方向伝送方法

【課題】高速化に対応した双方向伝送系を提供する。

【解決手段】入出力回路100と、入出力回路200と、回路100および回路200を結ぶ双方向伝送路300とで構成される双方向伝送系において、伝送路300に接続される回路200の入力端には可変インピーダンス回路21が設けられる。第1の伝送情報(回路100の出力信号)は電圧信号E11として回路100から伝送路300を介して回路200へ送られ、第2の伝送情報(可変インピーダンス回路21のインピーダンス制御信号S21)は電圧信号E21として回路200から伝送路300を介して回路100へ送られる。ここで、第2の伝送情報S21が、可変インピーダンス回路21の回路インピーダンスZの変更に対応した電圧信号E21の変化として、回路100へ伝送される。

(もっと読む)

送信回路、データ転送制御装置及び電子機器

【課題】出力信号の振幅を調整可能にする送信回路、データ転送制御装置等の提供。

【解決手段】送信回路は、電源AVDDとノードNDとの間に設けられた定電流回路10と、ノードNDと信号線DPとの間に設けられたスイッチ素子SW1と、ノードNDと信号線DMとの間に設けられた第2のスイッチ素子SW2と、定電流回路10から流れる電流の値を可変に制御する電流制御回路20を含む。電流制御回路20により可変に制御される電流により、スイッチ素子SW1、SW2を介してDP、DMを駆動する。出力ハイレベル電圧の最小値をvminとし最大値をvmaxとし、送信側、受信側の終端抵抗値をrt、rrとし、定電流回路10から流れる電流の値をihsとした場合に、{(rt+rr)/(rt×rr)}×vmin≦ihs≦{(rt+rr)/(rt×rr)}×vmaxを満たす範囲に、電流範囲が設定される。

(もっと読む)

伝送システムの分岐器並びに伝送システム

【課題】従来例に比べてインピーダンスの低下が補償できる範囲を拡大して分岐数の増減が容易に行える伝送システムの分岐器並びに伝送システムを提供する。

【解決手段】分岐器3は、幹線2に接続される各一対の第1の接続端子10と、分岐線2’が接続される一対の第2の接続端子11と、第1の接続端子10と第2の接続端子11との間に挿入され、幹線2に対して分岐線2’を高インピーダンスとするインピーダンス変換部12とを備えている。インピーダンス変換部12における抵抗値が幹線2に挿入される分岐器3の台数に応じた最適な値となるように切替スイッチSW1,SW2を切り替えて選択することができる。そのため、分岐器における抵抗値が固定であった従来例に比べて、分岐器3を挿入したことによるインピーダンスの低下が補償できる範囲を拡大し、分岐数の増減が容易に行える。

(もっと読む)

141 - 160 / 222

[ Back to top ]