Fターム[5K029LL08]の内容

直流方式デジタル伝送 (8,390) | 基本回路 (285) | 遅延回路;単安定マルチ (67)

Fターム[5K029LL08]に分類される特許

1 - 20 / 67

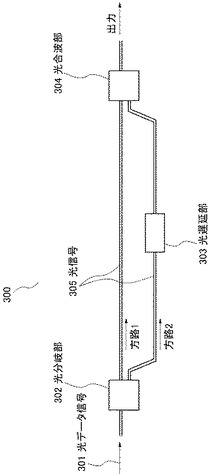

光回路及び波形整形方法

【課題】

データ伝送における伝送帯域を拡大するという課題を解決するための技術を提供する。

【解決手段】

本発明の光回路は、光信号を分岐する光分岐部と、光分岐部で分岐された光信号の少なくとも1つに第1の遅延及び位相変化を与える第1の光遅延部と、光分岐部で分岐された光信号と第1の光遅延部を通過した光信号とを結合させる第1の光結合部と、を備え、位相変化は、第1の光結合部において結合される少なくとも2つの分岐された光信号の間にφ+2nπ(π/2<φ<3π/2、nは0以上の整数)の位相差を与える。

(もっと読む)

伝送装置及びネットワークシステム

【課題】TDMデータをパケット化し伝送するネットワークシステムにおいて、パケットネットワーク上で発生する遅延変動を吸収するために、伝送装置内に具備した遅延変動吸収バッファにユーザデータを格納している時間を最適化し、エンド・ツー・エンドでの遅延時間によるリソースの過剰消費を抑止する。

【解決手段】伝送装置1は、TDMネットワーク7から受信したTDMフレームをパケット化してパケットネットワーク8へ送信し、また、パケットネットワーク8から受信したパケット信号をTDM化して前記TDMネットワークへ送信するものであり、パケットネットワーク上の伝送遅延時間を測定する手段106〜108、113と、測定した遅延時間から遅延変動時間を算出する手段109と、算出した遅延変動時間に基づいて、パケットネットワーク8から受信した信号をTDM化してTDMネットワークに送信するまでの時間を制御する手段112とを備える。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

光受信方法、光受信装置及びビート雑音推定器

【課題】本発明は、ビットパターンのゆらぎによる影響を小さくすることにより、ビート雑音推定器の推定誤差を小さくすることができる技術を提供することを目的とする。

【解決手段】本発明のビート雑音推定器13は、光電変換器11が出力する受信電気信号91に時間遅延を与える遅延子21と、遅延子21が時間遅延した受信電気信号91から最尤判定器12が出力する信号成分推定値92を減算して受信電気信号91から信号成分を除去した雑音信号95を出力する減算器22と、減算器22が出力する雑音信号95と最尤判定器12が出力する信号成分推定値92との相関関係から算出した補正前のビート雑音推定値を、最尤判定器12が出力するビート雑音推定対象である複数の信号成分についての信号成分推定値92の乗算値から算出した擬似的なビート雑音推定値で補正した値を、補正後のビート雑音推定値93として出力する相関器23と、を備える。

(もっと読む)

駆動回路および光送信装置

【課題】駆動対象の応答特性を柔軟に補償すること。

【解決手段】駆動回路100は、分岐部110と、遅延部121,122と、増幅器131,132と、合成部140と、を備えている。分岐部110は、駆動信号を分岐する。遅延部121,122は、遅延量が可変の可変遅延部を含み、分岐部110によって分岐された各駆動信号をそれぞれ遅延させる。増幅器131,132は、各駆動信号のうちの一部の駆動信号を反転させる。合成部140は、遅延部121,122および増幅器131,132の後段に設けられ各駆動信号を合成する。

(もっと読む)

エレベータの信号伝送装置

【課題】直列伝送信号が時間軸に対して歪んだとしても、正しくデータを受信することができるレベータの信号伝送装置を提供する。

【解決手段】直列伝送信号の最初のビット以外の特定のビットが直前のビットと異なるレベルに緩やかに移行する場合に、親局によるサンプリング位置での特定のビットの値が異なるレベルと認識される値となるように、残りのビットの時間幅を維持しつつ、最初のビットの時間幅を狭くして、複数のビットを連続的に並べて親局へ送信するようにした。

(もっと読む)

高速送信器ドライバ回路のための構成可能なエンファシス

【課題】シリアルデータ信号において、シリアルデータ信号内の直前のビットのデータ値とは異なる各ビットにプレエンファシスを与える回路を提供すること。

【解決手段】シリアルデータ信号において、該シリアルデータ信号内の直前のビットのデータ値とは異なる各ビットにプレエンファシスを与える回路であって、該回路は、各次のビットのデータ値を示す方向に回路要素内に第1の電流を流す第1の回路と、1つのビットが、該1つのビットの直前にあるビットと同一のデータ値を有する条件に応答して、該第1の電流とは反対の方向に該回路要素内において流れるように第2の電流を流す第2の回路と、該回路要素における正味の電流の量および方向に基づいて、シリアルデータ出力信号を生成する第3の回路とを備える、回路。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

電子回路装置

【課題】信号の遅延時間を調整することにより、インピーダンス不整合によって発生するディターミニスティックジッタを低減することが可能な電子回路装置を提供することを目的とする。

【解決手段】本発明の代表的な構成は、高速シリアル伝送により伝送路106を通じてドライバ104からレシーバ108へ信号を伝達する電子回路装置100であって、伝送路106上のインピーダンス不整合点の上流側または下流側の近傍に、このインピーダンス不整合点のキャパシタンスとの間で遅延回路を構成するインダクタ112、LC回路114またはLCR回路を備えていることを特徴とする。

(もっと読む)

無線通信装置

【課題】変調効率が高い無線通信装置を提供することを課題とする。

【解決手段】無線通信装置は、ベースバンド信号生成器により生成されたNビットのデジタルデータに応じて、クロック発生器により生成された2N個のパルス信号のうちの1個のパルス信号を選択するセレクタと、セレクタにより選択されたパルス信号のパルス幅を短くする短パルス発生器と、短パルス発生器によりパルス幅が短くされたパルス信号に含まれる周波数成分の中から通過周波数帯域の周波数成分のみを通過させ、通過周波数帯域以外の周波数成分を減衰させるバンドパスフィルタとを有し、クロック発生器により生成される2N個のパルス信号は、第1のパルス及び第2のパルスを含む全期間非送信パルス(S0)、第3のパルス及び第4のパルスを含む全期間送信パルス(S7)、並びにパルス幅が同じであって位相が異なる2N−2個の一部期間送信パルス(S1〜S6)を含む。

(もっと読む)

受信回路

【課題】エラーの発生率を改善し目標とする発生率にする際の遅延量を低減した受信装置を提供する。

【解決手段】発生確率が時間に応じて正規分布するランダムジッタを含む信号を入力し、この入力信号をデジタルデータに変換して出力する受信装置において、位相を設定可能なクロック信号を生成するクロック回路と、前記入力信号を前記クロック信号に基づくタイミングでデジタルデータに変換して出力するとともに、前記変換の際にエラーが生じた場合にはエラー信号を出力する第1受信回路と、前記入力信号を遅延させた信号を、前記クロック信号に基づくタイミングでデジタルデータに変換して出力するとともに、前記変換の際にエラーが生じた場合エラー信号を出力する第2受信回路と、第1、第2受信回路のエラー信号に基づいて、第1受信回路または第2の受信回路のいずれか一方からのデジタルデータを選択して出力するデータ出力制御部を備えた。

(もっと読む)

半導体集積回路装置、インタフェース回路

【課題】EMIを低減する半導体集積回路、インタフェース回路を提供する。

【解決手段】半導体集積回路装置(100)は、抵抗値を切り替え可能な可変抵抗部(10)と、可変遅延部(20)と、データ取り込み部(26)とを具備する。抵抗値を切り替え可能な可変抵抗部(10)は、入力されるデータ信号(DT)をダンピングする。可変遅延部(20)は、データ信号(DT)の入力タイミングを示すクロック信号(CLK)に変更可能な遅延を与える。データ取り込み部(26)は、可変抵抗部(10)によってダンピングされた信号から可変遅延部(20)によって遅延された遅延クロック信号によって示されるタイミングでデータを取り込む。

(もっと読む)

送信装置および送受信システム

【課題】受信装置において受信エラーが生じる頻度を更に低減することができる送信装置および送受信システムを提供する。

【解決手段】送信装置10は、第1出力部11、第2出力部12、処理部13および記憶部14を備える。処理部13は、送出すべき第1データD(1)および第2データD(2)を受け取るとともに、記憶部14により記憶されている信号線路31,32の線路間干渉特性をも受け取る。処理部13は、信号線路31,32の線路間干渉特性に基づいて、第1データD(1)の値を補正したデータD1(2)を求めるとともに、第2データD(2)の値を補正したデータD1(1)を求める。第1出力部11は、処理部13により求められたデータD1(1)を第1信号線路31へ送出する。第2出力部12は、処理部13により求められたデータD1(2)を第2信号線路32へ送出する。

(もっと読む)

信号伝送装置及び信号伝送方法

【課題】簡易な回路構成で信号のパルス幅やデューティ比を一定に保つことができるよう

にする。

【解決手段】エッジ抽出回路1は、入力パルス信号Dinの立ち上がりエッジ及び立ち下り

エッジを抽出し、抽出した立ち上がりエッジ及び立ち下りエッジを正パルス信号又は負パ

ルス信号のいずれかに統一したパルス信号n2を生成する。これにより、信号伝送回路2

における入力パルス信号Dinの立ち上がりの遅延と立ち下りの遅延による変動を入力パル

ス信号Dinの立ち上がり又は立ち下りで同じ条件にできる。従って、信号伝送回路2にお

ける入力パルス信号Dinの立ち上がりと立ち下がりにおける伝播遅延時間差が生じない。

信号伝送回路2は、エッジ抽出回路1により生成されたパルス信号n2を伝送する。波形

再生回路3は、信号伝送回路2により伝送されたパルス信号n2から波形を再生して出力

パルス信号Doutを得る。

(もっと読む)

デジタル信号伝送システム、送信部および受信部

【課題】差動伝送方式を用いてデジタル信号を伝送する場合に、伝送情報量の更なる向上を可能とするデジタル信号伝送システムを提供する。

【解決手段】送信部と、伝送路と、受信部とからなる。送信部は、入力デジタル信号を、N(Nは3以上の整数)個の2値信号の並列入力信号として受け、全てが同じ2値の値となるのを除いたN個の2値信号の並列出力信号からなる伝送用デジタル信号を出力する第1の演算手段を備える。伝送路は、N個の2値信号のそれぞれを伝送するN本の信号線を備える。受信部は、N本の信号線間に接続される終端抵抗と、N本の信号線の、互いに異なる組み合わせの2信号線間を伝送される2値信号を比較する(N−1)個の差動比較部と、(N−1)個の差動比較部の出力信号から入力デジタル信号を得る第2の演算手段とを備える。

(もっと読む)

データ通信システムおよび該データ通信システムを用いた画像形成装置

【課題】受信側を小型の構成で伝送路によるスキューを補正でき高精度な周波数・位相制御を可能とする。

【解決手段】伝送クロックと、該伝送クロックに同期し任意のビット幅を有する伝送データとを出力するデータ送信手段と、伝送クロックを用いて伝送データをサンプリングすることにより伝送データを受信するデータ受信手段とを備え、データ受信手段は、入力される伝送データと伝送クロックの位相関係から生成される、位相同期しているか否かを示す位相判定信号を、データ送信手段に出力する機能を有し、データ送信手段は、伝送クロックよりも高周波数の高周波クロックを生成するクロック生成部と、高周波クロックを基準として伝送クロックを生成する伝送クロック生成部と、高周波クロックを基準として、位相判定信号に基づいて伝送クロックとの位相誤差を補正した伝送データを生成する伝送データ生成部とを有する。

(もっと読む)

受信装置、駆動装置、画像形成装置

【課題】LVDSレシーバにおける信号ラインの異常を検出することが可能な受信装置、駆動装置、画像形成装置を提供することを目的としている。

【解決手段】LVDSレシーバ110の非反転入力端子T10の電圧と反転入力端子T20の電圧との電位差が、LVDSレシーバ110が正常にデータ伝送を行うことが可能な入力の電位差の範囲において最も小さい電位差未満である状態が一定時間継続した場合を、信号ラインの異常として検出する。

(もっと読む)

ノイズ試験システムおよびノイズ試験方法

【課題】試験用の差動ノイズを差動信号に対して高精度に重畳する。

【解決手段】ノイズ発生器10から発生されたノイズを、ディバイダ20によりポジ側遅延回路31およびネガ側遅延回路32に分配する。ポジ側遅延回路31、ネガ側遅延回路32から出力されるノイズは、結合コンデンサと抵抗とを介して、差動伝送路を構成するポジ側、ネガ側の各信号線に印加される。抵抗の抵抗値は、ポジ側、ネガ側の各信号線の特性インピーダンスより十分高く設定されている。そして、ポジ側遅延回路31およびネガ側遅延回路32の各遅延量は、ノイズ発生器10から発生されるノイズの周波数と、上記の各抵抗を通じて差動伝送路に印加する差動ノイズの振幅とから決定される遅延差を互いに有するように設定される。

(もっと読む)

情報処理装置、及び信号判定方法

【課題】消費電力が少なく、回路規模が小さく、受信側のデータ判定に用いる閾値の設定精度が緩和された情報処理装置を提供すること。

【解決手段】互いに異なる第1及び第2のビット値を含む入力データに対し、第1のビット値を複数の第1の振幅値で表現し、第2のビット値を第1の振幅値とは異なる第2の振幅値で表現し、連続して同じ振幅値をとらず、かつ、一周期毎に振幅値の極性が反転するように符号化された信号を受信する信号受信部と、入力信号を一周期分だけ遅延させて遅延後の信号を遅延前の信号に加算する変換処理を信号受信部により受信された信号に施す変換処理部と、変換処理の逆処理を変換処理部から出力された信号に施す逆変換処理部と、逆変換処理部から出力された信号の振幅値に基づいて第1及び第2のビット値を判定し、入力データを復号する入力データ復号部と、を備える、情報処理装置が提供される。

(もっと読む)

ディジタルインターフェースを有する半導体装置

【課題】本発明の課題は、インターフェースのレシーバにて、データパターンに依存するジッタを低減することにある。そして、低減するための遅延量の設定を装置毎に調整できるように自動的に調整可能なLSIを提供することにある。

【解決手段】データパターン依存ジッタは、前の状態がどの様であったかで予測可能であるので、レシーバにて受け取ったデータの状態を保持しこの保持された状態と、入力されたデータとから入力データの取り込みタイミングを調整する。

また、実装形態に依存する遅延量を決定するためのレシーバ内の調整機構として、ドライバから1サイクル間隔のパルスデータ、2サイクル間隔のパルスデータをテストパターンとして送受信する。パルス幅の異なるパルスの立上りと立下がり時間差から系に最適な遅延量を求める自動調整機構を持つ。

(もっと読む)

1 - 20 / 67

[ Back to top ]