Fターム[5K047AA05]の内容

デジタル伝送方式における同期 (12,489) | 目的、効果 (2,701) | 同期品質の向上 (1,344) | タイミング品質の向上 (665)

Fターム[5K047AA05]の下位に属するFターム

位相ジッタ吸収 (104)

ケーブル長依存の伝送遅延変化の補償 (27)

スキュー補正 (110)

無信号時にもクロック供給 (10)

Fターム[5K047AA05]に分類される特許

1 - 20 / 414

クロックデータ再生回路

ゲーティッドVCO回路

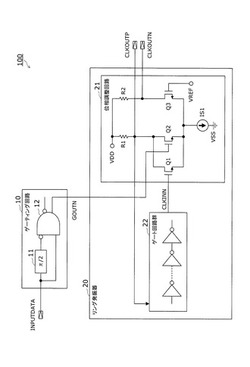

【課題】ジッタやクロックデューティ比のずれが抑えられた良好なクロック成分を抽出する。

【解決手段】リング発振器20の位相調整回路21において、ゲート回路群22から出力された自走クロック信号CLKINNを入力とするMOSトランジスタQ1、およびゲーティング回路10からのゲーティング信号GOUTNを入力とするMOSトランジスタQ2の並列接続回路と、基準となるレファレンス電圧VREFを入力とするMOSトランジスタQ3とが差動対をなすCML回路を構成し、当該CML回路で得られた自走クロック信号CLKINNとゲーティング信号GOUTNとの論理和またはその反転論理をクロック出力信号CLKOUTとして出力する。

(もっと読む)

ゲートウェイ装置

【課題】現用系と予備系の各々のTDMデータの内容及びその出力タイミングを簡単に一致させることができるゲートウェイ装置を提供する。

【解決手段】

中継部の各々は、系切り替え手段による指定に関らず、IP網から到来したパケットを一時的に記憶する記憶部を含み、当該系切り替え手段によって現用系中継部として指定されたときは、先頭パケットに含まれるシーケンス番号を先頭シーケンス番号として予備系中継部に供給するとともに、当該先頭パケットを受信した時刻に所定遅延時間を加算して得られた読出し開始時刻を当該予備系中継部に供給し、当該系切り替え手段によって予備系中継部として指定されたときは、当該先頭シーケンス番号以降のシーケンス番号のパケットのみを当該記憶部に記憶し、且つ当該読出し開始時刻が到来してから当該記憶部に記憶されているパケットの読出しを開始する。

(もっと読む)

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

受信装置、周波数偏差算出方法及びコンピュータプログラム

【課題】異なるタイミングで受信されるリファレンス信号間の相関から推定できる周波数偏差の範囲を拡大する。

【解決手段】受信装置12は、異なる複数の受信間隔で受信されるリファレンス信号に基づいて、複数の受信間隔毎に各受信間隔において生じる受信信号の位相差を推定する処理と、推定された位相差に基づいて、複数の受信間隔毎に複数の位相差候補を決定する候補決定処理と、複数の受信間隔毎に選択される位相差候補同士を組み合わせて形成される位相差候補の複数の組合せの中から、複数の受信間隔における受信信号の位相差を示す組合せを選択する選択処理と、選択された組合せに含まれる位相差候補に基づいて受信信号の周波数偏差を推定する推定処理を実行する制御部17を備える。

(もっと読む)

PONシステムのCDR回路およびCDR回路におけるパルス幅歪自己検出方法とパルス幅歪自己補償方法

【課題】簡易な入力データパルス幅歪の自己検出、自己補償機能を備えたPONシステムのCDR回路を提供する。

【解決手段】CDR機能手段での入力データのエッジ位相の検出結果に対するエッジ位相ヒストグラムを作成する手段8、CDR機能手段でのN位相クロック生成結果をシステムクロック速度レベルまで分周したクロックをシステムクロックから生成したm位相クロックにてサンプリングし得られた結果から分周クロックのエッジ位相を検出してクロックヒストグラムを作成する手段11−13、クロックヒストグラムからN位相クロックのジッタ量を検出し、またエッジ位相ヒストグラムからクロックヒストグラムを減算し入力データに重畳するジッタ成分のみ抽出し重畳するジッタ成分から入力データの理想的な1ビットパルス幅とことなるピークをパルス幅歪量として判断し検出する検出手段9を含む。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

同期システム、タイムマスタ装置、タイムスレーブ装置及び同期方法

【課題】非対称2重リング型のネットワーク等あらゆる接続形態の論理リングネットワークであっても、同期を確立することを目的とする。

【解決手段】タイムマスタ装置(M)は、通信時間を計測するための計測情報を送信する。また、タイムマスタ装置(M)は、計測情報を送信してからネットワークを巡って再び受信するまでの時間を計測する。各タイムスレーブ装置(Sx)は、計測情報を受信してから再び受信するまでの時間を計測する。各分岐装置(Cx)は、計測情報を受信してから再び受信するまでの時間を分岐先毎に計測する。各タイムスレーブ装置(Sx)は、各装置が計測した時間に基づき、遅延時刻を算出する。また、各タイムスレーブ装置(Sx)は、タイムマスタ装置(M)から同期時刻算出のタイミング情報を受信した時刻から遅延時間後の時刻を同期時刻として算出する。

(もっと読む)

データ通信装置及びその処理方法

【課題】 外部から受ける外来ノイズ(静電気)に対して発生する、画像の乱れを低減した装置及び方法を提供する。

【解決手段】 例えば、外来ノイズにより、通信フォーマットで規定されたクロック信号に同期して、受信すべきデータの水平同期位置が誤っている場合に、水平同期位置を示す水平同期信号のサイクル間隔に従って当該水平同期位置を補正する。

(もっと読む)

PONシステムの宅側装置、信号処理回路及び同期維持方法

【課題】 光トランシーバのスリープ時間の経過後に即座に通信を開始できる信号処理回路を提供する。

【解決手段】 本発明の信号処理回路は、光トランシーバ21から入力された受信信号からクロックと受信データを再生し、再生された受信データを上位層側に出力する受信側処理部33,34と、上位層側から入力された送信データを再生されたクロックと同期する送信信号として光トランシーバ21に出力する送信側処理部31,32とを備える。また、本発明の信号処理回路は、光トランシーバ21の機能を低下させるスリープ動作を行う場合に、既に再生されたクロックをスリープ時間中において保持し、かつ、スリープ時間の終了とともにクロックの保持を解除する同期維持モードを実行する制御部27を備える。

(もっと読む)

クロック再生回路

【課題】ジッタが小さく、面積が小さなクロック再生回路を提供する。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

(もっと読む)

アンテナ切り替え受信システム及びそれを備えた無線通信器

【課題】アンテナ切り替え受信システムにおいて、マルチパスが多い環境下においてもマルチパスフェージングによるレベル変動の影響を低減する。

【解決手段】複数のアンテナを所定の周期で切り替えながら(#1)、送信システムから送信される無線信号を受信する(#2)。受信した信号をダウンコンバート、復調し(#3、#4)、ビット同期が確立される(#5)。その後、ユニークワードが検出される(#6においてYES)とアンテナを固定して(#7)、その後のペイロードが受信される(#8)。

(もっと読む)

受信回路及びエラー検出方法

【課題】設計時のタイミング調整を容易とする受信回路及びエラー検出方法を提供すること

【解決手段】本発明にかかる受信回路は、位相の異なる複数のクロックを用いて、矩形波としてデータが遷移する受信シリアルデータビット列をサンプリングして、前記サンプリングされた受信シリアルデータビットを用いて受信データビット列を生成するDL回路部1と、前記サンプリングされた前記受信シリアルデータビットのうち、所定期間内に位相の異なるクロックを用いてサンプリングされた前記受信シリアルデータビットの値が一致するか否かを比較した結果に基づいて前記受信データビット列のエラー区間を検出するPD回路部2と、を備えるものである。

(もっと読む)

データ転送システムおよびデータ転送方法

【課題】システム性能を低下させることなくマスタから周辺回路へデータを転送することが可能なデータ転送システムを提供することである。

【解決手段】本発明にかかるデータ転送システムは、マスタM1〜M3と、マスタから第1のバス2を介して出力された複数のデータD1〜D3を入力し第2のバス4を介して当該データを出力するバスブリッジ3と、バスブリッジ3から出力されたデータD1〜D3を保持するライトバッファWB1〜WB3および当該ライトバッファWB1〜WB3から出力されたデータD1〜D3を保持するレジスタR1〜R3を備える周辺回路5と、を備える。バスブリッジ3およびライトバッファは第1のクロックで動作し、レジスタは第1のクロックとは非同期の第2のクロックで動作し、ライトバッファとレジスタとを同期化することでライトバッファからレジスタへデータを転送する。

(もっと読む)

通信装置、制御信号生成方法、シャッターメガネ、及び通信システム

【課題】 受信データから得られる基準タイミングに基づいた表示装置等の被制御装置の制御を遅延なくかつ低消費電力で可能にする通信装置、その被制御装置を制御するための制御信号生成方法、受信データから得られる基準タイミングに基づいたシャッターの開閉を遅延なくかつ低消費電力で可能にするシャッターメガネ、及び基準タイミングを表すデータの送受信を遅延なくかつ低消費電力で可能にする通信システムを提供する。

【解決手段】 間欠的に到来するデータ内に所定の基準タイミング信号パターンが存在するか否かを識別するタイミング信号識別手段と、タイミング信号識別手段によって所定の基準タイミング信号パターンの存在が識別された場合に被制御装置に対する制御信号を生成する制御信号生成手段と、通信装置の制御を司る制御手段と、を備える。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

回路装置、通信機器及び通信システム

【課題】低消費電力で無線通信を行うことが可能な回路装置、通信機器及び通信システムを提供すること。

【解決手段】この回路装置は、所与のイベントを検出する第2のセンサーを備えた外部機器と通信を行う回路装置であって、前記所与のイベントを検出する第1のセンサーからの入力を処理するセンサー入力部と、無線通信部の動作を制御する通信制御部とを含み、前記第1のセンサーの出力に基づき通信タイミングを決定し、前記通信タイミングに基づき前記無線通信部を介して前記外部機器との通信を行う。

(もっと読む)

受信装置、プログラム、半導体装置、通信システム

【課題】拡散変調された送信データに妨害波が重畳した状況下であっても、相関ピーク値による同期検出が可能になる受信装置、プログラム、半導体装置、通信システムを提供する。

【解決手段】通信装置Aは、受信した通信データに基づいて生成される基本符号列において、第1の部分符号列の特定領域に窓関数1−Wkを乗じる窓関数処理部62と、基本符号列において、第1の部分符号列から同期シンボルのシンボル長の整数倍だけ離れた第2の部分符号列の特定領域に窓関数Wkを乗じる窓関数処理部63と、窓関数処理部62,63の各乗算結果を合成した合成符号列を生成する合成部64と、特定領域を合成符号列に置き換えた第1の部分符号列と拡散符号との相関値を演算する相関器1と、相関器1が演算した相関値から相関ピーク値を抽出することによって、同期タイミングの検出処理を行う同期検出部K10とを備える。

(もっと読む)

映像受信装置

【課題】ビットレートが低い場合であってもデコードの開始が遅れることを回避することが可能な映像受信装置を得る。

【解決手段】映像受信装置4は、それぞれにタイムスタンプ50が付加された複数のトランスポートパケットTPを含むトランスポートストリームS1を一時的に記憶するバッファメモリ11と、基準クロックを発生するVCO18と、基準クロックに基づいてカウント動作を行うTTSカウンタ16と、各トランスポートパケットTPに付加されているタイムスタンプ50の値と、TTSカウンタ16のカウント値とに基づいて、バッファメモリ11からの各トランスポートパケットTPの出力を制御するTTSゲート12と、バッファメモリ11に入力されたトランスポートパケットTPの滞留時間に基づいて、基準クロックの周波数を調整する調整部17と、を備える。

(もっと読む)

1 - 20 / 414

[ Back to top ]