Fターム[5K047AA06]の内容

デジタル伝送方式における同期 (12,489) | 目的、効果 (2,701) | 同期品質の向上 (1,344) | タイミング品質の向上 (665) | 位相ジッタ吸収 (104)

Fターム[5K047AA06]に分類される特許

1 - 20 / 104

パケット伝送システムおよび方法

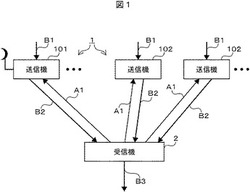

【課題】ジッタが存在する可能性のある伝送路を経由したMPEG2−TSパケットの送受信において、外部GPSを用いずに送信機とのクロック同期をとり、1台の受信機で複数台の送信機から個別に送信されるパケットのPCRジッタを抑制する。

【解決手段】受信機から同期に必要なパイロットパターンを複数台の送信機全てに向けて送信する。送信機は、受信したパイロットパターンを基にしてTTSを付与したパケット(MPEG2−TTSパケット)を送出する。受信機側において受信したMPEG2−TTSパケットを、パイロットパターンを基にしたタイミングでMPEG2−TSとして送出することにより、クロック同期をとる。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】ゲーティング回路と、再生クロックを出力する第1の発振回路と、第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に周波数制御信号Aと回路間ばらつき調整信号C1の加算信号を入力し、ゲーティング回路の制御端子に周波数制御信号Aと回路間ばらつき調整信号C2の加算信号を入力する構成である。

(もっと読む)

信号伝送装置

【課題】N(Nは3以上の整数)チャネルの信号を伝送すること。

【解決手段】各チャネルCH1〜CH5のうち、クロック源が共通のチャネルの中からクロック源に同期している正常な一のクロックを選択するM(Mは1以上N未満の整数)個のクロック選択部150と、クロック選択部150が選択したクロックのジッタを抑圧するM個のジッタ抑圧部160とを備える。

(もっと読む)

データ送信回路、データ受信回路、データ送受信システム、データ送信方法、及びデータ受信方法

【課題】データ送信回路とデータ受信回路とが互いに同期していないときに、データ受信回路においてデータ過多又はデータ欠損を生じさせることなく、ディジタルオーディオデータに含まれる音声又は音楽の再生品質を向上する。

【解決手段】周期測定部1は、受信LRクロックLRrに同期しかつ受信LRクロックLRrの周波数より高い所定の周波数を有する高速サンプリングクロックfsrを用いて、送信LRクロックLRsの周期を所定の時間間隔で測定する。データ補間部2は、測定された送信LRクロックLRsの周期と受信LRクロックLRrの周期との周期差を算出し、受信LRクロックLRrの各出力タイミングにおいて、算出された周期差に基づいて当該各出力タイミングにおける送信LRクロックLRsの位相を算出し、当該各出力タイミングの前後のオーディオデータDaを、算出された位相に基づいて線形補間して補間オーディオデータDinsrを生成する。

(もっと読む)

データ送信回路、データ受信回路、データ送受信システム、データ送信方法、及びデータ受信方法

【課題】データ送信回路とデータ受信回路とが互いに同期していないときに、データ受信回路においてデータ過多又はデータ欠損を生じさせることなく、ディジタルオーディオデータに含まれる音声又は音楽の再生品質を向上する。

【解決手段】周期測定部1は、受信LRクロックLRrに同期しかつ受信LRクロックLRrの周波数より高い所定の周波数を有する高速サンプリングクロックfsrを用いて、送信LRクロックLRsの周期を測定する。データ補間部2は、測定された送信LRクロックLRsの周期と受信LRクロックLRrの周期との周期差を算出し、受信LRクロックLRrの各出力タイミングにおいて、算出された周期差に基づいて当該各出力タイミングにおける送信LRクロックLRsの位相を算出し、当該各出力タイミングの前後のオーディオデータDaを、算出された位相に基づいて線形補間して補間オーディオデータDinsrを生成する。

(もっと読む)

信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

(もっと読む)

CDR回路

【課題】ジッタの抑圧と応答時間の短縮とを両立させる。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO11と、G−VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO12と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ回路3と、入力データ4のデータ信号期間の少なくとも一部において、ゲーティング回路10の出力パルスが再生クロック7に与える影響を、入力データ4の同期信号期間と比較して小さくするよう制御する可変減衰器16とを備える。

(もっと読む)

サンプリングクロック同期装置、ディジタルコヒーレント受信装置およびサンプリングクロック同期方法

【課題】受信品質の向上を図る。

【解決手段】サンプリングクロック同期装置は、A/Dコンバータ、フィルタ部およびサンプリング同期化部を備える。A/Dコンバータは、サンプリングクロックにもとづいて、アナログ/ディジタル変換を行う。フィルタ部は、A/Dコンバータから出力された、スペクトル狭窄化を受けている信号に対して、スペクトル狭窄化の特性と逆特性のフィルタ特性で、スペクトル狭窄化による帯域制限を補償する。サンプリング同期化部は、スペクトル狭窄化の補償後の信号から、サンプリングクロックの位相ずれを検出して、サンプリングクロックの位相を調整し、サンプリングタイミングの同期をとる。

(もっと読む)

GPSジッタ低減装置

【課題】後段側の装置を軽量に設計することのできるGPSジッタ低減装置を得る。

【解決手段】位相比較調整処理部105は、GPS11が出力する1PPSと、出力パルス生成部104から出力される平滑化された1PPSとの位相差をカウントし、位相差目標値と比較して、固定値にて調整を実施する。出力パルス生成部104は、移動平均処理部103の出力と、位相比較調整処理部105の調整値に基づいて平滑化した1PPSを生成する。

(もっと読む)

半導体集積回路装置およびジッタ補正方法

【課題】SERDESがジッタを含むシリアルデータ信号をオーバーサンプリング動作によって受信した場合に、SERDESから出力されたパラレルデータ信号およびリカバリクロック信号に基づいて、もとのシリアルデータ信号を正しく受信できるようにすること。

【解決手段】半導体集積回路装置は、シリアルデータ信号をm倍(mは2のべき乗)オーバーサンプリングするSERDES回路から出力されたNビットの第1のパラレルデータ信号に基づいてKN/mビット(N/mは偶数)の第2のパラレルデータ信号を生成するとともに、SERDES回路から出力された第1のリカバリクロック信号をK分周(Kは2のべき乗)して第2のリカバリクロック信号を生成し、第2のパラレルデータ信号と第2のリカバリクロック信号とを同期して出力するクロックデータリカバリ回路を備えている。

(もっと読む)

受信回路

【課題】 多相クロック信号を用いてデータを受信する受信回路において、多相クロック信号の位相歪みを抑制すること。

【解決手段】 本受信回路30は、位相コードに基づき、多相クロック入力信号から任意の位相の多相クロック出力信号を生成する位相インターポレータ40と、位相コードに変動を与える位相変動回路52と、位相コードの変動に対する多相クロック出力信号の変動を検出する位相検出回路46と、位相検出回路46の検出結果に基づき、位相インターポレータ40の位相歪みを推定する歪み推定回路52と、歪み推定回路52の推定結果に基づき、位相歪みを補正する補正回路52と、を備える。

(もっと読む)

受信回路

【課題】エラーの発生率を改善し目標とする発生率にする際の遅延量を低減した受信装置を提供する。

【解決手段】発生確率が時間に応じて正規分布するランダムジッタを含む信号を入力し、この入力信号をデジタルデータに変換して出力する受信装置において、位相を設定可能なクロック信号を生成するクロック回路と、前記入力信号を前記クロック信号に基づくタイミングでデジタルデータに変換して出力するとともに、前記変換の際にエラーが生じた場合にはエラー信号を出力する第1受信回路と、前記入力信号を遅延させた信号を、前記クロック信号に基づくタイミングでデジタルデータに変換して出力するとともに、前記変換の際にエラーが生じた場合エラー信号を出力する第2受信回路と、第1、第2受信回路のエラー信号に基づいて、第1受信回路または第2の受信回路のいずれか一方からのデジタルデータを選択して出力するデータ出力制御部を備えた。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

受信回路及びサンプリングクロック制御方法

【課題】1ユニットインターバルに対するサンプリング数を一定に保つことができる受信回路を提供することを課題とする。

【解決手段】1サイクル内で複数の異なる位相のクロック信号を生成するクロック発生回路(301)と、複数の異なる位相のクロック信号により入力データをオーバーサンプリングするオーバーサンプリング回路(303)と、オーバーサンプリング回路により出力されたデジタルデータの時系列の変化点を検出し、1ユニットインターバルの両端の2個のデータバウンダリを判定するデータバウンダリ判定回路(305)と、判定された2個のデータバウンダリの間の1ユニットインターバルのサンプリング数が閾値より多いときには、隣接する1ユニットインターバルのサンプリング数が一定となるようにクロック発生回路で生成するクロック信号の位相を制御するクロック位相制御回路(306)とを有する受信回路が提供される。

(もっと読む)

デジタル信号処理回路、デジタル信号処理方法、及び、プログラム

【課題】セットアップタイム及びホールドタイムのマージンを十分に確保することが可能なデジタル信号処理回路を提供すること。

【解決手段】回路は第1の遅延量を複数の判定用遅延量のそれぞれに設定する。回路は入力データ信号を、第1の遅延量だけ遅延させた第1の遅延データ信号と第2の遅延量だけ遅延させた第2の遅延データ信号とを出力する。回路は、第1の遅延データ信号をラッチすることにより第1のラッチデータを取得し、第2の遅延データ信号をラッチすることにより第2のラッチデータを取得する。回路は、複数の判定用遅延量のそれぞれに対して、第1のラッチデータと第2のラッチデータとが一致しているか否かを判定し、当該判定結果に基づいて第1のラッチデータと第2のラッチデータとを一致させるように、第1の遅延量を第1の制御遅延量に設定し且つ上記第2の遅延量を第2の制御遅延量に設定する。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの確実な同期と再生クロックの適切なジッタ低減とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aは、外部から入力される駆動力制御信号に応じて駆動力が調整される駆動力調整機能付きバッファ増幅器である。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

1 - 20 / 104

[ Back to top ]