Fターム[5K047GG06]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | クロックの伝送 (1,938) | クロックの受信 (1,715)

Fターム[5K047GG06]の下位に属するFターム

クロックの選択、切換え (63)

伝送クロックよりクロックの再生 (446)

受信信号よりタイミングの抽出 (1,089)

Fターム[5K047GG06]に分類される特許

1 - 20 / 117

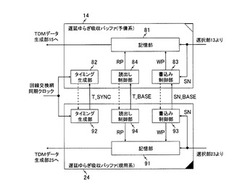

ゲートウェイ装置

【課題】現用系と予備系の各々のTDMデータの内容及びその出力タイミングを簡単に一致させることができるゲートウェイ装置を提供する。

【解決手段】

中継部の各々は、系切り替え手段による指定に関らず、IP網から到来したパケットを一時的に記憶する記憶部を含み、当該系切り替え手段によって現用系中継部として指定されたときは、先頭パケットに含まれるシーケンス番号を先頭シーケンス番号として予備系中継部に供給するとともに、当該先頭パケットを受信した時刻に所定遅延時間を加算して得られた読出し開始時刻を当該予備系中継部に供給し、当該系切り替え手段によって予備系中継部として指定されたときは、当該先頭シーケンス番号以降のシーケンス番号のパケットのみを当該記憶部に記憶し、且つ当該読出し開始時刻が到来してから当該記憶部に記憶されているパケットの読出しを開始する。

(もっと読む)

基地局および通信制御方法

【課題】専用線ではない通信ケーブルで基地局と公衆網などを接続した場合であっても、周辺の基地局との同期ずれを抑制した基地局を提供する。

【解決手段】通信端末MSとの間で無線通信を行う無線通信部1と、公衆網NWとの間で有線通信を行う有線通信部6と、公衆網NWを介して上位装置100から送信される送信データに含まれる同期信号に基づいて同期処理を行う制御部9と、上位装置100からの同期信号よりも高精度の高精度同期信号に基づいた同期処理を行う同期部2とを備え、制御部9は、同期部2における同期処理が不可能な状態となった場合に、上位装置に対して送信データが公衆網を優先的に通過できるように優先度を高くして送信するように指示を出し、上位装置100からの同期信号に基づく第1のタイミングと、自機のクロックに基づく第2のタイミングとの差分が所定値を超えるか否かで、同期の調整の要否を判断する。

(もっと読む)

遷移検出回路

【課題】

簡潔な構成でコード信号の遷移を検出する遷移検出回路を提供する。

【解決手段】

1ビットずつ遷移するグレイコードの遷移を検出する検出回路において、グレイコードのビットに含まれる1の個数が偶数であるか奇数であるかによって変化する信号を出力する組み合わせ論理回路と、組み合わせ論理回路の出力が変化したときに有効となる遷移検出信号を生成する比較回路とを備える。

(もっと読む)

情報通信端末、生体情報測定機器及び情報通信システム

【課題】無線通信を行う情報通信端末において、汎用無線方式での通信回路の同期信号を利用して、上位層のアプリケーションとしての情報処理の同期を実現すること。

【解決手段】無線通信を行う無線通信部110と、所与の情報処理を行う処理部120と、を含み、前記無線通信部110は、前記外部機器との無線通信の同期を確立するための同期信号を送信して、前記外部機器との無線通信の同期を確立する無線通信同期確立部112と、前記無線通信の同期のタイミングで前記プロセッサーに割り込み信号を出力する処理、又は無線通信の同期のタイミングからの相対時刻をカウントするためのカウント制御処理を行う制御部116とを含み、前記処理部120は、前記外部機器に対する送信情報として、所与のイベントを前記無線通信の同期のタイミングに対応して設定された相対時刻に関連づけたイベント情報を生成する送信情報生成部122を含む情報通信端末100である。

(もっと読む)

データ受信装置及びデータ送信装置

【課題】後段の誤動作を抑制するデータ受信装置及びデータ送信装置を提供する。

【解決手段】物理層回路とMAC層との間でデータが非同期転送される。データは1バイト単位で処理される。検出回路は変換モジュールが送信したデータの第1のパケットと第2のパケットとの間隔が規格最小値より短いことを検出する。第2のパケットは第1のパケットに続く。無効化回路は間隔が規格最小値より短いことが検出回路に検出された場合に第2のパケットの先頭から1バイトの自然数倍分のデータを無効化する。無効化は、間隔が規格最小値以上となるように行われる。

(もっと読む)

クロックド・シリアル・インタフェース

【課題】様々な波形のコントロール信号を生成し出力できるクロックド・シリアル・インタフェース(CSI)を提供する。

【解決手段】コントロール信号の波形を決定するパターンデータが書換可能に格納される複数のシフトレジスタと、これらシフトレジスタ内のパターンデータに応じてコントロール信号を生成する生成手段と、を備える。具体的には、CSI60は、3つのシフトレジスタ81,82,83を有し、これらシフトレジスタ内のパターンデータに応じた波形のコントロール信号を生成し出力する。

(もっと読む)

通信インタフェース装置及び該通信インタフェースを備えた半導体装置

【課題】複数のレーンを有する通信インタフェースにおいて消費電流の増大を抑制し各レーン間でパラレルクロック信号を同期させる装置の提供。

【解決手段】シリアルクロック線21にシリアルクロック信号が供給され、レーン1はシリアルクロック線からシリアルクロック信号を入力して第1のレーン内に分配し、該シリアルクロック信号サンプリングクロック信号とするカスケード接続されたフリップフロップ(FF)12、13を有し、FF13の出力の反転信号がFF12に帰還入力される分周回路を備え、FF13の出力信号がパラレルクロック信号としてレーン1内に分配され、レーン2ではシリアルクロック信号を入力してレーン内に分配し、レーン1のFF12の出力を受け、レーン2の前記シリアルクロック信号でサンプルするFF13を備え、FF13の出力がパラレルクロック信号としてレーン2内に分配されると共にレーン2のFF12に帰還入力される。

(もっと読む)

タイミング調整装置、タイミング情報生成装置、および時刻同期システム

【課題】他の通信システムから受信したタイミング基準信号を用いる装置に対し、動作タイミングに関する情報を提供することを目的とする。

【解決手段】GPS受信機12は衛星信号を受信し、1PPS信号およびTODを時刻情報分配器14に出力する。時刻情報分配器14では、内部のタイミング調整装置22にて1PPS信号およびTODに基づいて時刻同期タイミング調整用のデータ信号を生成する。そして、各無線基地局20に対応する信号伝送線16に当該タイミング調整用データ信号を送信する。タイミング情報生成装置18は、時刻情報分配器14から信号伝送線16を介してタイミング調整用データ信号を受信する。そして、タイミング調整用データ信号が示すタイミングに基づいて1PPS信号を再生すると共に、タイミング調整用データ信号からTODを抽出し、1PPS信号およびTODを無線基地局20に出力する。

(もっと読む)

通信装置およびクロック同期方法

【課題】リング網において障害発生時のクロックソースの切替に要する時間を短縮する。

【解決手段】実施の1形態のノード10は、リング網36における第1方向の伝送路を介して伝送された第1クロック情報と、リング網36における第2方向の伝送路を介して伝送された第2クロック情報の少なくとも一方を用いて当該ノードの動作をマスタクロックに同期させる。ノード10は、リング網36における第1方向の伝送路で障害が検出された場合、第2クロック情報を用いてマスタクロックへの同期処理を実行させるための付加情報を第1クロック情報に設定してリング網の第1方向へ送出する。それとともに、その付加情報を第2クロック情報にも設定してリング網の第2方向へ送出する。

(もっと読む)

同期信号検出装置

【課題】回路規模を小さくできるようにした同期信号検出装置を提供する。

【解決手段】同期信号仮検出部7が、2値のハイレベルとロウレベルとを順に繰り返して受信する前に1ビット長の2のN乗倍の長さで2値のロウレベルが続いたことを条件として受信した2値のレベルを仮同期信号として検出しているため、ロウレベルが1ビット長の2のN乗倍の長さ未満のときには全て仮同期信号として見なされることがなくなり、同期信号を検出するための煩雑な計算処理を行う頻度を少なくできる。

(もっと読む)

データ送出装置、データ受信装置、及びデータ送受信システム

【課題】従来のHDMIのオーディオクロック伝送システムでは、サイクルタイムスタンプ値が変動してオーディオクロックの精度が劣化してしまう。

【解決手段】データのサンプルクロックを所定の分周比で分周してクロックを生成するクロック分周手段と、クロック分周手段で生成したクロックをカウントするカウント手段と、カウント生成手段で計測したカウント値を平均化する平均化手段と、平均化手段で取得した平均カウント値のビット数を削減するノイズシェーピング手段と、基本クロック、ノイズシェーピング手段で生成したカウント値及びクロック分周手段で使用した分周比を送出する送出手段を備える。

(もっと読む)

時刻同期装置およびその時刻同期補正方法

【課題】GPS衛星電波が受信出来ない時も正確に同期タイミング信号を出力する時刻同期装置およびその時刻同期補正方法を提供する。

【解決手段】内蔵発振器1は、GPS受信器Rからの1pps信号と出力するクロックと間の位相差信号を発振制御部3へ出力し、この位相差を無くす発振周波数制御信号が発振制御部3内蔵発振器1へ出力される。1pps信号が断となった場合、発振制御部3は、ログ部LGのドリフト記録部5と信号断時間記録部6から、予め測定記録していた単位時間あたりの内蔵発振器1の周波数のドリフト量からドリフトを補正する発振周波数制御信号を生成して内蔵発振器1へ出力し、タイミング信号発生部2は、内蔵発振器1からのクロックにより生成した同期タイミング信号を外部へ出力する。

(もっと読む)

シリアル通信装置

【課題】受信回路と送信回路とで必要となるハードウェア信号を削減することを目的とする。

【解決手段】受信回路と送信回路とを有するシリアル通信装置であって、受信回路から前記送信回路へ送信されている位相合わせ用の基準クロックが停止したことを検知することでハードウェアフロー制御を行うことによって課題を解決する。

(もっと読む)

データ伝送システム及び方法、データ送信装置及び受信装置

【課題】データの符号化の条件の制約を受けずに、高周波伝送を可能にしたデータ伝送システムを提供する。

【解決手段】データ送信装置101は、バッファ回路111と、遅延回路112及び遅延回路113と、セレクタ114と、Dフリップフロップ115とを有する。セレクタ114は、その立ち上がりエッジの位相がデータDINのデータ値に対応して変化し、その立ち下がりエッジの位相が一定となるようなデータ出力信号OUTを出力させる。データ受信装置102は、PLL回路121と、データ復元回路122とを有する。PLL回路121は、受信信号IN1の立ち下がりに同期して基準信号REF1を生成し、データ復元回路122は、生成された基準信号REF1の立ち上がりのタイミングで、受信信号IN1と基準信号REF1との位相差を検出してデータを復元する。

(もっと読む)

電子回路ユニット、シリアル伝送システム、および伝送制御方法

【課題】基準CLKのための専用のCLKユニットや各ユニット内のPLLを必要としない構成で、低コスト、低消費電力を実現しながらも、データエラーを引き起こすことのないようにする。

【解決手段】他の電子回路ユニットからシリアル伝送によりデータ受信を行う電子回路ユニットについて、上記電子回路ユニットおよび上記他の電子回路ユニットは、基準クロックを発生させるクロック発生器をそれぞれ備え、上記電子回路ユニットは、当該電子回路ユニットにおける基準クロックおよび上記他の電子回路ユニットにおける基準クロックのずれを監視する監視手段と、上記監視手段により検出された基準クロックのずれを該電子回路ユニットの上記クロック発生器に補正させる補正指示手段と、を備える。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

半導体装置及びデータ処理システム

【課題】電力消費を抑えて長周期ジッタに起因するビットエラーの発生を抑制することができるシリアル受信回路を提供する。

【解決手段】クロック信号(CK3)に同期してシリアル信号を受信するシリアル受信回路(2)は、前記クロック信号に対して位相をずらした複数相のサンプリング位相(CLK(1)〜CLK(N))に同期して前記シリアル信号をサンプリングし、サンプリングした信号に基づいて前記シリアル信号の位相変動によるサンプリング結果への影響が少ないサンプリング位相を最適位相と判別して当該最適位相によりサンプリングした信号を受信データとする受信動作を行い、前記最適位相の判別動作として、第1モード(初期位相検出)と、前記第1モードで判別された最適位相の最適性を前記サンプリング数を減らしたサンプリング結果に基づいて判別する第2モード(位相追跡)と、を有する。

(もっと読む)

クロック検出方法及びその装置

【課題】既存のクロック検出方法のリソース占用率が高い問題を解決できるクロック検出方法及びその装置を提供する。

【解決手段】該方法は、プログラマブル部品が、ローカルタイムソースにより生成されたソースクロック信号に周波数分割を行って参照クロック信号を取得し(S101)、プログラマブル部品が、ソースクロック信号をカウント動作クロックとし、検出対象クロック信号の、参照クロック信号の連続するN(Nは正整数である)個のハイ電圧レベルの各ハイ電圧レベル期間における立ち上がりエッジカウント値とハイ電圧レベルカウント値を確定し(S102)、プログラマブル部品が、検出対象クロック信号の、各ハイ電圧レベル期間におけるハイ電圧レベルカウント値と第1の所定値との大きさ関係、及び立ち上がりエッジカウント値と第2の所定値との大きさ関係に基づいて、検出対象クロック信号が有効であるかを確定する(S103)。本発明によると、少ないリソースを占め、クロック検出の信頼性が向上でき、また、検出対象クロック信号の周波数範囲が広くなり、検出対象クロック信号の高周波数グリッチによる影響を避けることができる。

(もっと読む)

クロックを並列データに整列させるための回路

【課題】クロック信号を並列データに整列させるための方法を提供する。

【解決手段】クロックシフティング回路10は、入来クロック信号8を入来データ信号16に対してシフトし、データクロッキング回路20は、シフト済みクロック信号を使用して、入来データ信号16を再クロックする。クロックシフティング回路10は、位相ロックループ回路2に直列に接続されている複数のDフリップフロップ回路4,6を連結して備える。データクロッキング回路20は、それぞれの入来データビット16を受信し、ミキサ22に対するローカルオシレータとして働く真−補数ブロック50,58を備える。複数のシフト済みクロック信号62,54,64,56は、入来クロック信号16に対して90度、180度、及び270度シフトされたものなど、が生み出される。

(もっと読む)

1 - 20 / 117

[ Back to top ]