Fターム[5K047GG22]の内容

デジタル伝送方式における同期 (12,489) | 網同期;クロック、ビット同期 (2,470) | クロックの伝送 (1,938) | クロックの受信 (1,715) | 受信信号よりタイミングの抽出 (1,089) | 抽出手段、原理 (419)

Fターム[5K047GG22]の下位に属するFターム

受信信号特異点を利用 (164)

受信信号スペクトルを利用 (10)

高周波クロックを用いるもの (161)

Fターム[5K047GG22]に分類される特許

1 - 20 / 84

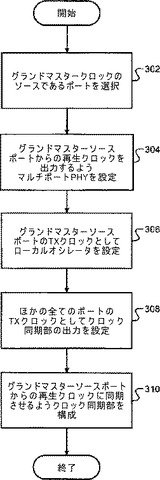

同期ネットワークデバイス

【課題】物理層デバイスおよび同期デバイスの複数のポート間でクロックを同期させる方法を提供する。

【解決手段】制御方法は、グランドマスタークロックのソースとなるポートを選択するステップを含む(302)。選択されたポートは、リンク先からの送信に基づいてグランドマスタークロックを再生する。マルチポートPHY ICは、グランドマスターソースポートのRX_CLKを出力する(304)。グランドマスターソースポートのTX_CLKは、ローカルオシレータから取得される(306)。そして、ほかの全てのポートのTX_CLKは、クロック同期部の出力から取得される(308)。クロック同期部は、グランドマスターソースポートを有するマルチポートPHY ICからの再生クロックに基づいて同期させる(310)。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

パケット伝送システムおよび方法

【課題】ジッタが存在する可能性のある伝送路を経由したMPEG2−TSパケットの送受信において、外部GPSを用いずに送信機とのクロック同期をとり、1台の受信機で複数台の送信機から個別に送信されるパケットのPCRジッタを抑制する。

【解決手段】受信機から同期に必要なパイロットパターンを複数台の送信機全てに向けて送信する。送信機は、受信したパイロットパターンを基にしてTTSを付与したパケット(MPEG2−TTSパケット)を送出する。受信機側において受信したMPEG2−TTSパケットを、パイロットパターンを基にしたタイミングでMPEG2−TSとして送出することにより、クロック同期をとる。

(もっと読む)

トランシーバ

【課題】バス通信路にクロック成分とデータとを重畳して送信する通信システムにおいて、クロック成分を受信する側のノードからのデータ送信を可能とするためのトランシーバを提供する。

【解決手段】マスタからクロック成分を受信するスレーブのトランシーバでは、バス通信路を介したデータの送信が許可されている状態において(S101:YES)、スレーブの信号処理部からロウレベルの送信データが入力されると(S102:YES)、重畳用のロウレベルの信号をバス通信路5へ出力するための処理が行われる(S103〜S105)。具体的には、バス通信路上の信号の立ち下がりエッジが検出されると(S103:YES)、重畳用のロウレベルの信号を出力する期間が算出され(S104)、算出された期間継続してロウレベルの信号が出力される(S105)。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

バイフェーズ符号化データの復号化方法

【課題】バイフェーズ符号化データの復号化方法を提供する。

【解決手段】本発明のバイフェーズ符号化データの復号化方法は、バイフェーズ符号化データ中の立下りエッジ変換を検出することによって、隣り合う2つの立下りエッジ変換の間の時間差値及び前1ビットの論理値に基づき、相応する復号化を行い、時間差値が1個ビット周期であり且つ前1ビットが論理1である時、現在のビットが論理1であると判定し、時間差値が1個のビット周期であり且つ前1ビットが論理0である時、現在のビットが論理0であると判定し、時間差値が1.5個のビット周期であり且つ前1ビットが論理1である時、現在及び後1ビットが何れも論理0であり、時間差値が1.5個のビット周期であり且つ前1ビットが論理0である時、現在のビットが論理1であると判定し、時間差値が2個のビット周期であり且つ前1ビットが論理1である時、現在及び後1ビットがそれぞれ論理0及び1であると判定する。

(もっと読む)

バーストCDR回路およびバースト信号から入力データ信号を再生する方法

【課題】処理が高速で低消費電力なバーストCDR回路を得る。

【解決手段】N位相クロックを生成するN位相クロック生成回路2と、N位相クロックでバースト信号に対するサンプリングを実行するN位相クロックサンプリング回路3と、隣接位相に係るサンプリングデータのEXOR演算値から簡易中心位相を抽出する簡易位相選択回路4と、簡易中心位相に係るデータを並列展開する第1DEMUX回路5と、並列展開されたデータをn回積算し中心位相番号の偶奇を示す偶奇番号データを出力する中心位相積算抽出回路6と、隣接位相に係るサンプリングデータから偶奇番号データに対応したデータを出力するセレクタ回路7と、セレクタ回路からのデータを並列展開する第2DEMUX回路8と、並列展開されたデータをm回積算しデータエッジ位相から最も離れた位相でのサンプリングデータを出力する最適位相データ高精度抽出回路9とを備える。

(もっと読む)

通信装置及び通信方法

【課題】PLL回路をベースとしたCDR回路を使用したトランシーバ間において、再同期を高速に行うことを目的とする。

【解決手段】PLL回路により構成されるクロック抽出部16に、受信信号を受信していない非受信状態の場合には、受信信号を受信している受信状態から非受信状態へ移行する時点におけるクロック信号の位相を示す位相情報を保持しておく受信側位相保持部22を追加する。データ送信時には、受信側位相保持部22が保持した位相情報を用いて生成されたクロック信号を用いて送信データを送信する。

(もっと読む)

CDR回路

【課題】前段の光受信装置のスケルチ機能の有無に関係なく汎用的に使用可能なCDR回路を提供する。

【解決手段】CDR回路は、入力データ1に同期した再生クロック2を出力するG−VCO14と、入力データ1の識別再生を再生クロック2に基づいて行うフリップフロップ回路12と、G−VCO14と同一周波数のクロックを出力するサブVCO15と、再生クロック2とサブVCO15の出力クロック4のいずれかを選択する選択回路17と、選択回路17の出力クロック8と参照クロック6とを周波数比較しその周波数差に応じた周波数制御信号5を出力する周波数比較器16とを備える。選択回路17は、少なくとも入力データ1が無信号である期間においてサブVCO15の出力クロック4を選択し、残りの期間において再生クロック2を選択する。

(もっと読む)

受信装置及び方法、並びにプログラム

【課題】クロックの同期を確実にとることができるようにする。

【解決手段】短時間平均値監視部114は、バッファ112に順次蓄積される受信データの数秒ごとの蓄積容量の平均を示す短時間平均値を取得し、長時間平均値監視部115は、バッファ112に順次蓄積される受信データの数分ごとの蓄積容量の平均を示す長時間平均値を取得する。クロック制御部116は、取得された長時間平均値の評価結果に応じて、デコーダ113が受信データの処理を行うためのクロックの周波数を制御するとともに、取得された短時間平均値に基づいてパケットロスなどの異常が検出された場合、クロックの周波数の調整を停止し、その異常が検出されてから所定の時間が経過した後、クロックの周波数の調整を再開する。本発明は、例えば、ネットワークを利用した動画配信において動画を受信する受信装置に適用することができる。

(もっと読む)

情報処理装置及び携帯端末

【課題】ベースバンド処理部からネットワーク網の同期信号が出力されない場合においても、音声信号の伸長処理を実行可能にする。

【解決手段】情報処理装置(1)は第1シリアルインタフェース(19)を含む。第1シリアルインタフェースは、ベースバンド処理部から取り込まれるデータが、予め設定されたデータ量に達する毎に、その状態を音声処理部(20)に通知するための通知信号を形成する通知信号生成回路(195)を含む。音声処理部は、上記通知信号に基づいてネットワーク網同期信号を形成する同期信号生成回路(205)を含む。上記ネットワーク網同期信号に基づいて上記PCM通信用のクロック信号を形成することにより、ベースバンド処理部からネットワーク網の同期信号が出力されない場合においても、音声信号の伸長処理を実行可能にする。

(もっと読む)

シリアル通信装置及びその制御方法

【課題】内部回路との間で所定の同期クロックを用いて通信を行う送受信回路と、入力される基準クロックに基づいて上記同期クロックを発生するPLL回路とを備えたインターフェース回路を備えたシリアル通信装置において、インターフェース回路及び内部回路の誤動作を防止する

【解決手段】遅延回路5は、基準クロックREFCLKの周波数が100MHzで安定した後に発生されるリセット信号PERST#を、所定の遅延時間Δtだけ遅延させて内部リセット信号PERST2を発生し、リンクコントローラ31に出力する。PHY回路2は、リセット信号PERST#に応答してリセットされ、リンクコントローラ31は、内部リセット信号PERST2に応答してリセットされる。また、遅延時間Δtは、PLL回路23の回路仕様に基づいて予め計算されたロックアップ時間より長く設定される。

(もっと読む)

クロック再生装置、クロック再生方法および制御プログラム

【課題】アダプティブクロック再生法を用いて同期を取っている時にパケット固定遅延を検出した場合でも、安定して送信端末と受信端末との同期を取る。

【解決手段】クロック再生装置10は、クロック出力手段50から受信したクロックに同期させてバッファ60からパケットを出力させると共に、バッファ60の蓄積量を計測して出力するバッファ制御手段20と、遅延の有無を監視し、遅延を検出した場合、遅延量を算出して出力する遅延検出手段30と、バッファ制御手段20から受信した蓄積量に基づいてクロック制御値を生成して出力すると共に、遅延検出手段30から遅延量を受信した場合、該遅延量に対応する期間、所定のクロック制御値を出力するクロック制御手段40と、クロック制御手段40から受信したクロック制御値に基づいてクロックを生成して出力するクロック出力手段50と、を備える。

(もっと読む)

バースト光信号処理装置およびバースト光信号処理方法

【課題】

バースト電気信号のガードタイム中に、バースト電気信号とダミー信号の同期を取る必要なく、ベースラインドリフトを回避する。

【解決手段】

バースト光信号処理装置は、受信したバースト光信号を、バースト電気信号に変換する変換手段と、第1の電気パルス信号とバースト電気信号とから符号化信号を排他的論理和演算により生成して出力する符号化手段と、符号化信号の論理識別再生とクロック信号の再生とを行う再生手段と、再生したクロック信号に位相同期し、前記バースト電気信号よりも符号遷移密度が少ない第1の電気パルス信号と第2の電気パルス信号とを生成して、少なくともバースト電気信号の無信号区間中に第1の電気パルス信号と第2の電気パルス信号とを出力する第1の信号生成手段と、符号化信号を第2の電気パルス信号を用いて復号する復号化手段と、を備える。

(もっと読む)

光受信装置及びクロック生成方法

【課題】分散値の調整を簡易かつ迅速に行うとともに、分散値の調整時にアンロック状態が発生することを回避すること。

【解決手段】分散補償部は、設定された分散値を用いて光信号の波長分散を補償する。位相差信号生成部は、分散補償部によって補償された光信号に含まれるクロックである外部クロックと、自装置内で用いるクロックである内部クロックとの位相差を算出することにより位相差信号を生成する。分散値調整部は、分散補償部に設定された分散値を調整する。抑制部は、分散値調整部によって分散値が調整された場合に、位相差信号生成部によって生成された位相差信号に現れる変動を抑制する。クロック生成部は、抑制部によって抑制された位相差信号に基づいて、外部クロックの位相と同期した内部クロックを生成する。

(もっと読む)

クロック信号を生成できる、または各トランシーバに関連付けられたデジタル・システムのデータのバイパスを可能にする、電力管理されたトランシーバのネットワークを使用する通信システム

【課題】感知回路の雑音感受性を最小にするとともに、回路の少なくとも一部に対する電力を管理して、消費電力を少なくした通信システムを提供する。

【解決手段】通信システムはノードのセットを含む。各ノードはトランシーバ・インターフェイスとデジタル・システムを含む。トランシーバは、通信回線とデジタル・システムとの間に結合されており、伝送フォーマットおよび/または伝送プロトコルを対応するノード内の1つまたは複数のデジタル・システムにより認識されるビットのシーケンスに修正する。トランシーバは、デジタル・システムを支持する回路基板から分離された1つまたは複数のモノリシック回路基板に配置される。

(もっと読む)

受信機の同期方法および受信回路

【課題】直交アンダーサンプリング技術を用いた受信機に簡素な同期回路を提供する。

【解決手段】A/D変換器(1)から出力されるベースバンドI/Q信号のサンプル点につき、4/シフトQPSK変調の同一シンボル期間中において+I成分と−I成分または+Q成分と−Q成分の和を時系列的に連続して算出し(21)、時間的変化からシンボルタイミングを再生する(22)。

(もっと読む)

通信システムに用いられるノード

【課題】バスを介して通信する通信システムに用いられるノードにおいて、通信を高速化しても、往復分の伝播遅延および同期補正についての制約が満たされやすくすること。

【解決手段】受信状態では、バス信号109に基づいて生成される受信クロック信号106が示すタイミングをSP(サンプリング・ポイント)とし、サンプリング回路205が受信信号104をサンプリングする。送信状態では、送信クロック信号101が遅延した遅延クロック信号が示すタイミングをSPとし、サンプリング回路205が受信信号104をサンプリングする。また、送信権がある状態では送信クロック信号101は受信クロック信号106とクロック公差がほぼ無い。よって、遅延クロック信号103は受信クロック信号106よりも遅延することになる。よって、送信状態では受信状態よりも遅いタイミングで受信信号104をサンプリングすることになる。

(もっと読む)

送受信装置およびその動作方法

【課題】半導体チップ面積を低減して再生データと再生クロックの生成の誤動作の可能性を軽減する。

【解決手段】送受信装置7は、クロックデータリカバリ回路11、デシリアライザ15、シリアライザ14、PLL回路13、周波数検出器12を具備する。クロックデータリカバリ回路11は受信信号RXとPLL回路13から生成されるクロック信号TXCLKに応答して、再生クロックCLKと再生データDATAを抽出する。デシリアライザ15はCLKとDATAからパラレル受信データDTを生成し、シリアライザ14はパラレル送信データDRとTXCLKからシリアル送信信号TXを生成する。検出器12は受信信号RXとクロック信号TXCLKの周波数の差を検出して周波数制御信号FCSを生成して、信号FCSに応答して周波数の記差を低減するように、PLL回路13はTXCLKの周期を制御する。

(もっと読む)

1 - 20 / 84

[ Back to top ]