Fターム[5K047MM25]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本素子 (364) | メモリ;バッファメモリ (323) | エラスティックメモリ (12)

Fターム[5K047MM25]に分類される特許

1 - 12 / 12

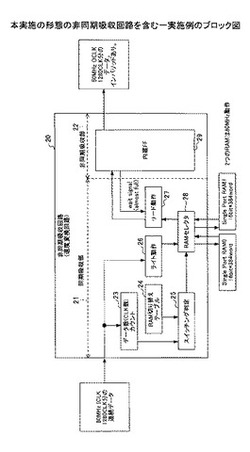

非同期吸収回路、画像処理装置及びプログラム

【課題】画像1ライン分よりも少ない記憶容量の複数のシングルポートメモリを用いて非同期吸収を行うことができる非同期吸収回路、画像処理装置及びプログラムを提供することを課題とする。

【解決手段】少なくとも画像1ライン分よりも少ない記憶容量の複数の記憶手段への入力データの書き込み動作を行う書き込み動作手段と、記憶手段からの出力データの読み出し動作を行う読み出し動作手段と、書き込み及び読み出しの対象となる記憶手段を切り替える切り替え手段と、画像1ライン分の入力データを複数に分けたブロックデータが記憶手段に振り分けられるタイミングに基づき、切り替え手段による記憶手段の切り替えを制御する切り替え制御手段と、入力データのクロック信号と出力データのクロック信号との非同期吸収を行う非同期吸収手段とを有することにより上記課題を解決する。

(もっと読む)

シリアル通信回路

【課題】低消費電力モードから復帰時にその受信シンボルでスキュー調整を実施することができ、通常通信状態への迅速な復帰を行う。

【解決手段】符号化された複数のレーンのシリアル受信信号からクロックの再生を行い、受信シンボルを各レーン毎に再生し、バイトアライン及びSP変換後、復号化して複数のレーンの受信シンボルを同一のクロックに同期した受信シンボルに変換して出力する物理層受信回路と、複数のレーンの受信シンボルに対してレーン間のシンボルスキューを調整するレーン間スキュー調整回路とを備えたシリアル通信回路において、所定の検出基準シンボルを受信シンボルからレーン毎に検出し、カウンタ回路により検出信号に応答して検出信号の計数を開始し、カウンタ値の選択信号に対応する遅延量だけ、物理層受信回路から出力される複数のレーンの受信シンボルに対して遅延させてレーン間のシンボルスキューを調整する。

(もっと読む)

信号伝送装置

【課題】N(Nは3以上の整数)チャネルの信号を伝送すること。

【解決手段】各チャネルCH1〜CH5のうち、クロック源が共通のチャネルの中からクロック源に同期している正常な一のクロックを選択するM(Mは1以上N未満の整数)個のクロック選択部150と、クロック選択部150が選択したクロックのジッタを抑圧するM個のジッタ抑圧部160とを備える。

(もっと読む)

クロック乗せ換え回路およびクロック乗せ換え方法

【課題】より安定してクロックの乗せ換えを行う。

【解決手段】2ポートRAMは、独立して書き込みと読み出しが可能であり、書き込みアドレス制御部は、2ポートRAMにおいて、入力データが書き込まれる書き込みアドレスを制御し、ブランクアドレス検出部は、書き込みアドレスにおいて、入力データが書き込まれないブランクアドレスを検出し、読み出しアドレス変換部は、2ポートRAMにおいて、ブランクアドレス以外の書き込みアドレスを、出力データが読み出される読み出しアドレスに変換する。本技術は、例えば、データ伝送システムに適用することができる。

(もっと読む)

データ転送システムおよびデータ転送方法

【課題】システム性能を低下させることなくマスタから周辺回路へデータを転送することが可能なデータ転送システムを提供することである。

【解決手段】本発明にかかるデータ転送システムは、マスタM1〜M3と、マスタから第1のバス2を介して出力された複数のデータD1〜D3を入力し第2のバス4を介して当該データを出力するバスブリッジ3と、バスブリッジ3から出力されたデータD1〜D3を保持するライトバッファWB1〜WB3および当該ライトバッファWB1〜WB3から出力されたデータD1〜D3を保持するレジスタR1〜R3を備える周辺回路5と、を備える。バスブリッジ3およびライトバッファは第1のクロックで動作し、レジスタは第1のクロックとは非同期の第2のクロックで動作し、ライトバッファとレジスタとを同期化することでライトバッファからレジスタへデータを転送する。

(もっと読む)

シリアル受信装置並びにシリアル受信装置の制御方法及びプログラム

【課題】EBからのコードの読み出しを一時的に止めることができ、かつEBからのコードの読み出しを止めてもRDチェックが正しく機能するシリアル受信装置を提供する。

【解決手段】制御部30は、パラレルコードのうちSKPシンボルを除いた残りのパラレルコードを記憶手段21に書き込むように書き込み手段22を制御する機能と、記憶手段21に書き込まれたパラレルコードがあるときにのみ当該パラレルコードを読み出すように読み出し手段23を制御する機能と、記憶手段21からパラレルコードを読み出す際にコード有効信号Validを出力する機能とを有する。8B/10Bデコーダ40は、コード有効信号Validが出力されたときに、パラレルコードの復号化及びRD検出を実行し、当該RDと前回のコード有効信号Validが出力されたときに検出したRDとの規則性をチェックする。

(もっと読む)

2つの基準クロックを有するリドライバ及びその動作方法

【課題】2つの基準クロックを有するリドライバ及びその動作方法を提供する

【解決手段】2基準クロックに設計されたリドライバは、インバウンドエラスティックバッファ及びアウトバウンドエラスティックバッファを含む。

ノースブリッジへの送信データ及びノースブリッジからの受信データは、共通基準クロックアーキテクチャを使用する。

外部ブレードへの送信データ及び外部ブレードからの受信データは、個別基準クロックアーキテクチャを使用する。

(もっと読む)

エラスティックストア回路

【目的】データの欠落やデータエラー等の障害を生じることなく書込アドレス及び読出アドレス間の位相調整を実行可能なエラスティックストア回路を提供する。

【解決手段】メモリの書込アドレス及び読出アドレスのアドレス差を判別するアドレス差判別部と、上記アドレス差が所定値よりも小なる場合に、アドレス差が増加するように読出アドレスを調整する位相調整部と、入力データの到来期間を判別し、上記到来期間において位相調整部による読出アドレスの調整を禁止する位相調整禁止部と、を有している。

(もっと読む)

非同期信号の同期化多重方法および装置

【課題】複数の非同期信号の処理が回路規模を増大させることなく実行可能となる非同期信号の同期化多重方法および装置を提供する。

【解決手段】クロック位相吸収部10.1〜10.Mにより非同期STM−N信号D1〜DMがシステムクロックCLKsysに乗り換えられる。システムクロックCLKsysに従って、MSOH終端部11、ポインタ受信部12およびメモリ部13が非同期STM−N信号に対してMSOH終端処理やフレーム位相吸収処理をシリアルに実行する。フレーム位相吸収された同期化信号D1_sync〜DM_syncがポインタ送信部6によりポインタ値の付け替え等の処理により多重化される。

(もっと読む)

受信装置

【課題】複数の伝送路からデータを受信し、伝送路間に生じるスキューも補正可能である受信装置を提供する。

【解決手段】複数の伝送路L0乃至L3それぞれから複数のデータブロックを有するデータ列を受信する受信装置2において、送信シンボル数で連なる複数のタイミング調整用シンボルを伝送路L0乃至L3間で同一サイクルに読み出すべきデータブロック同士のマーカとしてデータブロック間に挿入したデータ列それぞれを書き込み送信シンボル数を増減したエラスティックシンボル数のタイミング調整用シンボルが連なるデータ列を読み出しクロックCLKrに同期して読み出す複数のエラスティックバッファEB0乃至EB3と、データ列を書き込みタイミング調整用シンボルのデスキューシンボル数をエラスティックシンボル数から増減して送信シンボル数に等しくしタイミング調整用シンボルをマーカとして読み出しクロックCLKrに同期して伝送路L0乃至L3間のデータブロックを同一サイクルに読み出すデスキュー回路5を有する。

(もっと読む)

ディジタル伝送リンク上でのデータの受信の方法および装置

【課題】サンプリングされたデータに対して動作するオーバサンプリングされたシーケンスの検出器を提供する。

【解決手段】検出器は、異なるサンプリング位相についてのサンプルシーケンスを別個に分析し、それから最も信頼性のある検出を可能にするサンプルシーケンスを選ぶ。異なるサンプリング位相について、検出器は、簡単なシンボル単位での検出よりも改善を図るために、ルックビハインドおよびルックアヘッド情報のうちある程度の量を調べる。オーバサンプリングされた情報は、さらに検出パフォーマンスを改善するために用いられる。

(もっと読む)

エラスティックバッファ

【課題】本発明は、エラスティックバッファのオーバーフロー状態とアンダーフロー状態とを検出することを特徴とする。

【解決手段】第1、第2、第3の初期値データを転送する第1、第2、第3のリングカウンタと、第1のリングカウンタの出力を保持する第1の記憶回路と、第2のリングカウンタの出力と第1の記憶回路の出力が入力される第1のアンド回路群と、第3のリングカウンタの出力と第1の記憶回路の出力が入力される第2のアンド回路群と、第1のアンド回路群の出力が入力される第1のオア回路と、第2のアンド回路群の出力が入力される第2のオア回路と、第1のオア回路の出力を記憶する第2の記憶回路と、第2のオア回路の出力を記憶する第3の記憶回路と、第1、第2のオア回路の出力と第2、第3の記憶回路の出力とをデコードしてオーバーフロー信号およびアンダーフロー信号を出力するデコード回路とを具備している。

(もっと読む)

1 - 12 / 12

[ Back to top ]