Fターム[5L106DD00]の内容

半導体メモリの信頼性技術 (9,959) | 試験 (2,465)

Fターム[5L106DD00]の下位に属するFターム

並列的に試験 (233)

テストデータを並列的に書き込むもの (129)

スキャンパス (93)

試験モードへの切換え (576)

機密保護と関連するもの (10)

試験装置 (1,037)

しきい値の測定 (72)

アクセスタイムの測定 (43)

テスト列(行)を持つもの (19)

加速試験、ストレス (225)

Fターム[5L106DD00]に分類される特許

1 - 20 / 28

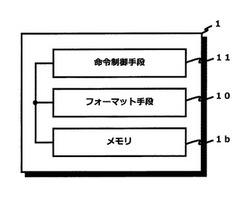

内部状態に応じたフォーマット処理を実行できる半導体記憶装置及び半導体記憶装置のフォーマット処理方法

【課題】半導体記憶装置の内部状態に応じてフォーマット処理できる半導体記憶装置を提供する。

【解決手段】半導体記憶装置1の内部状態に応じてフォーマット処理できるように、半導体記憶装置1は、フォーマット処理をする際に、フォーマット処理の状態を示す内部状態情報をフォーマット処理するメモリ1bから読み出し、メモリ1bから読み出した内部状態情報に従い、メモリ1bのフォーマット処理の状態を判定し、判定した該状態に適した処理を実行するフォーマット手段10を備える。

(もっと読む)

半導体記憶装置とそのセルリーク検出方法

【課題】SRAM回路の製品信頼性が低下する問題があった。

【解決手段】セルリークの判定機能を有した半導体記憶装置であって、相補性ビット線対と、前記ビット線対に接続され、セル選択時に前記ビット線対に印加された値に応じた値をセルノードに記憶するメモリセルと、セルリークテスト期間において、選択状態の前記メモリセルに対し、前記ビット線対の一方に第1の値を印加させ、その後、非選択状態の前記メモリセルの駆動電源の供給を停止し、且つ、前記ビット線対の一方に対して前記第1の値と逆の第2の値を印加させ、前記ビット線対の一方に対応する側の前記メモリセルの第1のセルノードの値に応じて、当該半導体記憶装置のセルリークを判定するテスト制御回路と、を有する半導体記憶装置。

(もっと読む)

識別情報を有するメモリ装置

【課題】メモリ装置に関する所定の情報、すなわち製造工場、製造日、ウェーハ番号、ウェーハ上の座標等を含む情報格納手段を有するメモリ装置を提供する。

【解決手段】複数個のバンクを含むメモリ装置において、各バンク0〜3が、アドレス信号を受信してデコーディングするプリデコーダ11と、メモリ装置に関する情報を格納する情報格納手段12と、情報格納手段12から出力される情報を受信する入出力ラインドライバ13と、入出力ラインドライバ13の出力信号を受信するデータ出力ドライバ14と、データ出力ドライバ14の出力信号を受信するデータパッドDQ0とを備え、情報格納手段12が、プリデコーダ11の出力信号を受信してメモリ装置に関する情報を出力し、情報格納手段12内に格納されたメモリ装置に関する情報が、メモリ装置のパッケージング後において、テストモード信号により同時に読み出されるように構成されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】ワード線リークの検出のための特別のパッドやスイッチを必要とせず、ワード線リークの発生箇所を迅速かつ確実に検出する。

【解決手段】制御回路4は、ワード線のリーク状態を判定するワード線リークテストを実行する場合において、テストパターンデータを書き込まれたメモリセルアレイ100に接続されたワード線に、テストパターンデータに対応した電圧を電圧制御回路20から印加する。その後、転送トランジスタ12を非導通状態とすることによりワード線をフローティング状態に設定する。転送トランジスタ12の非導通状態への切替えから所定時間経過後、センスアンプ回路30を作動させてメモリセルアレイ100に対する読み出し動作を実行する。その読み出しの結果をテストパターンデータに対応する期待値と比較する。

(もっと読む)

テスト回路

【課題】正電圧専用のテスタにより、高電圧生成回路、負電圧生成回路の出力をテストすること。

【解決手段】本発明のテスト回路10は、第1分圧回路11と、第2分圧回路12とを具備している。第1分圧回路11は、接地又は基準電圧生成回路1と高電圧生成回路2間に直列接続され、接地電圧又は基準電圧Vrefと高電圧Vp間の電圧を分圧して、正電圧専用のテスタにより測定可能な第1正電圧V1を生成する第1、2の抵抗素子R1、R2と、第1正電圧V1を出力するバッファBFとを備えている。第2分圧回路12は、負電圧生成回路3と基準電圧生成回路1間に直列接続され、負電圧Vnと基準電圧Vref間の電圧を分圧して、正電圧専用のテスタにより測定可能な第2正電圧V2を生成する第1、2の抵抗素子R1、R2と、第2正電圧V2を出力するバッファBFとを備えている。

(もっと読む)

半導体装置及び半導体装置の異常検出方法

【課題】メモリセルの読出し及び書込みを必要としない、簡便なテスト方法を実行することが可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のワード線(WL)と、ワード線ドライバ(4)と、第1検出回路(11、12、15)と、制御回路とを具備する。複数のワード線(WL)は、複数のメモリセルトランジスタ(図示されず)のゲートに接続されている。ワード線ドライバ(4)は、複数のワード線(WL)の各々に選択電圧又は非選択電圧を供給する。第1検出回路(11、12、15)は、ワード線ドライバ(4)を介して複数のワード線(WL)のいずれかに選択電圧を供給するとき、選択電圧を供給する配線(21)を介してワード線ドライバ(4)に流れ込む第1電流を検出する。制御回路は、第1電流に基づいて、複数のワード線(WL)及びワード線ドライバ(4)の異常を検出する。

(もっと読む)

メモリの寿命検出装置及び方法

【課題】メモリの寿命を検出する技術を提供する。

【解決手段】メモリにデータが保持されてからの経過時間を計り、前記経過時間が所定値に達した場合に前記データを前記メモリから読み出し、前記データをエラー無しで読み出せた場合の前記経過時間をデータ保持時間として求め、前記メモリについて求めた第1のデータ保持時間を記憶部に記憶させておき、前記メモリについて前記第1のデータ保持時間以降に求めた第2のデータ保持時間を前記第1のデータ保持時間と比較して前記メモリの寿命を検出する。

(もっと読む)

強誘電体記憶装置の初期化方法、強誘電体記憶装置および電子機器

【課題】過去の熱履歴等によるキャパシタのインプリント現象をリセットし、また、以降の処理によるインプリント現象の影響を低減することができる強誘電体記憶装置の初期化方法を提供する。

【解決手段】本発明に係る強誘電体記憶装置の初期化方法は、下部電極(9)と上部電極(13)との間に配置された強誘電体膜(11)を有するメモリセルがアレイ状に配置された強誘電体記憶装置をパッケージする工程と、前記下部電極および上部電極に電位を印加する検査工程と、前記検査工程の後において、前記上部電極に第1の電位[0V]を、前記下部電極に前記第1の電位より高い第2の電位[Vcc]を印加した後、動作保証温度より高い第1温度で熱処理する工程と、を有する。また、前記第1温度を、前記検査工程における検査温度およびパッケージ工程における処理温度より高くする。

(もっと読む)

半導体装置

【課題】記憶素子の電気抵抗値を正確に測定し、かつレイアウト面積の増大を防ぐことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1端子および第2端子を有する記憶素子Sと、記憶素子Sの第1端子に結合された電流線BLと、電流線BLに結合され、記憶素子Sにデータを書き込むための書き込み電流を電流線BLに流す第1のドライバBLDV2と、電圧を供給するための第1のパッドPD1と、電圧を供給するための第2のパッドPD2と、電圧を供給するための第3のパッドPD3とを備え、第1のパッドPD1および第3のパッドPD3は、第1のドライバBLDV2に結合され、第2のパッドPD2は、記憶素子Sの第2端子に結合されている。

(もっと読む)

半導体装置

【課題】冗長メモリを有する半導体装置において、装置面積を削減するとともに、救済情報の転送時間を短縮する。さらに、救済情報の転送制御をより簡略化する。

【解決手段】第1の救済情報格納手段200は不良セルを有する冗長メモリを救済するための救済情報を記臆する。冗長メモリ101,102は第2の救済情報格納手段400−1を共有し、冗長メモリ111,112,113は第2の救済情報格納手段400−5を共有する。第2の救済情報格納手段400−1,…,400−5は同一個数のシフトレジスタを有し、第1の救済情報格納手段200に直列に接続されており、救済情報が転送される。

(もっと読む)

半導体装置及び半導体メモリテスト装置

【課題】動作用の電圧を供給するポンプ回路を各メモリチップから取り去り、ポンプチップとして別チップにしてMCPチップ内に同梱するようにして、メモリチップの出荷前試験を可能にする半導体装置を提供する。

【解決手段】本発明の一実施の形態に係る半導体装置は、複数の不揮発性半導体記憶装置と、前記複数の不揮発性半導体記憶装置を動作させる昇圧電圧を生成する昇圧回路と、前記複数の不揮発性半導体記憶装置の動作シーケンスに基づいて、前記昇圧回路における前記昇圧電圧の生成動作を制御する昇圧回路制御部と、を備える。

(もっと読む)

冗長回路及び半導体記憶装置

【課題】複数の冗長ROM回路がアドレスに関連して所定の順番でプログラミングされているかを判別可能とする回路及び該回路を備えた半導体装置の提供。

【解決手段】冗長置換したアドレスをヒューズの溶断の有無によって記憶し、アクセスアドレスが冗長置換したアドレスと一致したとき冗長選択信号を出力する第1乃至第nの冗長ROM回路(11〜1n)を備え、アドレス値の大小関係に関して昇順に第1乃至第nの冗長記憶回路の順にリペアアドレスのプログラミングを行うという条件下で、第iの冗長ROM回路より冗長選択信号が出力されていない状態で第i+1の冗長記憶回路から冗長選択信号が出力されたことを検出した場合、SRフリップフロップ(7)をセットし、置換判定出力を逆順とする。

(もっと読む)

検査用半導体集積回路及び検査システム並びに検査方法

【課題】高速DRAMI/Fを備えたLSIを低速LSIテスターで検査する場合の検査内容を拡大し、検査品質を向上することができる検査システムを提供する。

【解決手段】行列状に配置される複数のメモリセルを有し、指示に従ってデータの書き込み読み出し動作を行うメモリセルアレイ101と、送受信特性の変更が可能で、高速な第1のクロック信号に同期して制御信号を検査対象の高速メモリインターフェース回路内蔵半導体集積回路105から取り込み、メモリセルアレイ101への書き込み読み出し動作を制御する第1のメモリインターフェース回路102と、第1のメモリインターフェース回路102の入出力特性を制御する制御部103と、第1のクロック信号とは別の低速な第2のクロック信号に同期してメモリセルアレイ101への書き込み読み出し動作を制御する第2のメモリインターフェース回路104とを備えた検査用半導体集積回路100。

(もっと読む)

メモリモジュールの救済方法、メモリモジュール及び揮発性メモリ

【課題】メモリモジュールの電気的試験で不良と判定された揮発性メモリを交換することなく、不良メモリセルの救済が可能なメモリモジュールの救済方法及びメモリモジュールを提供する。

【解決手段】不良と判定された揮発性メモリのメモリセルに対応する不良行アドレス及び不良列アドレス、並びに不良と判定された揮発性メモリを判別するための不良デバイス情報を不揮発性メモリへ格納しておき、システムの立ち上げ時に、不揮発性メモリに格納されたそれらの情報を、アドレス端子を介して揮発性メモリへ転送して保持し、不良と判定された揮発性メモリのメモリセルに対応するアドレスが入力された場合は、揮発性メモリで保持された情報を用いて該メモリセルに代わって冗長メモリセルへアクセスする。

(もっと読む)

メモリ試験方法

【課題】特別な回路等を追加することなく、複数のメモリの試験結果から一つを選択して結果出力端子へ出力するセレクタの不良を検出すること。

【解決手段】結果出力端子を共有する複数のメモリのうちの一つを着目メモリに定め、その着目メモリにのみ、“0”を書き込む(ステップS1)。次いで、着目メモリ以外のメモリに“1”を書き込む(ステップS2)。次いで、着目メモリから値を読み出し、結果出力端子から外部へシフト出力させる(ステップS3)。次いで、着目メモリ以外のメモリから順次値を読み出し、結果出力端子から外部へシフト出力させる(ステップS4)。これを、すべてのメモリが着目メモリになるまで、繰り返し行う(ステップS1〜4、ステップS5〜8)。

(もっと読む)

基準フェイルビットの確認回路及び不揮発性半導体メモリ装置

【課題】データ消去動作にかかる時間を短縮させうる基準フェイルビット確認回路及びこれを含む不揮発性半導体メモリ装置を提供する。

【解決手段】基準フェイルビット確認回路は、所定のフェイルビットの検出をカウンティングして第1カウンティング信号及び第2カウンティング信号を発生するフェイルビットカウンターと、第1カウンティング信号の遷移及び第2カウンティング信号の遷移に応答して活性化される基準ビット確認信号を発生するビット確認ブロックとを備える。基準ビット確認信号は、第1モードでは第1カウンティング信号の活性に応答し、第2モードでは第2カウンティング信号の活性に応答する。基準フェイルビット確認回路及びこれを含む不揮発性半導体メモリ装置では、消去電圧が段階的に増加する第1モード及び消去電圧が一定に維持される第2モードでの基準フェイル数を異ならせて設定しうる。

(もっと読む)

半導体記憶装置及びその調整方法

【課題】初期設定時にアンチヒューズに書き込まれたデータが確実に得られるようにして内部信号のタイミング調整を実施できる半導体記憶装置及びその調整方法を提供する。

【解決手段】クロックと非同期に供給されるリセット信号を用いてアンチヒューズに書き込まれたデータを出力させるための信号であるDLLReset信号を生成し、該DLLReset信号を、内部信号のタイミング調整に必要なデータが書き込まれた複数のアンチヒューズを備えたアンチヒューズブロックへそれぞれ供給する。

(もっと読む)

メモリモジュール及びそのテスト方法

【課題】メモリモジュール及びそのテスト方法を提供する。

【解決手段】メモリモジュールは、複数のメモリ、及びN個の入力チャンネルを介して外部から印加されるテスト信号を複数のメモリに印加し、印加されたテスト信号に応答して、複数のメモリから出力される複数の出力データをM個のグループに分けた後、外部から入力される出力グループ選択信号によって前記M個のグループのうち、少なくともいずれか一つを選択して、K個の出力チャンネルを介して出力するハブで構成される。従って、透過モードを利用したテスト時に外部の出力グループ選択信号を利用して出力されるDQグループをOn−the−Fly形式で選択することができる。

(もっと読む)

半導体集積回路装置

【課題】一つのブロック全体のプログラムループ回数を簡単に知ることができる不揮発性半導体記憶装置を有した半導体集積回路装置を提供すること

【解決手段】ページバッファに記憶された書き込みデータに応じて、データが書き込まれる複数のメモリセルと、複数のメモリセルへのデータ書き込みに要したプログラムループ回数を累積記憶するプログラムループ累積カウンタ33と、を具備し、プログラムループ累積カウンタ33に累積記憶されたプログラムループ回数を出力することを特徴とする。

(もっと読む)

半導体装置及びテスト方法

【課題】

評価・解析において、特性の劣化、不良等が周波数同期回路に因るのか否か等、不良原因の特定を容易化する半導体装置の提供。

【解決手段】

外部クロック端子13、14から外部クロック信号を入力して前記外部クロック信号に同期した信号を生成するDLL回路10と、外部端子15から入力されたクロック信号と、DLL回路10からの出力信号とを入力し、テストモード信号に基づき、テスト時には、外部端子15から入力されたクロック信号を出力し、通常動作時には、DLL回路10からの出力信号を出力するセレクタ11を備える。

(もっと読む)

1 - 20 / 28

[ Back to top ]