Fターム[5L106EE00]の内容

半導体メモリの信頼性技術 (9,959) | 障害・試験箇所 (1,040)

Fターム[5L106EE00]の下位に属するFターム

Fターム[5L106EE00]に分類される特許

1 - 10 / 10

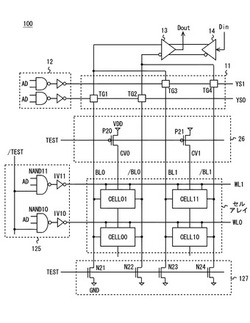

半導体記憶装置とそのセルリーク検出方法

【課題】SRAM回路の製品信頼性が低下する問題があった。

【解決手段】セルリークの判定機能を有した半導体記憶装置であって、相補性ビット線対と、前記ビット線対に接続され、セル選択時に前記ビット線対に印加された値に応じた値をセルノードに記憶するメモリセルと、セルリークテスト期間において、選択状態の前記メモリセルに対し、前記ビット線対の一方に第1の値を印加させ、その後、非選択状態の前記メモリセルの駆動電源の供給を停止し、且つ、前記ビット線対の一方に対して前記第1の値と逆の第2の値を印加させ、前記ビット線対の一方に対応する側の前記メモリセルの第1のセルノードの値に応じて、当該半導体記憶装置のセルリークを判定するテスト制御回路と、を有する半導体記憶装置。

(もっと読む)

半導体装置

【課題】簡単制御と低電圧で試験することができ、テスト時間の増大を回避し、Vtアンバランスの大きいセンスアンプを効率よく検出する。

【解決手段】相補の第1(BLT/BLB)、第2(LIOT/B)、及び第3のデータ線対(MIOT/B)と、前記第1のデータ線対に接続される第1のアンプ(SA)と、前記第1と第2のデータ線対間の接続を制御する第1のスイッチ対(Yスイッチ)と、前記第2と第3のデータ線対間の接続を制御する第2のスイッチ対(401、402)と、前記第2のデータ線対を第1の電圧にプリチャージする第1プリチャージ回路403とを備え、テスト制御信号(TSAVTCHCKT)がテスト動作を示すとき、前記第2のスイッチ対(401、402)を非導通とし、前記第1のプリチャージ回路403により前記第2のデータ線対に印加される前記第1の電圧が、前記第1のスイッチ対を介して、第1のアンプに印加される。

(もっと読む)

半導体装置及びそのテスト方法

【課題】第1メモリと、第1メモリとはデータの記憶方式が異なる第2メモリとを同時にテストすること。

【解決手段】本発明の半導体装置(100)は、複数のセクタに分割された第1メモリセルアレイ(10;10−1)と消去時間設定レジスタ(14)とを備えた第1メモリ(101)と、第1メモリセルアレイ(10;10−1)とはデータの記憶方式が異なる第2メモリセルアレイ(20;20−1)を備えた第2メモリ(102)とを具備している。まず、1セクタに格納されたデータを消去する消去時間を保証するためのセクタ消去保証時間を消去時間設定レジスタ(14)に設定する。次に、セクタ消去保証時間内に複数のセクタのうちの選択セクタに格納されたデータを消去するセクタ消去テストを実行し、セクタ消去テストが実行されているときに、第2メモリセルアレイ(20;20−1)に対するデータ保持テストを実行する。

(もっと読む)

半導体メモリ装置の内部信号モニタ装置及びモニタ方法

【課題】モニタしようとする内部信号を高精度で検証することができ、内部信号のモニタ時、従来よりも容易かつ迅速に検証することのできる半導体メモリ装置の内部信号モニタ装置及びモニタ方法を提供すること。

【解決手段】テストモード信号に応答して、モニタしようとする内部信号を受信してモニタソース信号として出力する内部信号入力手段と、前記テストモード信号に応答して、前記モニタソース信号を予定された任意のパッドに送信する内部信号出力手段とを備える半導体メモリ装置の内部信号モニタ装置を提供し、半導体メモリ装置の内部信号モニタ方法において、テストモード信号に応答して、モニタしようとする1つ又は複数の内部信号を受信するステップと、前記テストモード信号に応答して、前記内部信号を予定された任意のパッドに伝達するステップとを含む半導体メモリ装置の内部信号モニタ方法を提供する。

(もっと読む)

半導体装置

【課題】テスト動作時において通常動作時とは異なる電圧が内部電源配線に供給される半導体装置において、チップ面積の増大を最小限に抑制しつつ、プリチャージ電位などの通常電圧を安定供給する。

【解決手段】内部電源配線200と、第1の電源回路101と第2の電源回路102とを備えている。第1の電源回路101は、通常動作時において内部電源配線200に通常電圧を供給する通常電圧発生回路111と、テスト動作時において内部電源配線200にテスト電圧を供給するテスト電圧発生回路112とを備えている。一方、第2の電源回路102は通常電圧発生回路111のみを備えている。これにより、テスト電圧発生回路112よりも通常電圧発生回路111の数の方が多くなることから、チップ面積の増大を抑制しつつ、プリチャージ電位などの通常電圧を安定供給することが可能となる。

(もっと読む)

試験装置および試験方法

【課題】レイテンシを変更可能な被試験メモリの良否を効率的に判定する。

【解決手段】予め設定されたアルゴリズムに基づいて、被試験メモリに供給すべき制御コマンドと、アドレスと、被試験メモリに書き込むべき書込データおよび被試験メモリから読み出した読出データの期待値を含む試験パターンを順次生成するパターン発生器と、制御コマンド、アドレスおよび書込データを被試験メモリに供給し、被試験メモリが出力する読出データを受け取る信号入出力部と、読出データと期待値とを比較して、読出データの良否を判定する判定部と、パターン発生器が生成した試験パターンがレイテンシ設定コマンドであるか否かを検出する検出部と、検出部がレイテンシ設定コマンドを検出した場合に、被試験メモリへのデータ書き込みにおいて信号入出力部の書込レイテンシおよび読出レイテンシを、レイテンシ設定コマンドに応じた値に設定する設定部とを備える試験装置。

(もっと読む)

半導体記憶装置及びその調整方法

【課題】初期設定時にアンチヒューズに書き込まれたデータが確実に得られるようにして内部信号のタイミング調整を実施できる半導体記憶装置及びその調整方法を提供する。

【解決手段】クロックと非同期に供給されるリセット信号を用いてアンチヒューズに書き込まれたデータを出力させるための信号であるDLLReset信号を生成し、該DLLReset信号を、内部信号のタイミング調整に必要なデータが書き込まれた複数のアンチヒューズを備えたアンチヒューズブロックへそれぞれ供給する。

(もっと読む)

第2遅延回路を介してトリミングされる第1遅延回路を有する集積回路チップ、および遅延時間を調整する方法

【課題】プロセス変動による時間遅延の問題を低減または解決する。

【解決手段】第1遅延回路と第2遅延回路とを備える集積回路チップである。第1遅延回路は、信号を第1遅延時間遅延するように形成されている第1遅延回路接続形態を有している。第2遅延回路は、回路ループにおいて第2遅延時間を供給するように構成されている第2遅延回路接続形態を有している。回路ループは、モニターされるように形成されており、発振信号を供給する。第2遅延回路接続形態は、第1遅延回路接続形態と実質的に同じであり、第1遅延回路は、第2遅延時間と発振信号とに基づいて第1遅延時間を調節するためにトリミングされるように形成されている。

(もっと読む)

半導体装置及びテスト方法

【課題】

評価・解析において、特性の劣化、不良等が周波数同期回路に因るのか否か等、不良原因の特定を容易化する半導体装置の提供。

【解決手段】

外部クロック端子13、14から外部クロック信号を入力して前記外部クロック信号に同期した信号を生成するDLL回路10と、外部端子15から入力されたクロック信号と、DLL回路10からの出力信号とを入力し、テストモード信号に基づき、テスト時には、外部端子15から入力されたクロック信号を出力し、通常動作時には、DLL回路10からの出力信号を出力するセレクタ11を備える。

(もっと読む)

同期型半導体記憶装置

【課題】外部クロック信号に対する同期動作完了までの時間を短縮することが可能な内部同期信号発生回路を有する同期型半導体記憶装置を提供する。

【解決手段】同期信号発生回路100は、外部クロック信号Ext.CLKを受けて、所定の時間遅延して出力する遅延回路110と、遅延回路110の出力と外部クロック信号Ext.CLKの位相を比較する位相比較器120と、位相比較器120の比較結果に基づいて、出力ノード140aに供給する定電流値をディジタル的に変化させる可変定電流源回路140と、出力ノード140aに供給される定電流値に応じて、遅延回路110の遅延量を調整する遅延制御回路150とを含む。遅延回路110の遅延量が、位相比較結果に応じて線形に変化する定電流値に応じて制御される。

(もっと読む)

1 - 10 / 10

[ Back to top ]