国際特許分類[C23C16/56]の内容

化学;冶金 (1,075,549) | 金属質材料への被覆;金属質材料による材料への被覆;化学的表面処理;金属質材料の拡散処理;真空蒸着,スパッタリング,イオン注入法,または化学蒸着による被覆一般;金属質材料の防食または鉱皮の抑制一般 (47,648) | 金属質への被覆;金属材料による材料への被覆;表面への拡散,化学的変換または置換による,金属材料の表面処理;真空蒸着,スパッタリング,イオン注入法,または化学蒸着による被覆一般 (43,865) | ガス状化合物の分解による化学的被覆であって,表面材料の反応生成物を被覆層中に残さないもの,すなわち化学蒸着 (14,497) | 後処理 (277)

国際特許分類[C23C16/56]に分類される特許

1 - 10 / 277

成膜装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

半導体装置の製造方法

【課題】キャパシタとコンタクトパッド間のコンタクト抵抗の上昇を防ぎ、書き込み・読み出し不良を低減する、装置特性が優れた半導体装置を提供する。

【解決手段】タングステン膜8bを形成する工程と、タングステン膜8b上に窒化チタン膜からなる下部電極13を形成する工程と、酸化雰囲気下で窒化チタン膜に熱処理を行うことにより窒化チタン膜を酸化する工程と、下部電極13上に容量絶縁膜14を形成する工程と、容量絶縁膜14上に上部電極15を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

シリコン酸化物膜の成膜方法

【課題】 表面ラフネスが良好なシリコン酸化物膜を得ることが可能なシリコン酸化物膜の成膜方法を提供すること。

【解決手段】 下地1上にシード層2を形成する工程と、シード層2上にシリコン膜3を形成する工程と、シリコン膜3及びシード層2を酸化し、下地1上にシリコン酸化物膜4を形成する工程と、を具備する。

(もっと読む)

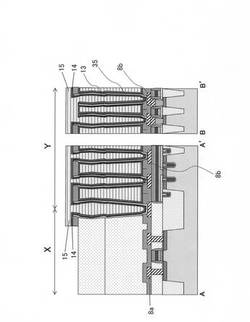

絶縁膜形成方法及び絶縁膜形成装置

【課題】信号遅延の抑制と絶縁性の向上との両立が可能な絶縁膜形成方法及び絶縁膜形成装置を提供する。

【解決手段】

シリコン貫通電極用の貫通孔が形成されたシリコン基板を備える基板Sに絶縁膜を形成するに際し、抵抗加熱ヒータ33Hによって加熱された基板Sを収容する反応室31Sに、酸素ガス及びキャリアガスであるアルゴンガスと混合されたZr(BH4)4を供給する。そして、Zr(BH4)4を上記基板S上で熱酸化することによって、基板Sの表面及び上記貫通孔の内側面にジルコニウム、ホウ素、及び酸素を含む絶縁膜の一つであるZrBO膜を形成する。

(もっと読む)

固体撮像素子およびその製造方法、電子情報機器

【課題】受光部への光入射効率を悪化させることなく、金属コンタミネーション起因による白傷を低減する。

【解決手段】複数の受光部3の上方で、パターニングされた3層の導電層(ここでは金属層の第3配線7c)上の第4絶縁膜6d上に、装置側で設定するプラズマ発生エネルギーを示すRFパワーを、金属コンタミネーション起因による白傷を抑制するように700W〜1500Wに設定するプラズマCVD法によりパッシベーション膜8を成膜するパッシベーション膜成膜工程と、熱処理によりパッシベーション膜8から水素を脱離させるシンター処理を行うシンター処理工程とを有している。このパッシベーション膜8は、その膜厚が50〜100nmである。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーション耐性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】 基板上に絶縁膜を形成する工程と、前記絶縁膜をエッチングして配線溝を形成する工程と、前記配線溝内に銅膜を形成し、銅配線を形成する工程と、前記銅配線及び前記絶縁膜の表面を平坦化する工程と、平坦化された前記銅配線及び絶縁膜上に金属膜を形成する工程と、酸素を含んだ雰囲気中で加熱を行うことにより前記銅配線上の前記金属膜と前記銅配線とを選択的に反応させて合金膜を形成するとともに前記絶縁膜上の前記金属膜を酸化して絶縁性の膜に変化させる工程と、前記合金膜及び前記絶縁性の膜上にブロック膜を形成する工程とを備えた半導体装置の製造方法。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

トレンチ内に誘電層を形成する方法

【課題】半導体構造の形成方法、より具体的にはトレンチ内における誘電層の形成方法を提供する。

【解決手段】半導体構造を形成する方法は、基板上にシリコン酸化被膜を形成するために、シリコン前駆体と原子酸素前駆体を約150℃以下の処理温度において反応させることを含む。シリコン酸化被膜は酸素含有環境内で紫外線(UV)硬化される。

(もっと読む)

膜形成方法および膜形成装置

【課題】良質な膜を簡便に形成する膜形成方法および膜形成装置を提供することである。

【解決手段】実施形態の膜形成方法は、少なくとも1つの有機官能基と、加水分解を起こす1つの官能基と、を含む有機ケイ素化合物を、大気雰囲気において基板の表面に供給する第1の工程と、前記有機ケイ素化合物を前記基板の前記表面に供給後、前記有機官能基を酸化し、前記基板の前記表面上にケイ素と酸素とを含む層を形成する第2の工程と、を備える。

(もっと読む)

1 - 10 / 277

[ Back to top ]