国際特許分類[G06F1/10]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | クロック信号またはそれから直接誘導された信号の発生または分配 (1,875) | クロック信号の分配 (273)

国際特許分類[G06F1/10]に分類される特許

1 - 10 / 273

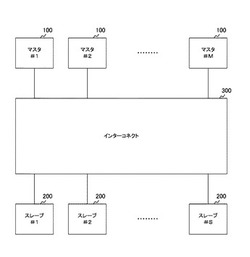

クロックゲーティング回路およびバスシステム

【課題】トランザクションを単位として扱うバスシステムにおいて消費電力を低減する。

【解決手段】クロックゲーティング回路は、クロックイネーブル信号生成部とマスククロック生成部とを備える。クロックイネーブル信号生成部は、バスシステムを複数のリージョンに分割した各々においてアウトスタンディングトランザクションの数を計数することにより複数のリージョンの各々のためのクロックイネーブル信号を生成する。マスククロック生成部は、複数のリージョンの各々のためのクロックイネーブル信号によってクロックをマスクしてマスククロックを生成する。

(もっと読む)

半導体装置

【課題】不揮発性メモリを備えた半導体装置において、高速動作の場合と低速動作の場合とに切替え可能にするとともに、低速動作時の消費電力を従来よりも削減する。

【解決手段】半導体装置1において、クロック生成回路40は、高周波モード時には低周波モード時よりも周波数の高いクロックを生成する。中央処理装置20は、データバス11を介して不揮発性メモリ10から読み出された読出データを取得する。クロック遅延部50Aは、縦続接続された複数段のバッファ55を介した第1の経路51と複数段のバッファ55を迂回した第2の経路52とを含む。クロック遅延部50Aは、高周波モード時には、クロック生成回路40からのクロックを第1の経路51を介して中央処理装置20に供給し、低周波モード時には、クロック生成回路40からのクロックを第2の経路52を介して中央処理装置20に供給する。

(もっと読む)

クロック分配回路及びクロック分配回路の形成方法

【課題】 28nm以降の半導体プロセスでは、チップ内バラツキが顕著になったため、フィードバックパスにトランジションフォルトが発生する頻度が上がった。従来技術ではフィードバックパスのトランジションフォルトが発生した場合の対策がなく、歩留まり低下につながる。

【解決手段】 クロック信号が分配されるクロックツリーと、クロックツリーの異なる分岐点から出力される複数のフィードバッククロック信号を受信し、各フィードバッククロック信号の位相差を検知する位相比較回路とを有する。位相比較回路によって検知した位相差に基づいて、半導体集積回路内の製造バラツキを補正するためのバラツキ補正済フィードバッククロック信号を生成するフィードバッククロック信号生成回路を有する。フィードバッククロック信号生成回路によって生成されたバラツキ補正済フィードバッククロック信号と基準クロック信号との位相差が小さくなるようにクロック信号を遅延する位相調整回路を有する。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

デイジーチェーンカスケードデバイス

【課題】デバイスをデイジーチェーンカスケード配列でシリアルに連結する。

【解決手段】デバイスはデイジーチェーンカスケード配列で連結され、第1デバイスの出力部は、データ、アドレス及びコマンド情報等の情報並びに制御信号を第2デバイスに第1デバイスから転送するように、デイジーチェーンカスケードの後方にある第2デバイスの入力部に連結されている。デイジーチェーンで連結されたデバイスは、シリアル入力部SIとシリアル出力部SOとを備える。情報がデバイスにSIを通じて入力され、該情報がデバイスからSOを通じて出力される。デイジーチェーンカスケードの前方のデバイスのSOは、デイジーチェーンカスケードの後方のデバイスのSIに連結されている。前方のデバイスにSIを通じて入力された情報は、該デバイスのSOを通じて出力される。該情報は次いで、後方のデバイスのSIに転送される。

(もっと読む)

クロック供給回路及び半導体集積回路

【課題】高速なクロックを内部回路に供給するためには、消費電力の高いクロックバッファを必要とする。そのため、高速なクロックを低消費電力で供給するクロック供給回路及び半導体集積回路が、望まれる。

【解決手段】クロック供給回路は、電圧制御発振器を含むPLL回路と、電圧制御発振器の発振周波数を制御する発振制御電圧に基づいて、電圧制御発振器の発振周波数と略同一の周波数を持つクロックを、PLL回路のリファレンスクロックに同期させて出力する自己発振型バッファ回路と、を備えている。

(もっと読む)

電子機器

【課題】複数の回路間で伝送路を介して第1クロックを伝送し、それぞれの回路で第1クロックを分周あるいは逓倍した第2クロックを用いる電子機器において、第1クロックと第2クロックとの伝送路でのクロストークを防止する。

【解決手段】リセット信号に基づいて動作を開始し、第1クロックを分周/逓倍して第2クロックを生成する第1分周/逓倍回路を備えた第1回路と、伝送路を介して入力したリセット信号に基づいて動作を開始し、伝送路を介して入力した第1クロックを分周/逓倍して第2クロックを生成する第2分周/逓倍回路を備えた第2回路と、を含むことを特徴とする電子機器。

(もっと読む)

集積回路、クロックゲート回路、および方法

【課題】本発明は、集積回路に渡ってクロック信号を分配する時に消費される、電力の量を減少するための技術に関する。

【解決手段】集積回路2は、動作クロック周波数を有する動作クロック信号に応じて作動するように配設される、機能回路4、6を備える。電力を節約するために、クロック信号は、動作クロック周波数よりも低い分配クロック周波数で、集積回路2に渡って分配される。クロック変換器10は、機能回路4、6の動作を制御するために、分配クロック信号を動作クロック信号に変換するように提供される。

(もっと読む)

電子機器

【課題】複数の接続部に動作クロックを出力すると、それぞれのクロックの立ち上がり及び立ち下がりにより生じる電磁波の周りへの影響が大きい。

【解決手段】電子機器は、信号の授受する動作クロックの周波数が同じ複数の外部機器が接続される複数の接続部と、複数の接続部に対して互いに位相をずらした動作クロックを出力するクロック出力部とを備える。クロック出力部は、複数の接続部のうちの2つに対して互いに逆位相の動作クロックを出力する。

(もっと読む)

集積回路設計装置及び集積回路設計方法

【課題】クロック線上における消費電力を効果的に抑えることが可能な集積回路を設計する集積回路設計装置を提供する。

【解決手段】開示の装置は、消費電力算出手段と、消費電力比較手段と、クロックツリー生成手段とを備える。消費電力算出手段は、クロック線上における、クロックゲーティングセルをクロックソース側及びクロックシンク側に配置した場合の第1及び第2の消費電力を算出する。クロックツリー生成手段は、第1及び第2の消費電力の比較により、消費電力が小さいと判定された方の配置の仕方で、クロックゲーティングセルをクロック線上に配置する。ここで、消費電力算出手段は、クロックゲーティングセルのイネーブル率と、クロック線上における消費電力のダイナミック電力成分とスタティック電力成分との比率と、に基づいて、第1及び第2の消費電力を算出する。

(もっと読む)

1 - 10 / 273

[ Back to top ]