国際特許分類[G06F1/24]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | リセット手段 (409)

国際特許分類[G06F1/24]に分類される特許

1 - 10 / 409

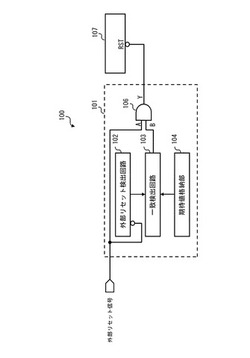

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】電源投入後から外部リセット信号が最初にアクティブになるまでの期間にリセット信号をアクティブにすることが可能なリセット信号生成回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路101は、外部リセット信号が最初にアクティブになったことを検出する外部リセット検出回路102と、外部リセット検出回路102の検出結果が、外部リセット信号が最初にアクティブになる前であることを示す場合、外部リセット信号に関わらずリセット信号をアクティブにする制御回路と、を備える。

(もっと読む)

半導体集積回路装置及びそれを用いた電子機器

【課題】クロック信号のスペクトラムを拡散することによって電磁放射ノイズを低減する半導体集積回路装置において、規模が小さくシンプルで確実に動作する回路構成を用いて、デッドロックや誤動作から確実に復帰する。

【解決手段】この装置は、基準クロック信号に基づいて多相クロック信号を出力する遅延回路と、多相クロック信号の内の1つを選択信号に従って選択することにより変調クロック信号を生成する選択回路と、変調クロック信号の生成が停止したときにリセット信号を出力するクロック停止検出回路と、リセット信号によってリセットされ、変調クロック信号に含まれているパルスの数をカウントすることにより、周期的にタイミング信号を生成するタイミング信号生成回路と、タイミング信号に応答して、変調クロック信号の周波数を所定の変調周期において増減させるように選択信号を生成する制御回路とを具備する。

(もっと読む)

情報処理装置および情報処理装置の制御方法

【課題】ユーザがバッテリを取り外すことが出来ない情報処理装置において、不具合が起きた場合に、容易に強制終了させること。

【解決手段】二次電池と、情報処理装置に所定の処理を実行させるための機能が割り当てられている複数のスイッチと、前記複数のスイッチの内の電源スイッチの操作に応じて情報処理装置の電力管理を行う電力管理コントローラと、前記二次電池から供給される電力を用いて前記情報処理装置を構成するコンポーネントに動作電源を供給する電源回路と、前記電力管理コントローラからの要求に応じて前記電源回路を制御する電源コントローラとを具備し、前記電源コントローラは、前記複数のスイッチの内の2以上のスイッチに結合され、前記2以上のスイッチに対する所定の操作に応答して、前記電力管理コントローラへのリセット信号を制御することによって前記電力管理コントローラに初期化処理を実行させる。

(もっと読む)

電源供給制御装置およびヘッドホン

【課題】リセットスイッチを設けずに、少ない部品点数でもって、情報処理装置の暴走に対処する。

【解決手段】電源を情報処理装置に対して供給する場合に一の状態を継続するスイッチを有し、スイッチが一の状態とされると、電源が情報処理装置に供給されると共に、情報処理装置の第1のポートが予め設定された所定の論理レベルとされ、第1のポートが所定の論理レベルとされたことを情報処理装置が検出して第2のポートを予め設定された所定の論理レベルとする。スイッチが一の状態から他の状態となると、第1のポートが所定の論理レベルと異なる論理レベルとされ、情報処理装置が第1のポートの論理レベルの変化を検出して終了処理を行い、終了処理の後に第2のポートを所定の論理レベルと異なる論理レベルとして、電源供給がオフとされる。

(もっと読む)

情報処理装置、プログラムおよび画像形成装置

【課題】電源がオンに移行したとき、ハードウエアの構成に対応して初期設定ができる情報処理装置等を提供する。

【解決手段】電源ユニットから電力が供給されて、情報処理装置の電源がオンになると、ハードウエアリセット(HWリセット)が行われる(ステップ101)。次いで、ハードウエア(HW)による初期設定が行われる(ステップ102)。そして、初期設定プログラムによる初期設定が行われる(ステップ103)。その後、スマートリセットが行われる(ステップ104)。そして、OS、デバイスドライバ、アプリケーションプログラムなどが起動される(ステップ105)。そして、情報処理装置が動作状態になる。

(もっと読む)

リセット信号生成回路及びそれを備えた半導体集積回路

【課題】ノイズや縮退故障等による意図しないリセット信号の解除を防止することが可能なリセット信号生成回路及びそれを備えた半導体集積回路を提供すること。

【解決手段】本発明にかかるリセット信号生成回路は、基準リセット信号RESETZを第1ノードに伝達するための信号線ROUT11と、基準リセット信号RESETZの反転信号を第2ノードに伝達するための信号線ROUTZ12と、第2ノードに伝達された信号の反転信号を出力するINV回路104と、第1ノードに伝達された信号の論理値と、INV回路104の出力信号の論理値と、が一致しない場合、基準リセット信号RESETZに関わらずリセット信号IN_RESZをアクティブにするAND回路105と、を備える。

(もっと読む)

半導体装置

【課題】スタンバイ状態時にSRAMにデータを保持できる電圧が与えられている場合に、パワーオンリセットがかからないようにすることができる半導体装置を提供する。

【解決手段】CPU5は、スタンバイ状態に遷移することを通知する。電源制御回路11は、スタンバイ状態時に、SRAM4における電力消費を低減させる。POR回路2は、外部電源電圧の値と、現在の状態がスタンバイ状態であるかに応じて、パワーオンリセット信号の活性化を制御する。

(もっと読む)

携帯情報端末

【課題】 リセット動作を制限する。

【解決手段】 携帯電話1は、アプリケーションプログラムを実行可能なCPU21と、電源をオンした状態とオフした状態とに切換える指示を受付けるための電源スイッチ14Bと、電源スイッチ14Bが所定時間閉ざされると、CPU21を再起動させるためのリセット信号を出力するリセット検出回路20とを備え、CPU21は、リセット可能な状態とリセット不可能な状態とのいずれかを示す状態信号SL1を出力し、リセット検出回路20は、状態信号SL1がリセット可能な状態を示すこことを条件に、ハイの信号S4(リセット信号)をリセット回路41に出力する論理積素子27を含む。リセット回路41は、リセット検出回路20からハイの信号S4(リセット信号)が入力されると、CPU21にローの信号SL5(リセット信号)を出力する。

(もっと読む)

電子回路

【課題】複数の電源のうち何れかの電源が瞬断したときに、確実に回路全体をリセットすること。

【解決手段】電源V1に瞬断が発生すると、リセット信号RSTN1がローレベルになりメイン回路10は動作が停止する。AND回路22はローレベルの信号SLP_RSTNを出力する。信号SLP_RSTNがローレベルになると、省エネ回路20は動作を停止し、記憶部201の記憶内容もリセットする。電源V1が復帰すると、リセット信号RSTN1はハイレベルになり、メイン回路10は信号BOOTCTLIを出力する。省エネ回路20は記憶部201の記憶内容が初期状態であるため、信号BOOTCTLOをループバックすると共に、記憶部201の記憶内容を起動処理済みであることを示す内容に書き換える。メイン回路10は、この信号BOOTCTLOを受け取ると、省エネ回路20に対して起動処理を実行する。

(もっと読む)

リセット回路および電子機器

【課題】リセット対象部を良好にリセットさせる。

【解決手段】実施形態のリセット回路および電子機器は、入力部と、リセット部と、を備える。前記入力部には、BIOSを実行する実行部を有するリセット対象部に設けられた異常検出部から出力された異常検出信号が入力される。前記リセット部は、前記入力部に前記異常検出信号が入力された場合、前記リセット対象部をリセットさせる。

(もっと読む)

1 - 10 / 409

[ Back to top ]