国際特許分類[G06F11/08]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 故障の発生への応答,例.耐故障性 (1,764) | データの表現形態に冗長性をもたせることによるエラー検出またはエラー訂正,例.チェック・コードを用いることによるもの (355)

国際特許分類[G06F11/08]の下位に属する分類

国際特許分類[G06F11/08]に分類される特許

1 - 10 / 58

データ転送装置、メモリ制御装置、およびメモリシステム

【課題】誤り訂正が発生したとしてもデータ伝送が待たされる時間を少なくし、データ転送に要する時間を短縮することが可能なデータ転送装置、メモリ制御装置、およびメモリシステムを提供する。

【解決手段】データ転送元の第1メモリ装置200の第1メモリアドレスと、データ転送先の第2メモリ装置の第2メモリアドレスと、転送データに誤りが検出されたか否かを示す誤り信号と、誤り訂正が完了して第2メモリ装置106に格納しているデータが有効であるか否かを示す有効信号を記憶する領域を複数含むデータ情報記憶領域109と、第2メモリ装置に格納しているデータのうち、データが有効であるメモリのアドレスである第2メモリ有効アドレスを出力し、第2メモリ装置の第2メモリ有効アドレスからデータを読出し、読出したデータと共に、第2メモリ有効アドレスに対応する第1メモリ装置のアドレスを転送する制御部108とを有する。

(もっと読む)

プログラム実行装置、プログラム生成装置、プログラム正否判定方法、および、プログラム加工方法

【課題】製造コストの削減や小型軽量化を図ると共に、スループットの低下を回避しつつ、オブジェクトプログラムを実行するタイミングでの誤り検出が可能となる。

【解決手段】プログラム実行装置120は、オブジェクトプログラムを実行する命令実行部220と、オブジェクトプログラムを一時的に保持するキャッシュメモリ222と、命令実行部によるオブジェクトプログラムのフェッチ要求を契機に、オブジェクトプログラムを読み込み、キャッシュメモリに保持させるプログラム読込部224と、読み込まれたオブジェクトプログラムに対し、順次、チェックコード導出式を計算し、ブロック単位でチェックコードを生成し、オブジェクトプログラムに予め挿入されているチェックコードと比較してオブジェクトプログラムの正否をブロック単位で判定するチェックコード判定部226とを備える。

(もっと読む)

障害処理方法および計算機

【課題】障害データが読み出しされることによってシステムを停止させるCPUを備える計算機システムにおいて、障害データに対するユーザソフトウェアのアクセス状況に基づいて障害範囲を限定する。

【解決手段】プロセッサと、プロセッサに接続されるメモリとを備える計算機における障害処理方法であって、プロセッサは、メモリ保護機能を備え、第1のソフトウェアと第1のソフトウェアの実行を監視する第2のソフトウェアとを実行し、第2のソフトウェアはアドレス情報とアクセス関連情報とを含む障害情報を保持し、方法は、第2のソフトウェアが、メモリにおける障害の発生を検出するステップと、障害が発生したメモリのアドレスへのアクセスを禁止し、アクセス状況を監視するステップと、障害が発生したメモリのアドレスに対する第1のソフトウェアからのアクセスを検出した場合に障害処理を実行するステップと、を含むことを特徴とする。

(もっと読む)

情報処理装置、情報送信方法および情報受信方法

【課題】通常の情報伝送動作中にバスの故障診断を実行できるようにする。

【解決手段】送信側デバイス10と受信側デバイス20とは、送信データとこの送信データに基づくエラー訂正符号とがパラレル送信されるパラレルバス30を通じて接続されている。送信側デバイス10は、パラレルバス30に送信する信号を反転する信号反転部11を有する。受信側デバイス20は、パラレルバス30からの受信信号を反転する信号反転部21と、信号反転部21から出力された信号を基にエラー検出処理とエラー訂正処理とを実行するエラー検出部22とを有する。信号反転部11によってすべてのバスに送信する信号が反転され、信号反転部21によってすべてのバスから受信した信号が反転されることで、エラー検出部22においてパラレルバス30の故障診断が行われる。

(もっと読む)

演算処理装置、情報処理装置および演算処理装置の制御方法

【課題】演算処理装置において、読み出されたデータのエラーを検出してからエラーを訂正して通常の動作状態に復帰するまでの時間を短縮すること。ハードウェアの量を減らすこと。

【解決手段】チェック部43が記憶部33の出力データのエラーを検出すると、演算制御部31はエラー検出信号EU_PDを出力する。演算制御部31は、記憶部33にエラーが発生したことを示すエラー識別信号GPR_DATA_ERRORを出力する。命令制御部36は、エラー検出信号およびエラー識別信号に基づいてキャンセル信号CANCELおよび訂正開始信号CORRECT_STARTを出力する。演算処理装置12は、キャンセル信号によって演算部32の動作を停止し、エラーの報告処理を開始する。演算処理装置12は、訂正開始信号によってエラー訂正部34でのエラーの訂正処理を開始する。エラーの訂正処理はエラーの報告処理と並行して行われる。

(もっと読む)

エラー訂正装置、エラー訂正装置のメモリの制御方法および光ディスク記録再生装置

【課題】エラー訂正時に使用されるメモリ容量の増大を低減させる。

【解決手段】エラー訂正装置(35)は、メモリ(351)と、エラー訂正部(357)とを有する。メモリは、格納済みの第1ブロックデータが有する複数のフレームデータを行方向に順次読み出し、読み出しに連動して読み出し後の空き領域に第2ブロックデータが有する複数のフレームデータを行方向に順次格納する第1動作と、第1動作で格納した第2ブロックデータが有する複数のフレームデータを列方向に順次読み出し、読み出しに連動して読み出し後の空き領域に第1ブロックデータが有する複数のフレームデータを前記列方向に順次格納する第2動作とを交互に行う。

(もっと読む)

ストレージデバイス内のエラーデータを追跡するシステムおよび方法

エラーデータを追跡するシステムおよび方法を開示する。この方法が、第1のエラー訂正コード演算のエラー場所に関連づけられた第1のチェックサムを受信するステップと、第2のエラー訂正コード演算のエラー場所に関連づけられた第2のチェックサムを受信するステップとを含む。第1のチェックサムは、第2のチェックサムと比較され、その比較結果に基づいてメモリアレイの領域に動作が開始される。  (もっと読む)

(もっと読む)

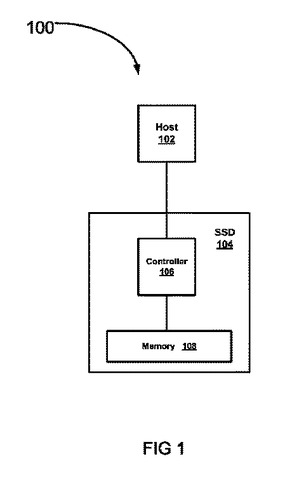

ソリッドステートディスクにおける改良された誤り訂正

いくつかの実施例では、ソリッドステートディスクは、不揮発性メモリとコントローラとを有する。コントローラは、不揮発性メモリに格納されているデータに対してECCを実行し、ECCがデータを訂正できない場合、データに対してパリティ処理を実行する。他の実施例が開示及び請求される。  (もっと読む)

(もっと読む)

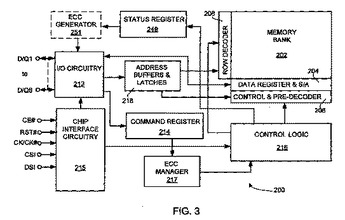

エラー検出方法および1つまたは複数のメモリデバイスを含むシステム

1つまたは複数のメモリデバイスを含むシステムと、エラーの検出および訂正の方法とが開示される。システムのメモリデバイスが、パケットを受信するための入力を含む。パケットの第1の部分は、少なくとも1つのコマンドバイトを含むことが可能であり、パケットの第2の部分は、コマンドエラー検出を容易にするパリティビットを含むことが可能である。メモリデバイスは、パリティビットに基づいて、エラーが少なくとも1つのコマンドバイト内に存在するかどうかを検出するように構成されているエラーマネージャと、パケットをエラーマネージャに供給するように構成されている回路とを含むことが可能である。  (もっと読む)

(もっと読む)

フォルト検出回路

【課題】フォルト検出回路において、回路規模を低減し、故障や誤動作がどの部分で起こっているのかを明らかにできるようにする。

【解決手段】論理回路20を自己双対関数によって設計し、外部から同じ内容のデータを2回入力する。論理回路20では、転送1回目のデータが反転されずに演算され、この結果が第4フリップフロップ32に保持され、転送2回目のデータが反転されて演算され、この結果が第3フリップフロップ31に保持される。これにより、出力側エラー検出回路34によって、第4フリップフロップ32に保持されたデータと、第3フリップフロップ31に保持されたデータとが比較され、各データが異なるときにはエラーが出力される。

(もっと読む)

1 - 10 / 58

[ Back to top ]