国際特許分類[G06F11/28]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | エラー検出;エラー訂正;監視 (10,741) | 処理順序の正しさを検査することによるもの (1,742)

国際特許分類[G06F11/28]に分類される特許

1 - 10 / 1,742

テストシステム、テスト方法、及び、プログラム

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

マルチプロセッサ装置及びマルチプロセッサ装置の制御方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

トレース情報の数を算出する計算機、トレース情報の数を算出する方法及びトレース情報の数を算出させるプログラム

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

ソースコード変換方法及びソースコード変換プログラム

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

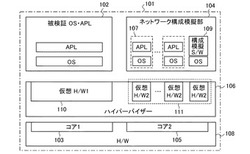

ネットワーク機能検証システム

【課題】複数のH/W構築を必要とせずに、高いCPUパワーを有しないコンピュータ上で、ネットワーク構成を模擬し、同期動作するシステムのネットワーク機能を検証するネットワーク機能検証システムを得る。

【解決手段】デュアルコアCPUを搭載したコンピュータ101のH/W108上でハイパーバイザー106が動作し、ハイパーバイザー106上で仮想H/W1(110)と複数の仮想H/W2(111)が形成され、仮想H/W1(110)上には被検証OS・APL102が動作し、各仮想H/W2(111)上には、模擬される各ノードであるOS・APL107が動作してネットワーク構成を模擬し、被検証OS・APL102が、OS・APL107と通信を行って、ネットワーク機能を検証するようにした。

(もっと読む)

インサーキットエミュレータ、トレースメモリ制御装置、トレースメッセージ生成装置及びトレースメッセージ処理方法

【課題】トレース対象の命令の実行が同時に生じた場合に、正確な命令発生タイミングを把握すること

【解決手段】タイミング情報生成回路131は、第1CPUコア111、第2CPUコア121の各々からのトレースデータの出力と同期して出力されるプロセッサ1(2)出力イネーブル信号に基づき、トレースデータの出力タイミングが同一であるか否かを示すタイミング情報を出力する。トレースメッセージ生成回路132は、各トレースデータと、各トレースデータ取得時のタイムスタンプと、タイミング情報と、を対応付けたトレースメッセージを生成する。トレースメモリ書き込み制御回路144は、トレースメッセージ生成回路132が生成したトレースメッセージをトレースメモリ150に書き込む。

(もっと読む)

シミュレーション装置、シミュレーション方法、およびシミュレーションプログラム

【課題】ハードウェアとソフトウェアの協調動作のデバッグを効率的に行うこと。

【解決手段】シミュレーション装置100は、ソフトウェア101の実行中に、ハードウェアモデル102にアクセスする特定の関数が実行される場合、論理シミュレータ103側となるC−SVインターフェース104にて特定の関数の関数名を取得する。次に、C−SVインターフェース104は、関数名を記憶領域に格納する。また、論理シミュレータ103も、ハードウェアモデル102のシミュレーションの結果を記憶領域に格納する。波形ビューワ111は、記憶領域に格納されたシミュレーションの結果と関数名とを、時系列で対応付けて表示する。

(もっと読む)

品質判定プログラム、品質データ収集判定プログラム、及び、情報処理装置

【課題】プログラムの品質を判断すること。

【解決手段】品質判定の対象プログラムがインストールされている1以上の第1のコンピュータで対象プログラムの実行を監視することにより収集された品質データであって対象プログラムの品質を判定するための品質データが記憶されている記憶装置から品質データを取得する取得処理(S201)と、取得処理によって取得された品質データに基づいて対象プログラムの品質を判定する品質判定処理(S202)と、を情報処理装置に実行させる品質判定プログラム。

(もっと読む)

試験装置及び試験方法

【課題】移動端末の有するデバイスに拘わらず、該移動端末に搭載されたソフトウェアによる機能を試験すること。

【解決手段】移動端末に搭載されたソフトウェアによる動作を評価する試験装置は、移動端末に動作させる機能を実行させるための操作情報を含むシナリオを設定するシナリオ設定部と、該シナリオに含まれる操作情報により表される操作が、該移動端末に実装されたデバイスによって影響を受けるか否かを判定する操作判定部と、移動端末に実装されたデバイスによって影響を受けると判定された操作を移動端末に実装されたデバイスに応じて変換する操作対象変換部と、変換された操作に従って、設定されたシナリオを実行するシナリオ実行部と、実行されたシナリオの実行結果が予め想定された結果と同じかどうかを判定するシナリオ実行結果判定部とを有する。

(もっと読む)

割り込み回路及び割り込み方法

【課題】マイクロコンピュータのチップに内蔵した割り込み回路における割り込み処理の遷移を、インサーキットエミュレータを使用せずに時間計測する。

【解決手段】割り込み監視回路11が、割り込み要求、CPU(中央演算処理装置)からの割り込み許可信号、割り込み処理の本体の開始信号、割り込み処理の本体の終了信号、割り込み前のプログラムへの復帰信号の少なくとも1つをトリガとしてタイマ回路12にトリガ信号S1を供給することにより、タイマのカウント値をキャプチャレジスタに取り込んだ直後に、取り込んだタイマのカウント値と割り込み種類情報を、内部バス33に接続された内部メモリ32に転送する。割り込み処理の実行後に、各々の割り込み種類ごとに、割り込み待ち時間、割り込み前処理の時間、割り込み処理本体の時間、割り込み後処理の時間、割り込み処理全体の時間の少なくとも1つを計算する。

(もっと読む)

1 - 10 / 1,742

[ Back to top ]