国際特許分類[G06F12/00]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382)

国際特許分類[G06F12/00]の下位に属する分類

アドレシングまたはアロケーション;リロケーション (4,708)

メモリの不正な使用に対する保護 (533)

メモリ内容の破壊に対する保護 (2,432)

国際特許分類[G06F12/00]に分類される特許

61 - 70 / 12,709

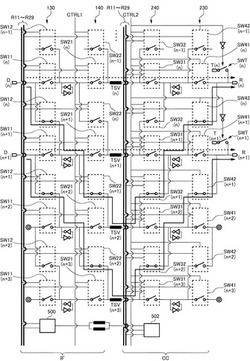

半導体装置

【課題】複数の貫通電極を選択的に利用可能な積層型の半導体装置において、回路動作を安定させる。

【解決手段】半導体記憶装置10は、インターフェースチップIFと複数のコアチップCCを含む。コアチップCCは、インターフェースチップIFに積層される。インターフェースチップIFとコアチップCCは複数の貫通電極TSVにより接続される。コアチップCCに含まれる入力切り替え回路240、230は、電源投入時における設定処理の前に、コアチップCCに含まれる複数の入力信号線と複数の貫通電極TSVとの接続をいったん遮断し、コアチップCCの設定後に、複数の入力信号線と複数の貫通電極TSVの接続を示す救済情報にしたがって各入力信号線を複数の貫通電極TSVのいずれかと接続する。

(もっと読む)

画像形成装置及び画像形成装置制御方法

【課題】データのバックアップを効率的に実行しつつ退避前の状況を復元可能な画像形成装置及び画像形成装置制御方法を実現する。

【解決手段】画像形成装置の記憶部に記憶されているプリントデータ及びイメージデータについて、対応する関係にあるか否かを調べ、対応する関係にある前記プリントデータ及び前記イメージデータが存在している場合には前記プリントデータを、対応する関係にない前記プリントデータ又は前記イメージデータについては当該前記プリントデータ又は前記イメージデータを、バックアップの対象として退避用記憶部に退避させてバックアップを実行する。

(もっと読む)

グラフインデックス更新装置

【課題】グラフインデックスの更新において、過剰に長いリンクの生成を抑制することが可能な装置又は方法を提供する。

【解決手段】データベースに格納された複数のベクトルデータの一部又は全部によって構成される特定のベクトルデータ集合を特定する。ついで、前記ベクトルデータ集合に属する第1のベクトルデータから、第2のベクトルデータを、前記複数のベクトルデータ間のリンク関係を示すグラフインデックスを用いて検索する。ついで、前記グラフインデックスを用いた検索の過程において取得した第3のベクトルデータと前記第2のベクトルデータとの間の距離が、前記第1のベクトルデータから前記第2のベクトルデータまでの距離より短い場合には、前記第3のベクトルデータと前記第2のベクトルデータとの間に新たなリンクを生成して、前記グラフインデックスを更新する。

(もっと読む)

データベース圧縮装置

【課題】ページ単位で圧縮あるいは伸張可能なデータベース圧縮装置を提供する。

【解決手段】データベース管理システムと、ユーザテーブルを管理する論理ページを記録するための論理ページ用メモリと、可変長の圧縮ページを表形式で管理するページ管理テーブル内の圧縮ページを記録するための物理ページ用メモリと、データベース管理システムに配置され、論理ページ用メモリに記録される未圧縮ページを圧縮する圧縮ライブラリと、データベースファイルを記録・格納するストレージと、を備え、データベース管理システムは、ページ単位でデータを圧縮/伸張する。

(もっと読む)

複数のファイルを列挙した情報を生成する装置及び方法

【課題】アプリケーション側にハードウェアデバイスに依存した実装を施すことなく、シーケンシャルメディアに特化したパフォーマンスを落とさないアクセスを行う。

【解決手段】ファイルシステム60では、コマンド処理部61が、ファイルの列挙方法を示すオプションをコマンドから取り出し、インデックス受信部63が、ディレクトリ名、ファイル名、記録位置を含むインデックスをテープドライブから受信し、インデックス記憶部66が、オプションが示す列挙方法に従い、インデックスを、そのままの状態で、又は、ディレクトリ名もしくはファイル名が変更された状態で、記憶する。一方、IRP受信部67が、IRP(I/O Request Packet)をOSから受信すると、IRP設定部68が、インデックス内のファイル名を記録位置の順にIRPのバッファに格納し、応答送信部69が、ステータスをOSに返す。

(もっと読む)

サンプリング装置、サンプリングプログラム、およびその方法

【課題】探索のために最適化されていないデータソースに対して、全体の傾向を適切に取得することができるサンプリング装置を提供することを目的とする。

【解決手段】記憶装置に記録された複数のレコードの中から、ランダムにレコードをサンプリングするサンプリング装置であって、記録位置に対応する乱数を生成する乱数生成手段と、前記複数のレコードから、前記生成した乱数に対応する記録位置にデータを有するレコードを選択するレコード選択手段と、前記選択されたレコードのレコード長を取得するレコード長取得手段と、前記取得されたレコード長に基づいて算出した確率で、前記選択されたレコードをサンプルとして採用するサンプル決定手段と、を有することを特徴とする。

(もっと読む)

電子機器及び固有情報の管理方法。

【課題】マイクロコントローラのフラッシュメモリに記憶されたプログラムにより電子機器本体を制御する電子機器において、製造コストの低下を図りかつ固有情報の書き換えを速やかに行う。

【解決手段】フラッシュメモリ5内の固有情報領域7に外部コンピュータ4から固有情報群を事前に書き込んでおく。固有情報群は例えばシンセサイザ回路部2に使用される標準のパラメータ群及び周波数シンセサイザ1の仮番号である。マイクロコントローラ3のRAM8には、固有情報領域7と同容量の読み出し領域81が割り当てられ、電源投入時に固有情報領域7から読み出し領域81に固有情報群が読み出される。外部コンピュータ4からの指示により当該固有情報群の一部を書き換え、その後固有情報領域7内の固有情報群を一括消去した後、読み出し領域81内の固有情報群を一括して固有情報領域7に書き込む。

(もっと読む)

情報処理装置およびその制御方法、並びにプログラム

【課題】WEBアプリケーションが中間言語やスクリプト言語で記述されている場合、WEBアプリケーション内の各ページへのアクセス時に初めて中間言語などをコンパイルし、結果をキャッシュに保持する処理が実行されるため、初回アクセスに関しては応答に時間がかかるという問題がある。

【解決手段】ネットワークを介して接続される端末からの要求に応じてアプリケーションプログラムのウェブページを提供する情報処理装置であって、前記端末によりウェブページが要求される前に、前記アプリケーションプログラムに対して前記ウェブページの要求を発行する要求手段と、前記要求手段による前記ウェブページの要求に応じて、前記アプリケーションプログラムが提供する前記ウェブページをコンパイルし、キャッシュに保持して管理する管理手段とを有する。

(もっと読む)

デジタル信号処理用のメモリアクセス

【課題】デジタル信号処理システムにおけるメモリアクセスを提供する。

【解決手段】一例では、デジタル信号処理システムは、複数の単一ポートのメモリデバイスに接続されたメモリインタフェースから構成されたマルチポートのメモリを有する。メモリインタフェースは、プロセッサが単一アドレス空間を使用して単一ポートのメモリデバイスに格納されたデータにアクセスするために使用できるアクセスポートを提供する。プロセッサは、複数のアクセスポートに接続され、同時に複数の異なるメモリアドレスのデータへのアクセスを要求するためにこれらを使用してもよい。デジタル信号処理システムは、メモリインタフェースに接続された単一ポートのメモリデバイスの総数が3以上の素数になるように構成される。素数の数のメモリデバイスが使用されるため、異なるメモリアドレスのデータが同じ単一ポートのメモリデバイスにある可能性が最小化され、メモリアクセス速度を増加させる。

(もっと読む)

外部記憶装置およびそのメモリアクセス制御方法

【課題】セクタデータを連続してアクセスする外部記憶装置において、単一のエラー訂正手段によりエラー検出・訂正を行いながらメモリアクセスを高速化する。

【解決手段】ホスト2がライトするセクタデータは一時ライトバッファ7に格納される。マイクロプロセッサ8は、ライトバッファに格納されたセクタデータが奇数番目のセクタデータの場合には第1のメモリ4に、偶数番目のセクタデータの場合には第2のメモリ5に格納する。ホスト2がセクタデータをリードするときには、データ切換手段11において、第1のメモリから読み出したN番目のセクタデータをシステムバスに対し出力すると同時に、第2のメモリから読み出したN+1番目のセクタデータ(ホストコンピュータが次にリードするセクタデータ)をエラー訂正手段に対し出力する。これにより、N+1番目のセクタデータに対するエラー検出およびエラー訂正に要する時間を見かけ上短縮する。

(もっと読む)

61 - 70 / 12,709

[ Back to top ]