国際特許分類[G06F12/08]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | アドレシングまたはアロケーション;リロケーション (4,708) | 階層構造のメモリ・システム,例.仮想メモリ・システム,におけるもの (2,277)

国際特許分類[G06F12/08]の下位に属する分類

国際特許分類[G06F12/08]に分類される特許

1 - 10 / 1,680

半導体記憶装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

ソフトエラー耐性調整機能を備えた電子システム装置及びソフトエラー耐性調整方法

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

複数の状態のプロセッサのための命令のキャッシング

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

ホスト装置、システム、及び装置

Notice: Undefined index: from_cache in /mnt/www/gzt_ipc_list.php on line 285

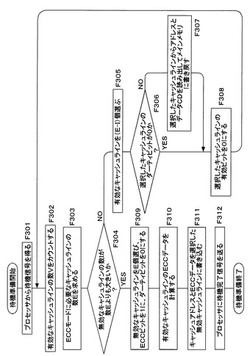

不揮発性キャッシュメモリ、不揮発性キャッシュメモリの処理方法、コンピュータシステム

【課題】不揮発性メモリをキャッシュメモリとして使用する場合に、電力遮断状態での保持されているデータの信頼性を向上させる。

【解決手段】キャッシュデータの記憶に不揮発性メモリを用いる。この場合に、電力供給遮断の準備として、待機状態データを生成して不揮発性メモリ部上に記憶する待機準備処理を行う。また電力供給再開の際に、待機状態データを用いて不揮発性メモリ部に記憶されたキャッシュデータの復帰処理を行う。

(もっと読む)

プログラムの命令を実行する装置および命令をキャッシュするシステム

【課題】キャッシュ・メモリに命令をキャッシュする場合における保持内容の冗長さを減少させ、効率の良いキャッシュ・システムを実現する。

【解決手段】命令フェッチ・ユニット10と、命令キャッシュ20と、命令とこの命令が格納されたメイン・メモリ上における1または複数のアドレスとを関連付けて保持するマクロ・キャッシュ部30と、命令キャッシュ20におけるキャッシュ・ヒットの頻度が高い命令をマクロ・キャッシュ部30に保持させるマクロ登録判断部40と、を備える。マクロ・キャッシュ部30は、マクロ登録判断部40により保持するように指示された命令と同一の命令を既に保持している場合は、その命令を指定するアドレスを、既に保持しているその命令と関連付けて保持し、マクロ登録判断部40により保持するように指示された命令と同一の命令を保持していない場合は、その命令とその命令を指定するアドレスとを関連付けて保持する。

(もっと読む)

階層間の効率的なデータ移行を管理する装置

【課題】低速階層及び高速階層を有するデータストレージシステムにおいて、階層間でデータを効率的に移行させる。

【解決手段】高速データストレージデバイス106のリザーブスペースを備えている。プロセッサ102は、メモリ104に記憶されたリザーブスペーステーブルを参照して、低速データストレージデバイス108に記憶されたデータへのアクセスが高頻度となることによりホットデータとなると、該データを高速データストレージデバイス106のリザーブスペースに移し、該ホットデータを高速データストレージデバイス106上に保持する。データ移行は、一方向性であることが多く、データは低速階層から高速階層へ移行し、通常動作中のオーバーヘッドを低減することができる。

(もっと読む)

プログラム変換装置、プログラム変換方法、および変換プログラム

【課題】プロセッサコアが夫々キャッシュメモリを有するマルチプロセッサ環境で前記キャッシュメモリを効率よく使用できるようにプログラムを変換すること。

【解決手段】プログラム変換装置は、アクセス属性決定部と、非共有化対象分類部と、変換部とを備える。アクセス属性決定部は、ソースプログラムを構成するスレッドによるメモリアクセスから排他アクセスを求め、前記求めた排他アクセスのうちからキャッシュメモリを使用するメモリアクセスを決定する。非共有化対象分類部は、前記キャッシュメモリを使用してメモリアクセスされるアクセスデータのうちから、他のアクセスデータとの間でキャッシュラインを非共有化させるアクセスデータを決定する。変換部は、前記非共有化対象分類部による決定結果に基づいてキャッシュラインを非共有化させる処理をソースプログラムに挿入する。

(もっと読む)

記憶装置および計算機

【課題】不揮発性メモリからキャッシュメモリへの書込回数を削減する。

【解決手段】記憶装置10は、不揮発性メモリ30とキャッシュメモリ20とメモリコントローラ12とを有する。不揮発性メモリ30は、分割データと格納場所を管理する論理/物理アドレス変換テーブル32を記録している。キャッシュメモリ20は、データキャッシュ21と、論理/物理アドレス変換テーブル32の一部を保持する論理/物理アドレス変換テーブルキャッシュ22を記録している。メモリコントローラ12は、外部からデータの読み出し要求を受けたとき、データキャッシュ21上に空きエントリが無かったならば、データキャッシュ21上の分割データのうち、論理/物理アドレス変換テーブル32のエントリが、論理/物理アドレス変換テーブルキャッシュ22に有るものを優先的に不揮発性メモリ30に退避して空きエントリを作成し、データを読み出す。

(もっと読む)

キャッシュ装置、メモリシステム及びデータ転送方法

【課題】キャッシュデータを効率的にメインメモリへライトバックすることができるキャッシュ装置、メモリシステム及びデータ転送方法を提供すること

【解決手段】本発明にかかるキャッシュ装置は、複数のキャッシュデータが、メインメモリ80に格納されている複数のデータと一致しているか否かを判定するライトバック制御部60と、複数のキャッシュデータのうち、不一致と判定されたキャッシュデータであって、メインメモリ80において連続するアドレスへ書き込まれる複数のキャッシュデータを格納するデータバッファ部13と、データバッファ部13へ格納されたキャッシュデータを一括してメインメモリ80へ書き込むメモリライト部14と、を備えるものである。

(もっと読む)

1 - 10 / 1,680

[ Back to top ]