国際特許分類[G06F12/14]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | メモリ・システムまたはアーキテクチャ内でのアクセシング,アドレシングまたはアロケーティング (20,382) | メモリの不正な使用に対する保護 (533)

国際特許分類[G06F12/14]に分類される特許

31 - 40 / 533

記憶装置及び履歴情報書き込み方法

【課題】出荷された後の履歴情報の秘匿性を保ちつつ履歴情報の管理を容易に行うこと。

【解決手段】ユーザがデータを書き込む記憶領域を有する記憶装置は、履歴情報を記憶領域の一部に書き込むデータ書き込み手段と、記憶領域の一部へのユーザアクセスを不可にするアクセス不可手段と、ユーザアクセス不可とした一部の領域をアクセス可能にする開放手段と、を有する。

(もっと読む)

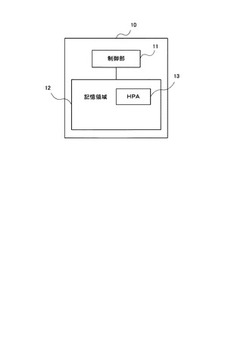

メモリシステム

【課題】 ユーザによるアプリケーションソフトウェアやシステムソフトウェアのアクセスを禁止することが可能なメモリシステムを提供する。

【解決手段】 メモリシステムは、アプリケーションモジュール19aと、記憶部18と、制御部11aとを含んでいる。記憶部18は、ユーザデータ、アプリケーションモジュールの動作を制御するアプリケーションソフトウェア、これらデータ及びソフトウェアを管理する管理情報を記憶している。制御部11aは、記憶部18から読み出された管理情報からアプリケーションソフトウェアを含むアクセス禁止領域を示す情報をマスクする。

(もっと読む)

誤書き込み防止回路および半導体装置

【課題】 書き込み時間の増加を抑制しつつ、保護対象のモジュールに対する誤書き込みを防止する。

【解決手段】 誤書き込み防止回路は、バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、バスに接続された保護対象のモジュールに書き込まれるデータに対応する期待値と比較コードとを比較する比較部と、比較部の比較結果に基づいて、モジュールに対する書き込みを許可するか否かを決定する書き込み制御部とを有している。

(もっと読む)

携帯装置及び動的データの格納位置変更方法

【課題】機密データの解読の足掛かりとなる誤動作が生じるメモリセルを特定することが困難になるセキュリティデバイスを提供する。

【解決手段】本実施形態のICカード1は、コンピュータプログラムが動作してから生成する動的データを利用するプログラムコードのオペランドに、起動した際に乱数を用いて生成される所定範囲内のオフセット値を基準とする相対位置が記述され、動的データを格納する物理アドレスとして、動的データを格納するためにメモリに設定された作業領域の先頭アドレスに、オフセット値及記相対位置を加算した値を利用するように構成されている。

(もっと読む)

セキュア計算システム、セキュア計算方法およびセキュア計算用プログラム

【課題】マルチコアプロセッサを用いて計算処理を実行する際、プロセッサごとの動作を制御する特別なセキュリティ回路を備えていない場合であっても、セキュアに計算処理を実行できるセキュア計算システムを提供する。

【解決手段】一のコア80は、他のコア90からのアクセスが可能な状態で情報を記憶する他コアアクセス可能記憶手段81と、自コアからのみアクセスが可能な状態で情報を記憶する自コア内アクセス可能記憶手段82とを備える。復号手段83は、他のコアから受信した暗号化データを復号鍵を用いて復号した平文データを作成し、その平文データを平文データ記憶手段87に記憶させる。平文データ計算手段84は、平文データ記憶手段87に記憶された平文データに対して指定された計算処理を行い、その計算処理による計算結果を結果データ記憶手段86に記憶させる。

(もっと読む)

中継装置及び中継プログラム

【課題】検索サーバに、バースト的な検索の発生が知られる可能性を低減する。

【解決手段】端末10から入力される検索キーワード群を受け付ける受付部20と、受付部が受け付けた検索キーワード群を検索サーバ16に送信する検索キーワード送信部22と、過去に用いた検索キーワードの一致度が低い従業員ごとにまとめた従業員のグループが登録されたクラスタDB40を参照し、グループ内において特定の検索キーワードを所定時間内に利用した従業員の割合(均質性)が、所定の第1の閾値よりも高い場合に、特定の検索キーワードを含む検索キーワード群を検索サーバ16に送信しないように検索キーワード送信部22を制御する検索キーワード隠蔽制御部26と、を備えている。

(もっと読む)

メモリ保護ユニットおよび記憶素子へのアクセスコントロール方法

【課題】メモリ保護に於いて、効果的かつフレキシブルな保護ユニットを提供する。

【解決手段】処理素子による記憶素子17へのアクセスは、当該処理素子に関連するメモリ保護ユニット15,16の第1のアクセスコントロールユニット31と第2のアクセスコントロールユニット32がアクセスを許可した場合に許可され、第1のアクセスコントロールユニット31または第2のアクセスコントロールユニット32がアクセスを拒否した場合には拒否される。第1のアクセスコントロールユニット31は関連の処理素子によってのみプログラム可能であり、第2のアクセスコントロールユニット32のプログラミングは、複数の処理素子を有するシステム使用されるが、前記関連の処理素子ではない付加的な処理素子によって読み出し可能である。

(もっと読む)

プロセッサ、バスインターフェース装置、およびコンピュータシステム

【課題】外部バスからプロセッサ内部のレジスタやローカルメモリの読み出しや改変が可能であった。そのため、暗号鍵などの機密データが読み出されたり、開発したソフトウェアがコピーされてしまう可能性があった。

【解決手段】外部と接続するバスを持つメディアプロセッサにおいて、外部バスに接続された他のデバイスからのアクセスは全て許可される。そのため、プロセッサ内部の機密事項を保護するために、メディアプロセッサのバスインターフェース部分にTLBを設け、そのTLBはプロセッサ内部からのみ書き換えることができる。このTLBは外部からアクセスされたアドレスが、アクセスできるかを判定する。TLB内にアクセス許可が記述されていればメディアプロセッサ内部へアクセスを発生し、そうでなければリクエストを破棄する。

(もっと読む)

動的バイナリ・トランスレータに関するメモリ管理のための装置、方法、およびコンピュータ・プログラム

【課題】あるページ・サイズの第1のブロックを、他のページ・サイズの第2のブロックへと変換するための動的バイナリ・トランスレータ装置を提供する。

【解決手段】装置は、第1のメモリ506のメモリ・ページ特性に応じて、第1のメモリのアドレスを第2のメモリ512のアドレスにマッピングするためのリダイレクト・ページ・マッパ514と、第2のブロックの実行中にメモリ障害を検出し、障害カウントをトリガしきい値まで累算することを実行するように動作可能なメモリ障害挙動検出器516と、障害カウントがトリガしきい値に達したことに応じて、第2のブロックを廃棄し、ページ・テーブル・ウォークにより再マッピングされたメモリ参照を用いて第1のブロックを再変換済みブロックへと再変換することを実行するように動作可能な再生成コンポーネント518と、を備える。

(もっと読む)

マルチプロセッサシステム、マルチプロセッサシステムにおけるシステム構成方法及びそのプログラム

【課題】安定性やセキュリティレベルを考慮して実行する処理内容に応じて実行環境を柔軟に構築する。

【解決手段】マルチプロセッサシステムは、CPU割当ての決定に際し、CPU割当てを判断する実行環境主制御手段10と、実行環境主制御手段10の指示に従って、実行環境の起動・停止・切替を制御し、実行環境主制御手段10との同期をとる実行環境副制御手段20a〜20nと、CPU4−0〜CPU4−n又は実行環境毎の共有資源の管理情報や参照拒否情報を入力し、実行環境主制御手段10と実行環境副制御手段20a〜20n又は、実行環境副制御手段20a〜20nをそれぞれ分離する実行環境管理手段30とを含む。

(もっと読む)

31 - 40 / 533

[ Back to top ]