国際特許分類[G06F17/50]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 特定の機能に特に適合したデジタル計算またはデータ処理の装置または方法 (34,028) | 計算機利用設計 (7,589)

国際特許分類[G06F17/50]に分類される特許

81 - 90 / 7,589

リッツ線の電気特性解析方法および電気特性解析プログラムならびに電気特性解析装置

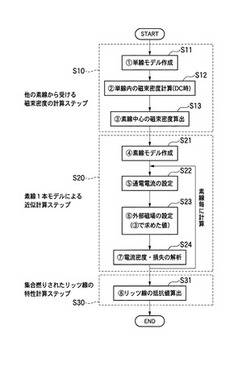

【課題】集合撚りされたリッツ線について計算機のメモリ容量の制約を受けずに特性を計算可能なリッツ線の電気特性解析方法を提供する。

【解決手段】リッツ線のある位置の断面構造の複数の素線の1つに相当する素線モデルを作成する素線モデル作成ステップS21と、リッツ線全体の単線モデルについて前記断面の磁束密度分布を算出する磁束密度算出ステップS10と、複数の素線のそれぞれについて該当する素線1本の通電電流と前記磁束密度算出ステップで得られる素線位置の磁束密度と前記素線モデルとに基づき所望の周波数における電流密度および電気的損失量を算出する素線特性算出ステップS24と、各素線の電気的損失量に基づいて前記リッツ線の全体の電気的特性を算出するステップS30とを有する。複数の素線モデルを生成する必要がなくメモリ容量が少なくても計算可能になる。

(もっと読む)

CADメッシュにおける接平面連続境界の抽出システム及び抽出方法

【課題】CADメッシュにおけるセグメンテーションのためのG1連続境界を精度良く抽出する。

【解決手段】3次元CADモデルを三角形分割することにより生成された三角形メッシュであるCADメッシュのデータからPアークとPラインとを抽出する。Pアークが平滑Pアークかどうか、及び、Pラインが平滑Pラインかどうかを判定する。抽出された平滑Pアークを判定することにより、円弧G1連続境界を抽出できる。また、抽出された平滑Pラインを判定することにより、直線G1連続境界を抽出できる。

(もっと読む)

部品の共通化による樹脂製品の製造

【課題】予め定められた要目の部品を組み合わせることによって樹脂製品の外殻或いは製品そのものを構成することで、新製品の開発及び製造に必要な型の新規製造という段階を省略し、新製品の開発を容易にするとともに、開発及び製造に必要な費用を低減し、販売価格の下落を図る。

【解決手段】まず平板状や棒状といった、多種多様な樹脂製品及び部品の一部として流用可能な部品を成型するための型を製造しておく。そして新製品を開発するに当たっては、既存の共通部品を組み合わせることで要求仕様を満たす製品を設計し、それに従って部品を成型して組み立て、製品を製造する。

(もっと読む)

半導体装置の設計方法、半導体装置の設計プログラム、半導体装置の設計装置

【課題】IRドロップの制約を満たしつつチップレイアウトを小型化できる半導体装置の設計方法、半導体装置の設計プログラム、半導体装置の設計装置を提供すること。

【解決手段】本発明の一態様である半導体装置の設計方法は、複数の電源用パッド及び信号用パッドを、半導体チップ上のチップコアの周囲に配置する。そして、複数の電源用パッド及び信号用パッドの数から決まるチップサイズSpと、チップコアの大きさから決まるチップサイズScと、を比較する。その後、Sp≧Scであれば、IRドロップが制約値を満たす限り、配置した複数の電源用パッドのうちの1又は2以上の電源用パッドを削除する。

(もっと読む)

タイヤのシミュレーション方法

【課題】計算時間等を短縮しうるタイヤのシミュレーション方法に関する。

【解決手段】空気入りタイヤを有限個の要素でモデル化したタイヤモデルを設定するステップS1と、前記タイヤモデルと接触する接触面を有するリムをモデル化したリムモデルを設定するステップS2と、前記タイヤモデルを前記リムモデルに装着する条件を与えてタイヤ・リム組立体モデルを設定するステップS3とを含むタイヤのシミュレーション方法であって、前記リムモデルの前記接触面は、関数によって定義されることを特徴とする。

(もっと読む)

フィラー配合材料のシミュレーションモデル生成方法。

【課題】フィラー配合材料のシミュレーションモデルをコンピュータを用いて簡単かつ短時間で生成する。

【解決手段】マトリックス中にフィラーが分散配合されたフィラー配合材料のシミュレーションモデルをコンピュータを用いて生成するための方法であって、シミュレーションモデルの形成空間を、前記フィラーの領域とフィラー以外の領域とに区分し、これらの境界を定めるステップS1、前記フィラーの領域を有限個の要素に分割してフィラーモデルを設定するステップS2、前記フィラー以外の領域を有限個の要素に分割するステップS3、前記フィラー以外の領域の要素のうち、少なくとも前記フィラーモデルに接触している要素を界面モデルとして設定するステップS4、及び前記フィラー以外の領域の要素のうち、前記界面モデルの外側の要素をマトリックスモデルとして設定するステップS5を含むことを特徴とする。

(もっと読む)

半導体装置および半導体装置の制御方法並びに半導体装置の設計支援方法

【課題】本発明の課題は、組み込みシステムのアーキテクチャに左右されることなく、DVFSの実行に必要なサイクル数を容易に取得することである。

【解決手段】ファームウェア(21)は、サイクル数概算ルーチン(213)と、動作電圧・周波数算出ルーチン(213)とを有する。サイクル数概算ルーチンは、サイクル数概算関数を備える。サイクル数概算関数は、ユーザ回路(6)の処理内容を決定づける属性パラメータの入力でタスクのサイクル数を概算する。動作電圧・周波数算出ルーチンは、サイクル数概算ルーチンの実行によって得られたサイクル数に基づいて、ユーザ回路(6)の目標動作電圧・周波数を算出する。

(もっと読む)

情報生成プログラム、情報生成方法、および情報生成装置

【課題】モデルの分解方向検出の高精度化を図ること。

【解決手段】+X〜−Zの6方向の各方向について、各方向からのEリング101の投影画像(a)〜(f)を生成する。投影画像(a)〜(f)は、所定サイズのビットマップに対し、所定倍率で投影される。他の部品を表示させてその色を背景色と同色の黒にして、各方向からのEリング101の投影画像(A)〜(F)を生成する。投影画像(A)〜(F)も、投影画像(a)〜(f)と同一サイズのビットマップに対し、同一倍率で投影される。両投影画像(a)〜(f),(A)〜(F)について、同一方向からの投影画像どうしで比較する。そして、一致する白のビット数が最大である組を検出し、その投影画像の組を投影した方向を、組付方向に決定する。図1の場合は、+X方向が組付方向となり、その逆の−X方向が分解方向となる。

(もっと読む)

レイアウトデータ作成装置及び半導体装置

【課題】従来のようにピラーの分割単位が小数点数とならず、単位ピラートランジスタのピラーの径の変更を行う必要が無くなり、半導体装置を製造するプロセスを複雑化することなく、ピラー型のトランジスタによりセルを、セルロウ内に効率的に配置するレイアウトデータ作成装置を提供する。

【解決手段】本発明のレイアウトデータ作成装置は、集積回路における複数の単位ピラー型トランジスタで構成されるピラー型トランジスタを、配置領域内に配置可能な単位ピラー型トランジスタの整数単位に分割し、配置領域内に配置するサブピラー型トランジスタを生成するトランジスタ調整部2を備えている。

(もっと読む)

メッシュ作成装置、メッシュ作成方法、メッシュ作成プログラム

【課題】メッシュの作成において、不良メッシュの数を低減するメッシュ作成方法等を提供する。

【解決手段】メッシュ作成の対象領域に、所定寸法の第1メッシュを含む第1メッシュ領域を設定する第1メッシュ領域設定部と、前記第1メッシュ領域の外周上のメッシュの節点数と同数の節点候補を前記対象領域の外周上に所定の配置仕様で設定する外周設定部と、前記第1メッシュ領域の外周上のメッシュの節点と前記節点候補とを対応づけた線分を設定し、前記第1メッシュ領域の外周から前記対象領域の外周に至る部分に第2メッシュを設定する第2メッシュ領域設定部と、前記第1メッシュと前記第2メッシュとを含む前記メッシュ作成の対象領域中のメッシュ節点にラプラシアン法による節点位置調整処理を少なくとも1回適用する位置調整部とを備えるメッシュ作成装置とする。

(もっと読む)

81 - 90 / 7,589

[ Back to top ]