国際特許分類[G06F5/06]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 処理するデータの順序または内容を変更することなくデータ変換を行うための方法または装置 (126) | データ・フローの速度を変えるためのもの,すなわち速度調整のためのもの (33)

国際特許分類[G06F5/06]の下位に属する分類

格納位置が連続しており、中間のデータは格納または取り出しを行う際にアクセス不能であるもの,例.シフトレジスタを使用するもの (2)

格納位置が連続しており、各データが格納および取り出しを行う際にそれぞれ独立してアクセス可能であるもの,例.ランダムアクセスメモリを使用するもの (4)

多重方式,即ち,2つ以上の同様な装置を使用し、格納および取り出しを行う際に交互にアクセスするもの,例.ピンポン・バッファ

国際特許分類[G06F5/06]に分類される特許

1 - 10 / 27

データ転送装置およびデータ転送方法

【課題】書き込み側と読み出し側とがお互いのアクセスに制約を受けず、自由にリードライトすることができ、データの有効性を向上させることができるデータ転送装置を提供する。

【解決手段】少なくとも2面からなるメモリ11と、書き込み先のメモリ11を所定の順番で切り替えて、かつ所定の周期でデータを送信しメモリ11に書き込ませるデータ送信部10と、書き込みの周期に依存しない周期で少なくとも2面のメモリより同時にデータを受信するデータ受信部12と、データ送信部12がメモリに送信するデータに対して各データに固有な判定情報を付加する判定情報付加部13と、データ受信部12がメモリ11より受信するデータに付加された判定情報を用いてデータが有効であるか否かを判定し、判定結果をデータ受信部に通知する判定情報検査部15とを備えた。

(もっと読む)

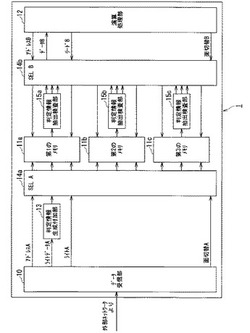

出力制御回路、出力制御回路の制御方法及びその制御プログラム

【課題】順序整合データを、複数のFIFO回路で処理することができる出力制御回路、出力制御回路の制御方法及びその制御プログラムを提供すること

【解決手段】本発明にかかる出力制御回路100は、順序整合データと非順序整合データとの2種類からなるデータのうち、順序整合データが入力された場合、順序整合データを識別する識別情報を生成するデータ解析部101と、互いに異なる順序整合データが割り振られる第1のFIFO回路102及び第2のFIFO回路103と、入力されたデータが順序整合データである場合、前記識別情報に基づいて、当該順序整合データが、当該順序整合データよりも前に入力された非順序整合データよりも後に出力され、当該順序整合データよりも後に入力された非順序整合データよりも前に出力されるように前記第1及び第2のFIFO回路を制御する制御部104を備える。

(もっと読む)

デバイス起動装置およびCPU

【課題】互いに同期していない複数のデバイスにであっても遅延することなく再起動させる。

【解決手段】アドレスを指定することによりデータの書き込み、および、読み出しが可能に構成されたレジスタを複数有するレジスタ回路(100)、アドレスを指定することによってレジスタ回路の複数のレジスタのデータを監視し、かつ、レジスタ回路の予め定められたレジスタにデバイスを起動させるためのデータを書き込むレジスタ制御回路(120)、指定されたアドレスとレジスタ回路から読み出されたデータとに基づいて複数のデバイスのうちいずれかのデバイスに所定の動作を行わせる信号発信回路(110)を備え、レジスタ回路(100)では、複数のレジスタのうち予め定められた第1レジスタに複数のデバイスの各々の動作を共通して管理する第1ビットの集合が割り当てられているとともに、第1レジスタ以外の複数の第2レジスタのそれぞれに複数のデバイスの各々の動作を個別に管理する第2ビットがそれぞれ割り当てられている。

(もっと読む)

メモリアクセス装置、メモリアクセスシステム及びメモリアクセス装置の処理方法

【課題】書き込み制御部のライトポインタの更新に依存することなく、データ転送効率を向上させることができるメモリアクセス装置を提供することを課題とする。

【解決手段】処理部から要求された処理領域に対応するデータのサイズを保持している値に基づいてカウントするカウンタ(111)と、前記処理部と前記処理領域に対応するデータが格納された第1のメモリとの間に接続された第2のメモリ(102)と、前記第2のメモリにおけるリードポインタと前記カウンタの値とに基づいて、前記第2のメモリの状態を検出する検出部(111)と、前記検出部の検出結果に基づいて、前記処理領域に対応するデータを前記第1のメモリから前記第2のメモリに転送するための転送要求を出力する制御部(105)とを有することを特徴とするメモリアクセス装置が提供される。

(もっと読む)

リングバッファメモリ制御装置

【課題】先頭アドレスに基づいてデータの読出しを行うリングバッファメモリ制御装置において、ノイズなどで先頭アドレスが書き変わっていたとしても正常にデータを読み出す。

【解決手段】リングバッファメモリ10に各データが書き込まれる際、各データの先頭に各データの開始を示すデータ開始フラグをそれぞれ付加し、読出制御部2によって各データを読み出す際、その読み出された先頭データがデータ開始フラグであるか否かを判断し、先頭データがデータ開始フラグでないと判断された場合には、先頭データの位置の前方または後方に向かってデータ開始フラグを検索し、その検索によって見つけ出されたデータ開始フラグの位置からデータの読出しを行う。

(もっと読む)

リングバッファ回路及びその制御回路

【課題】読み出しと書き込みが同期しているか、非同期であるかに係わりなく、データが満杯であるか空であるかを正しく検出できるリングバッファ回路及びリングバッファ回路の制御回路を提供する。

【解決手段】Nビットで指定されるアドレスを有するリードライトメモリと、N+1ビットのグレイコードをカウントするリードライトメモリの書き込みアドレスカウンタポインタ及び読み出しアドレスカウンタポインタと、書き込み、読み出しアドレスカウンタポインタの出力するN+1ビットのグレイコードをリードライトメモリの書き込み、読み出しアドレスとして直接指定可能なNビットのアドレスに変換する書き込み、読み出しアドレス変換回路と、を有する。

(もっと読む)

速度変換回路

【課題】シングルポートメモリを用いて、データが欠けることなく連続した書き込み及び読み取りを行う。

【解決手段】書き込み用のクロック周波数からなる第1のクロック信号に同期した書き込みデータが保持されるライトバッファ回路と、前記第1のクロック信号と、前記第1のクロック信号と独立した読み取り用のクロック周波数からなる第2のクロック信号との非同期吸収を行う非同期吸収回路と、シングルポートメモリに対する書き込み及び読み取りを制御するRAMコントローラ回路とを有し、前記非同期吸収回路は、前記ライトバッファ回路で保持された書き込みデータを、前記第2のクロック信号に対応させてデータ長を調整し、調整された書き込みデータを前記RAMコントローラ回路へ出力することにより上記課題を解決する。

(もっと読む)

データ受信装置、該データ受信装置を備えた画像形成装置及びデータ受信方法

【課題】 ホストコンピュータ81と、CPU70、RAM71、及びROM82を含む画像処理装置とを接続する制御LSI100において、処理目的の異なる第一のデータと第二のデータとを、一方のデータを消滅させることなく他方のデータを受信すること。

【解決手段】 データラッチ[1]回路76、及びデータラッチ[2]回路77は、それぞれ処理目的の異なるデータを格納し、シフトクロック生成回路79は、所定の信号を受け入れると、データラッチ[1]回路76が格納するデータをデータラッチ[2]回路77へシフトさせる。

(もっと読む)

データバッファリング装置

【課題】要求元からの可変データ取得要求に応じて割り込みアドレスが変更される場合でも、要求元からは連続したアドレス領域のデータ取得を可能とするデータバッファリング装置を実現する。

【解決手段】時系列的に発生するデータが書き込み手段を介して先頭アドレスより最終アドレスまで書き込まれ、次のデータが前記先頭アドレスに上書きされるリングバッファ部と、このリングバッファ部への指定アドレスから所定数のデータを取得するデータ処理部を具備するデータバッファリング装置において、

前記リングバッファ部の最終アドレスに引き続く先頭アドレスを持つ補助バッファ部を備え、

前記書き込み手段は、前記リングバッファ部の先頭アドレス及び前記補助バッファ部の先頭アドレスより所定数の同一データを並行して書き込む。

(もっと読む)

データ処理装置

【課題】複数の連続する入力データの内から選択したデータのみを詰めて記憶装置に書き込む処理を高速に実施する。

【解決手段】無効を示す「0」又は有効を示す「1」をもつ有効フラグと対になり、且つ連続して入力する入力データD0〜D7を、4個づつ処理するデータ処理装置である。入力データをD0〜D3、D4〜D7毎に取り込み、当該データより順序が前の全てのデータの有効フラグ値の合計値を当該データの有効フラグ積算値として有効フラグ積算器10で算出し、得られた有効フラグ積算値をアドレスとして、前記入力データの内の有効フラグで有効と指定されたデータを記憶装置に書き込む。

(もっと読む)

1 - 10 / 27

[ Back to top ]