国際特許分類[G06F7/00]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915)

国際特許分類[G06F7/00]の下位に属する分類

デジタル値の比較 (26)

個々の記録担体上のデータを分類,選別,組合せ,または別々の記録担体上のデータを比較するための装置

連続的記録担体,例.テープ,ドラム,ディスク,上のデータを分類または組合せる装置 (51)

位取り記数法を用いて計算を行なうための方法または装置,例.2進,3進,10進法を用いるもの (331)

乱数または擬似乱数発生器 (209)

デジタルな非位取り記数法,すなわち.基数を用いない数表現を用いて計算を行うための方法または装置;位取り記数法と非位取り記数法の組合せを用いる計算装置 (35)

1語内の,指定値を有する1以上のビットの位置を選別または符号化すること,例.最上位または最下位の有意な0または1の検出,プライオリティ・エンコーダ (6)

データ内容から独立して定められたルールによるデータの再配置,並べ替え,または選別のための装置 (42)

国際特許分類[G06F7/00]に分類される特許

101 - 110 / 215

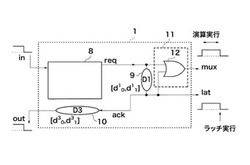

非同期式回路の制御回路

【課題】特別の休止相を設けることなく、各回路ブロックの演算終了後、初期状態に復帰することにより、高速化、低消費電力化を実現する非同期式回路の制御回路を提供する。

【解決手段】複数の回路ブロックが互いに他の回路ブロックと制御信号をやり取りすることにより一連の演算を実行する、非同期式回路において、入力制御信号が“1”から“0”に遷移したことをトリガとして演算を実施し、演算中、出力制御信号として“1”を出力し、演算が終了した後、出力制御信号を“0”に復帰するようにする。ここで、“0”とは、各回路ブロックの待機状態に対応する制御信号のステートを表したものであり、具体的な電圧等を表しているものではない。

(もっと読む)

データ処理装置、画像処理装置、及びデータ処理プログラム

【課題】再構成可能な演算回路を用いたデータ処理の高速化を図る。

【解決手段】最初、再構成回路22には、画像処理Xを行うX処理部80と、X処理部80が出力する中間データDxを用いて画像処理Aを行うA処理部82とが配置されている。再構成の条件を満たした場合、再構成回路22は全面的に再構成されて、X処理部84とB処理部86が配置される。X処理部84は、X処理部80と同じ論理回路をもち、X処理部80が保持していた中間データDxを保持している。したがって、B処理部86は、中間データDxを用いて直ちに画像処理Bを行うことができる。

(もっと読む)

ベクトル演算装置及びその方法

【課題】 一つのベクトル命令のみで、最大値や最小値を、要素毎に算出可能とすると共に、長時間ベクトルデータレジスタ内要素の保持を不要としたベクトル演算装置を提供する。

【解決手段】 複数のベクトルデータの要素の各々A,Bを、比較に要する時間だけ保持するベクトルデータ保持回路30を設け、要素A,Bの減算処理による比較回路20の比較結果に基いて、このベクトルデータ保持回路30のうち最も大きい要素または最も小さい要素を選択して演算結果Cとして導出する。これにより、一つの命令で、要素毎に最大値または最小値を求めることが可能となり、この演算が行われ次第、ベクトルデータレジスタ41〜43には要素の保持が必要なくなり、次の要素の書込みが可能となる。

(もっと読む)

半導体集積回路

【課題】システム全体のデータ転送量が増加してしまうことを解消することによって、システムの設計を容易にする。

【解決手段】演算器アレイ(102)と、メモリアレイ(103)と、データ転送回路(108)と、スイッチ回路(104)とを設ける。さらに上記演算器アレイ、上記メモリアレイ、上記データ転送回路、及び上記スイッチ回路における論理的動作を定義する構成情報を管理する構成情報管理部(106)と、上記構成情報の切替えを制御可能な状態遷移管理部(105)とを設ける。そして、上記データ転送回路は、上記構成情報に含まれる設定に従って、データの入れ替えのタイミングを判定し、自律的にデータ入れ替えを実行可能な制御回路を設けることで、システム設計の容易化を図る。

(もっと読む)

浮動小数点演算機能を有する電子制御装置

【課題】浮動小数点演算機能を有する電子制御装置において、浮動小数点演算により非数が発生した際には、演算により求められた変数同士の相関関係を保持し、処理負荷を大きくすることなく非数による制御不良を防止する。

【解決手段】浮動小数点演算プロセッサが演算した浮動小数点型データを保存するRAM15の記憶領域31を複数の記憶部32Aに分割し、幾つかの連続した記憶部32Aの集合であるブロック(吸気制御ブロック33A、噴射制御ブロック33B等)を制御単位で割り当てておく。ここで、各制御が終了する度に、ブロック単位で記憶部32Aに非数32Bがあるか否かを判定し、非数32Bがあると判定すると、ブロックの先頭アドレスからブロックの終了アドレスまでを一括して初期化する。この結果、変数同士の相関関係を保持し、RAM15の初期化の際の処理負荷を軽減しながら、非数32B発生時の制御不良を防ぐことができる。

(もっと読む)

プログラマブルロジックデバイスのための大きな乗算器

【課題】プログラマブルロジックデバイス(PLD)のための特殊処理ブロックで、単一のブロック内で実行され得るよりも大きな乗算の実行を容易にして、PLDの汎用プログラマブルリソースへの依存を低減または排除するロジックを備えるものを提供すること。

【解決手段】乗算器と、これらの乗算器の結果を加算する加算器のための回路網とを含むPLD内の複数の特殊処理ブロックは、加算する前に乗算器の結果をシフトするための選択可能な回路網を、該特殊処理ブロックに追加することによって、より大きな乗算器として構成され得る。一つの実施形態において、このことは、最終的な加算を除く全てが、特殊処理ブロック内で行われ、該最終的な加算は、プログラマブルロジック内で行われることを可能にする。別の実施形態において、追加の圧縮および加算の回路網は、最終的な加算でさえも、特殊処理ブロック内で行われることを可能にする。

(もっと読む)

リコンフィギュラブルSIMDベクトル処理システム

【課題】リコンフィギュラブルSIMDベクトル処理システムを提供する。

【解決手段】システムであって、冗長形式で表される2Nビットの積をM個出力するM個のNビット×Nビット乗算器と、M個の2Nビットの積を受け取り、M個の2Nビットの積に基づいて冗長形式で表されるMNビットの積を生成するコンプレッサと、M個の2Nビットの積およびMNビットの積を受け取り、M個の2Nビットの積およびMNビットの積のうちいずれかを選択し、選択した積を非冗長形式に変換する加算器ブロックとを備えるシステムを提供する。

(もっと読む)

集積回路及びリコンフィギュラブル回路の入力データ制御方法

【課題】入力データをリコンフィギュラブル回路で確実に処理できるようにする。

【解決手段】本集積回路は、再構成可能に相互に結合される複数の演算器を含むリコンフィギュラブル回路3と、入力データ制御部4とを備える。そして、入力データ制御部4によって、リコンフィギュラブル回路3の構成に応じてデータが入力されるように入力データが制御される。

(もっと読む)

処理装置

【課題】 回路規模の縮小化に貢献するリコンフィギュラブル回路およびその周辺技術を提供する。

【解決手段】 処理装置は、論理回路の機能をノードとして表現して、入力データから出力データに至るデータの流れをノードの接続で表現するデータフローグラフを生成するDFG生成部と、生成されたデータフローグラフをもとに、構成情報を生成する構成情報生成部と、機能の変更が可能なリコンフィギュラブル回路と、前記リコンフィギュラブル回路に所期の回路を構成するための構成情報を供給する設定部とを備える。この処理装置において、前記DFG生成部は、あるノードの出力数が、対応する論理回路が接続できる論理回路の数よりも多い場合は、データフローグラフにおいて、入力を同一とする別のノードを複製して、ノード出力を分散させる。

(もっと読む)

半導体装置

【課題】動的に回路構成を再構成可能な半導体装置にて、回路構成の再構成に係る制御情報量を低減できるようにする。

【解決手段】コンフィグレーションデータを記憶する制御データ用メモリ24と、演算器26とを有し、コンフィグレーションデータに応じて回路構成を再構成可能な複数の演算部22と、コンフィグレーションデータを制御データ用メモリから出力させるための構成指定データを記憶するコンフィグレーションメモリ13Aとを備え、コンフィグレーションメモリにはコンフィグレーションデータを記憶せずに、制御データ用メモリからコンフィグレーションデータを出力させるための情報のみを記憶するだけで、コンフィグレーションデータを供給することができるようにする。

(もっと読む)

101 - 110 / 215

[ Back to top ]