国際特許分類[G06F7/00]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915)

国際特許分類[G06F7/00]の下位に属する分類

デジタル値の比較 (26)

個々の記録担体上のデータを分類,選別,組合せ,または別々の記録担体上のデータを比較するための装置

連続的記録担体,例.テープ,ドラム,ディスク,上のデータを分類または組合せる装置 (51)

位取り記数法を用いて計算を行なうための方法または装置,例.2進,3進,10進法を用いるもの (331)

乱数または擬似乱数発生器 (209)

デジタルな非位取り記数法,すなわち.基数を用いない数表現を用いて計算を行うための方法または装置;位取り記数法と非位取り記数法の組合せを用いる計算装置 (35)

1語内の,指定値を有する1以上のビットの位置を選別または符号化すること,例.最上位または最下位の有意な0または1の検出,プライオリティ・エンコーダ (6)

データ内容から独立して定められたルールによるデータの再配置,並べ替え,または選別のための装置 (42)

国際特許分類[G06F7/00]に分類される特許

41 - 50 / 215

回路のモジュール間に選択的に使用可能な専用連結を有するモジュール式デジタル信号処理回路

所望の場合に、より大きな(例えば、より複雑および/またはより演算上正確な)DSP演算を行うように、より簡単に連動することができるデジタル信号処理(「DSP」)回路ブロックを提供する。これらのDSPブロックはまた、あるブロックを使用できないにもかかわらず(例えば、回路欠陥のために)、複数のそのようなブロックをつなぎ合わせることを容易にする冗長回路を含んでもよい。シストリックレジスタが、シストリック型の有限インパルス応答(「FIR」)デジタルフィルタを実装するよう、ブロックの使用を容易にするために、DSPブロックの中の種々のポイントに含まれてもよい。  (もっと読む)

(もっと読む)

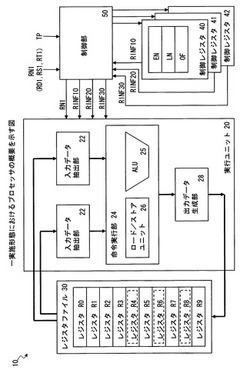

プロセッサ

【課題】 レジスタのビット幅に対して半端なデータサイズのデータが連続する際に、レジスタを有効に使用する。

【解決手段】 プロセッサは、入力されたデータに対する演算を実行する演算部と、データが格納される複数の第1レジスタと、入力データ抽出部とを有している。例えば、入力データ抽出部は、演算対象のデータを含む入力ビット列が格納された第1レジスタから入力ビット列を読み出す。そして、入力データ抽出部は、予め設定された第1位置情報に基づいて、読み出した入力ビット列から演算対象のデータを抽出し、抽出した演算対象のデータを演算部のビット幅に拡張する。

(もっと読む)

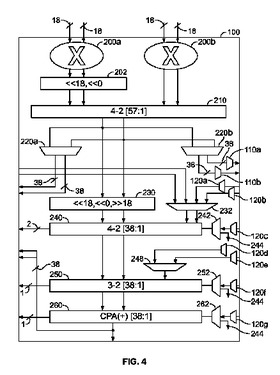

動的再構成可能な積和演算装置および動的再構成可能プロセッサ

【課題】小型で高速かつ入力データ数の変更に対応でき、様々な積和演算系の処理にも対応可能な動的再構成可能な積和演算装置を得る。

【解決手段】乗算器100〜103とデータ結合器200〜203と加減算器500,501,504,506とシフタ400〜403,408,409,412,414とを、乗算器100〜103側を入力としてツリー状に接続する。セレクタ300〜303,308,309,312,313は、乗算器100〜103とデータ結合器200〜203の出力を動的に選択すると共に、シフタ400〜403,408,409,412,413の出力を動的に選択する。

(もっと読む)

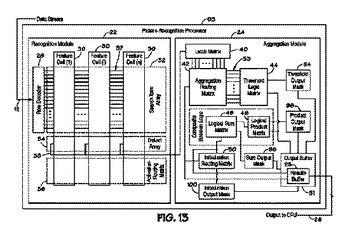

並列パターン検索エンジンのパターンマッチング結果を通信するための装置、システム、および方法

開示されているのは次のような方法およびシステムである。その中には、データストリーム(12)を検索するための一つ以上のパターン認識プロセッサ(14,93)を含む装置を含むシステムがある。パターン認識プロセッサ(14,93)のクラスタは、様々な検索機能を実行するために使用されてよい、さまざまなパターンマッチングマトリクス(40、42、44、46、48、50)およびマスクモジュール(94、96、98、100)を含んでよい。さらに、バッファ(25)は、情報検索に対する、パターンマッチングマトリクス(40、42、44、46、48、50)およびマスクモジュール(94、96、98、100)からの続いて起こる様々な結果を個別に記憶するために使用されてよい。  (もっと読む)

(もっと読む)

演算処理装置および変換装置

【課題】複数の演算器を含む演算部を備える演算処理装置において、乗算を効率的に実行したい。

【解決手段】演算処理装置は外部から供給される設定データに応じて機能の変更が可能な演算部10を備える。演算部10は、は、乗算を除く複数種類の算術論理演算を選択的に実行可能な第1演算器11〜46と、乗算を単体で実行可能な第2演算器61、71とを備える。第1演算器11〜46は、x(xは2以上の整数)行×y(yは2以上の整数)列の第1演算器アレイを構成してもよい。第2演算器61、71は、m(mはx以下の自然数)行×n(nは自然数)列の、第2演算器列または第2演算器アレイを構成してもよい。

(もっと読む)

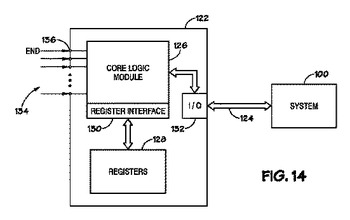

装置のエンディアンモードを管理するためのシステムおよび方法

エンディアン性を管理するためのシステム、方法、および装置が開示される。

一実施形態において、装置が、ビッグエンディアン動作モードまたはリトルエンディアン動作モードのうちの1つで選択的に動作するように構成される。その装置は、その装置の現在のエンディアンモードがレジスタ内の少なくとも2つの異なるビット位置で指示されるレジスタを含んでよい。その少なくとも2つのビット位置は、もしその装置およびシステムが同じエンディアンモードで動作するならば、そのシステムによってそのビット位置のうちの1つでデータが読まれるように選択され、もしその装置とシステムが互いに異なるエンディアンモードで動作するならば、選択されたビット位置の他方のデータビットがそのシステムによって読み出される。幾つかの実施形態において、その装置のエンディアンモードは、ハードウェア入力またはソフトウェア入力によって制御される。  (もっと読む)

(もっと読む)

演算処理装置、それを搭載した通信装置および放送受信装置、ならびに情報処理装置

【課題】アクセスされるべきアドレスが演算結果に依存する演算データのアドレス生成にも対応可能でありながら、演算部の処理パフォーマンスを高めたい。

【解決手段】制御部20は、機能の変更が可能な演算部10に、設定データを供給する。記憶部30は、演算部10で処理される演算データを保持する。記憶部30内の第1記憶領域は、制御部20からアドレスが供給される。記憶部30内の第2記憶領域は、演算部10からアドレスが供給される。

(もっと読む)

情報処理装置、情報処理方法及びプログラム

【課題】大きな記憶域を使用することなく、漸進的に決定性有限状態オートマトンの状態数を減少させることが可能な情報処理装置、方法及びプログラムを提供する。

【解決手段】決定性有限オートマトンを構成する各状態を、出て行く遷移に付随する入力記号と終了性とが同じ状態毎に分類し、探索部が、各状態の遷移先状態の集合との積集合のサイズが1以下となるまで、この積集合に含まれる状態の遷移先状態の集合を新たな状態の集合とみなして前記積集合を算出し、前記探索部が辿った遷移方向とは逆向きに辿りながら互いに区別不可能な複数の状態を一の状態に併合する。

(もっと読む)

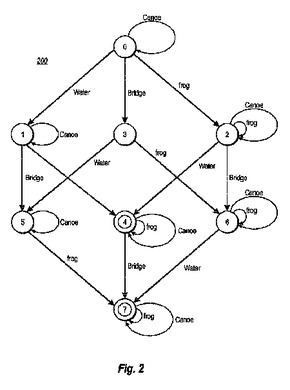

モジュラフォレストオートマトン

モジュラフォレストオートマトン(MFA)は、半順序正規ツリーパターンについての統一された記載を提供する。MFAはまた、これらのパターンの決定化、サブタイプ化、交わり、および相補のための簡素な方法を提供する。MFAは、高性能のパターン分析およびマッチングをサポートする。モジュラフォレストオートマトンと併せて、モジュラフォレストトランスデューサにより、コンパイラが、セマンティックアクションを任意の状態遷移におくことが可能にされ、一方でラベル付き有向グラフの効率的な変換がサポートされる。  (もっと読む)

(もっと読む)

ネステッドループおよびプログラミングツールのためのリコンフィギュラブルコプロセッサアーキテクチャテンプレート

【課題】開発期間が長期化するASICsの変更設計を容易にするアーキテクチャテンプレートを提供する。

【解決手段】提案するテンプレートから得られるアーキテクチャは一般的なチップシステム(SoC)に集積され、ボディが平行のファンクショナルユニットアレイにおいて実行されるオペレーションのエクスプレッションであるネステッドプログラムループを実行するリコンフィギュラブルコプロセッサにより構成されている。

(もっと読む)

41 - 50 / 215

[ Back to top ]