国際特許分類[G06F7/00]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915)

国際特許分類[G06F7/00]の下位に属する分類

デジタル値の比較 (26)

個々の記録担体上のデータを分類,選別,組合せ,または別々の記録担体上のデータを比較するための装置

連続的記録担体,例.テープ,ドラム,ディスク,上のデータを分類または組合せる装置 (51)

位取り記数法を用いて計算を行なうための方法または装置,例.2進,3進,10進法を用いるもの (331)

乱数または擬似乱数発生器 (209)

デジタルな非位取り記数法,すなわち.基数を用いない数表現を用いて計算を行うための方法または装置;位取り記数法と非位取り記数法の組合せを用いる計算装置 (35)

1語内の,指定値を有する1以上のビットの位置を選別または符号化すること,例.最上位または最下位の有意な0または1の検出,プライオリティ・エンコーダ (6)

データ内容から独立して定められたルールによるデータの再配置,並べ替え,または選別のための装置 (42)

国際特許分類[G06F7/00]に分類される特許

71 - 80 / 215

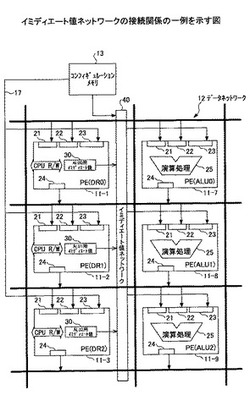

リコンフィギュラブル回路

【課題】本発明は、効率的且つ柔軟にイミディエート値をプロセッサエレメントに供給することが可能なリコンフィギュラブル回路を提供することを目的とする。

【解決手段】リコンフィギュラブル回路は、複数のプロセッサエレメントと、複数のプロセッサエレメントの演算データ入力ポートと出力ポートとに結合されるデータネットワークと、第1のプロセッサエレメントのコンフィギュレーションデータ入力ポートにコンフィギュレーション経路を介して結合されるコンフィギュレーションメモリと、前記データネットワークとは独立なネットワークであり、第2のプロセッサエレメントのコンフィギュレーションデータ入力ポートに結合されるイミディエート値ネットワークとを含み、第3のプロセッサエレメントの内部レジスタが、内部レジスタの格納データをイミディエート値ネットワークに出力可能なように、イミディエート値ネットワークに結合される。

(もっと読む)

ステートマシン及びこれを用いた半導体集積回路

【課題】簡単で低コストなハードウェア構成で、且つ、ハードウェアの回路構成を変更せずにステートマシンの制御内容を任意に変更する。

【解決手段】クロック同期型メモリ30を用い、このメモリ30の各アドレスにムーア型ステートマシン20の状態Sを表すデータを格納しておく。そして、ステートマシン20に対する入力信号in[j-1:0]と、メモリ30のリードデータrdata[m:0]の中の状態Sを表すデータrdata[m:k]とを組み合わせて、セレクタ21を介してメモリ30のアドレスに入力することで、クロック信号clkに同期して状態Sを変化させながら動作するムーア型ステートマシン20として振る舞わせる。

(もっと読む)

リコンフィギュラブル回路,リコンフィギュラブル回路の機能変更方法および通信装置

【課題】複数の演算エレメントと、演算エレメント間を相互に接続する複数の配線スイッチからなるリコンフィギュラブル回路のテスト時間を削減する。

【解決手段】複数の演算エレメントと、演算エレメント間を相互に接続する複数の配線スイッチからなるリコンフィギュラブル回路Aにおいて、第1の演算エレメントE1に内蔵されたコンフィギュレーションメモリ11のコンフィギュレーションデータのうち所定のビットを第2の演算エレメントE2を使って更新し、第1の演算エレメントE1または第3の演算エレメントE3の機能を変更する回路構成を持つ。

(もっと読む)

再構成可能な回路装置及び受信装置

【課題】従来は、コンフィギュレーションデータの付随情報に応じて、コンフィギュレーションするかどうかを決定することなどができない。また、再構成可能なコア内のリソースを使って付随情報を保持するため、本来使用するべき回路のためのリソースが減ってしまうという課題があった。

【解決手段】コンフィギュレーションデータと付随情報とを出力する第1の制御手段102と、前記付随情報を入力して格納する第1の記憶手段103と、前記コンフィギュレーションデータを入力して回路を再構成するコア104とを備えたことを特徴とする再構成可能なデバイスであり、第1の記憶手段103の情報をCPUなどの外部デバイスにより読み出すことで、再構成可能なコア104に構成されている回路に関する情報を得る。

(もっと読む)

データ処理装置

【課題】再構成可能な論理回路の再構成時間を短縮し、データ処理の高速化は図ることができるようにしたデータ処理装置を提供する。

【解決手段】回路情報源15に論理回路Bの論理回路Aとの差分回路情報W(A→B)を保持させる。論理再構成制御部16は、再構成可能な論理回路12に論理回路Aを再構成して論理回路Aに任されている処理を実行させた後、再構成化可能な論理回路12に論理回路Bを構成する場合、回路情報源15から論理回路Bの論理回路Aとの差分回路情報W(A→B)を読み出し、再構成可能な論理回路12内の再構成を必要とする番地の情報と、再構成する番地の回路情報とを回路情報保持レジスタ19に転送する。

(もっと読む)

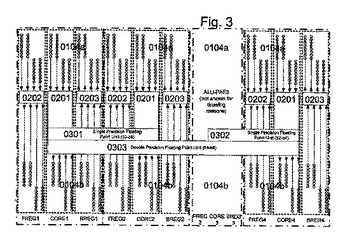

リコンフィギュラブルな浮動小数点レベルおよびビットレベルのデータ処理ユニット

リコンフィギュラブルなデータ処理ユニットの複数の固定小数点ユニットのブロックが、該ブロック内に固定実装された共通の同じハードウェアによって、浮動小数点数を効率的に演算する機能を支援する。  (もっと読む)

(もっと読む)

再構成ユニットによる解探索の方法およびデータ処理装置

【課題】遺伝的アルゴリズムにより解を探索するのに適したデータ処理装置を提供する。

【解決手段】回路を再構成可能なPEマトリクス10と、PEの接続情報を含むコンフィグレーションデータ18により回路を再構成する制御ユニット2aと、遺伝的アルゴリズムによりヒューリスティックにコンフィグレーションデータ(発見的コンフィグレーションデータ、GCD)を生成する生成ユニット2bとを有するデータ処理装置50を提供する。データ処理装置50は、さらに、発見的なコンフィグレーションデータにより再構成される評価対象回路61に対し入力データの複数のサンプルを供給するサンプルデータ供給ユニット62と、評価対象回路61の出力データの少なくとも一部を用いて評価する評価ユニット63とを含む。

(もっと読む)

演算装置、演算システムおよび演算方法

【課題】処理の効率化を図ることができる。

【解決手段】演算装置1は、動的に再構成可能な装置である。演算部2は、演算内容に応じて演算に必要な機能を動的に組み替えて演算処理を行う。データ処理部3は、所定のヘッダ情報が格納されているヘッダ4とデータ本体5とを備える処理対象データ6を受け取ると、ヘッダ情報に応じてデータ本体5の演算内容を決定する。決定された演算内容は、コンフィギュレーションメモリ7に送られる。コンフィギュレーションメモリ7は、演算部2等に所定の動作を行わせるコンフィグデータを複数有しており、演算内容に従ったコンフィグデータを演算部2に送る。

(もっと読む)

文字列照合回路

【課題】NFAをハードウェアに直接埋め込む形の文字列照合回路において、文字の繰り返し回数の大きい正規表現を少ない回路規模で効率的に実現する。

【解決手段】照合条件を表す正規表現から構成したNFA(Non-deterministic Finite Automaton)を回路化した文字列照合回路であって、正規表現に含まれる部分表現のうち、指定文字cの繰り返し回数Nを指定した正規表現は、照合対象文字とマッチ情報入力とを入力に持ち、マッチ情報出力を出力に持つc{N}-NFA回路201によって回路化されている。c{N}-NFA回路201は、入力された照合対象文字101と指定文字との連続一致回数を数えるカウンタ112と、連続一致回数が指定繰り返し回数Nに達したか否かを判定する判定回路113とを含む。

(もっと読む)

オートマトンの決定化方法、有限状態トランスデューサの決定化方法、オートマトン決定化装置及び決定化プログラム

【課題】決定化の実行時に要するメモリ量を減少させることが可能なオートマトンの決定化方法、有限状態トランスデューサの決定化方法、オートマトン決定化装置及びオートマトンの決定化プログラムを提供する。

【解決手段】非決定性モデルに含まれた遷移から、決定化対象とする一部の遷移を決定化に係る処理の繰り返し毎に選択し、この選択した一部の遷移についての決定化時に生成された状態の組み合わせからなる決定化済み状態の名称を、処理の繰り返し毎に互いに異なる単一の名称に変更する。

(もっと読む)

71 - 80 / 215

[ Back to top ]