国際特許分類[G06F7/00]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915)

国際特許分類[G06F7/00]の下位に属する分類

デジタル値の比較 (26)

個々の記録担体上のデータを分類,選別,組合せ,または別々の記録担体上のデータを比較するための装置

連続的記録担体,例.テープ,ドラム,ディスク,上のデータを分類または組合せる装置 (51)

位取り記数法を用いて計算を行なうための方法または装置,例.2進,3進,10進法を用いるもの (331)

乱数または擬似乱数発生器 (209)

デジタルな非位取り記数法,すなわち.基数を用いない数表現を用いて計算を行うための方法または装置;位取り記数法と非位取り記数法の組合せを用いる計算装置 (35)

1語内の,指定値を有する1以上のビットの位置を選別または符号化すること,例.最上位または最下位の有意な0または1の検出,プライオリティ・エンコーダ (6)

データ内容から独立して定められたルールによるデータの再配置,並べ替え,または選別のための装置 (42)

国際特許分類[G06F7/00]に分類される特許

81 - 90 / 215

データ流の管理方法

【課題】産業的使用のために新たなものを提供すること。

【解決手段】データ流の管理方法において、データに識別子を割り当てる、

ことを特徴とする方法。

(もっと読む)

情報処理システム、プログラマブル論理回路装置、配線方法、論理回路作成方法、及び、プログラム

【課題】時間パラメータを含む三次元に効率よく論理回路を配置できる情報処理システム、プログラマブル論理回路、及び、配線方法を提供する。

【解決手段】情報処理システムは、PLD(Programmable Logic Device)を備える。PLDは、モジュールを備える。モジュールは、複数の演算器エレメントを備える。情報処理システムは、二次元論理回路110を作成し、二次元論理回路110に基づいて仮想的な三次元論理回路120を作成する。PLDは、仮想的な三次元論理回路120を、時間パラメータを含む三次元論理回路として動的に再構成しながら、つまり、モジュールを論理回路A〜Dの順に再構成しながら、データ処理を行う。

(もっと読む)

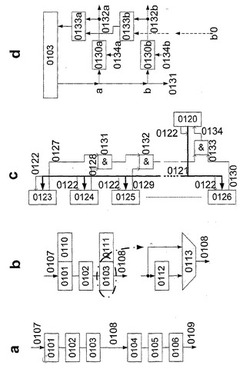

データフローグラフ生成装置、設定データ生成装置、処理装置、及びデータフローグラフ生成方法

【課題】多倍長演算が可能なリコンフィギュラブルプロセッサに対応したデータフローグラフを自動的に生成する。

【解決手段】リコンフィギュラブル回路の論理回路で行う演算に必要な演算ビット数を決定する演算ビット数決定部と、演算に対応するノードを生成するノード生成部を備え、前記ノード生成部は、前記必要な演算ビット数が前記演算可能な演算ビット数よりも小さい又は等しいとき、前記1つの演算に対応する1つのノードを生成し、前記必要な演算ビット数が前記演算可能な演算ビット数よりも大きいとき、前記1つの演算に対応して複数のノードを生成する。

(もっと読む)

動的再構成可能演算装置および半導体装置

【課題】面積効率の高い動的再構成可能演算装置を得る。

【解決手段】乗算器100〜107は、それぞれ2入力の乗算を行う。加算器200〜203は、乗算器100〜107の乗算結果出力100c〜107cを入力として加算を行う。加算器204,205は、加算結果出力200a〜203aか乗算結果出力100c,101c,106c,107cかを入力として加算を行う。加算器206,207は、加算結果出力204a,205aか乗算結果出力102c〜105cかを入力として加算を行う。

(もっと読む)

動的再構成プロセッサ

【課題】実行するアプリケーションによって処理性能が大きく変わることなく、ゲート規模やゲート利用率の観点から効率のよい動的再構成プロセッサを得る。

【解決手段】再構成可能演算部3は、積和演算部と並べ替え部とパターンマッチ/換字部と論理演算部のうち少なくとも一つの演算部を有し、かつ、その演算部における入力から出力に至る論理経路が選択可能に構成されている。演算制御部1は、再構成可能演算部3の論理経路情報を演算制御メモリ4に書き込み、再構成可能演算部3は、演算制御メモリ4に記憶された論理経路情報に基づいて、使用する演算部とその論理経路が設定される。

(もっと読む)

信号処理

【課題】信号を処理する方法を提供すること。

【解決手段】信号データ値および畳み込みフィルタ係数値を、畳み込み値を計算するために使用される一組のプロセッサ(cutil)中の対象プロセッサ(ct)にロードするためのプロセス。係数値はcutilにマッピング(150)される。データ値と係数値のインターリーブ(160)がctについて決定される。係数値がctにロードされ、データ値がctにロードされ、それによって畳み込み値の計算(170)に参加するようctを準備する。

(もっと読む)

半導体装置

【課題】処理性能の劣化を抑制しながら、命令メモリの容量を小さくすることができる。

【解決手段】本発明の半導体装置1は、複数の演算装置10A〜10Eと、所定の状態遷移に応じて複数の演算装置を制御するコントローラ11と、演算処理対象のデータを記憶する第1の記憶部12と、複数の演算装置で行われる演算処理を指定する回路情報を記憶する第2の記憶部と、第1の記憶部12へのデータアクセス情報と第2の記憶部へのポインタとを、コントローラ11が取り得る状態と関連付けて記憶する第3の記憶部とを備え、コントローラ11は、状態に応じて第3の記憶部に記憶された読み出しアドレスとポインタとを読み出し、読み出したポインタによって指定される第2の記憶部の領域に記憶された回路情報を複数の演算装置10A〜10Eへ送信することを特徴とする。

(もっと読む)

プロセッサ装置

【課題】ハードウェア資源を有効に活用できる動的再構成可能なプロセッサ装置を提案する。

【解決手段】本発明のプロセッサ装置1は、それぞれが同期動作し制御信号に応じた処理を行う複数の機能ブロック10a、10b、10cと、各機能ブロック10a、10b、10cの入出力11a〜12cの帯域幅よりも小さい帯域幅に変更可能であって各機能ブロック10a、10b、10c間を接続する接続手段30と、接続手段30の帯域幅を変更する第1の変更手段と、各機能ブロック10a、10b、10cの入出力データのデータ転送速度を変更する第2の変更手段と、第1の変更手段と第2の変更手段とを制御する制御手段50とを備えることを特徴とする。

(もっと読む)

グラフのパーティショニング方法

【課題】産業的使用のために新たなものを提供すること。

【解決手段】インタフェースエッジにメモリを挿入する、ことを特徴とするグラフのパーティショニング方法。

(もっと読む)

データ処理装置

【課題】「パイプライン方式」の専用演算装置を使用する場合とほぼ同等のハードウエア規模で、より短時間でのデータ処理を可能にする。

【解決手段】前処理用の第1の演算装置20Aと後処理用の第2の演算装置30Aで構成する。第1の演算装置20Aでは、第2の演算装置30Aで演算する必要があるデータのみを保持し、第2の演算装置30Aで演算する必要のあるデータは、第1の演算装置20Aからの制御情報に従い、第2の演算装置30Aで演算する。これにより、第2の演算装置30Aで処理するデータ量を削減し、データ処理に要する時間を短縮する。

(もっと読む)

81 - 90 / 215

[ Back to top ]