国際特許分類[G06F7/00]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915)

国際特許分類[G06F7/00]の下位に属する分類

デジタル値の比較 (26)

個々の記録担体上のデータを分類,選別,組合せ,または別々の記録担体上のデータを比較するための装置

連続的記録担体,例.テープ,ドラム,ディスク,上のデータを分類または組合せる装置 (51)

位取り記数法を用いて計算を行なうための方法または装置,例.2進,3進,10進法を用いるもの (331)

乱数または擬似乱数発生器 (209)

デジタルな非位取り記数法,すなわち.基数を用いない数表現を用いて計算を行うための方法または装置;位取り記数法と非位取り記数法の組合せを用いる計算装置 (35)

1語内の,指定値を有する1以上のビットの位置を選別または符号化すること,例.最上位または最下位の有意な0または1の検出,プライオリティ・エンコーダ (6)

データ内容から独立して定められたルールによるデータの再配置,並べ替え,または選別のための装置 (42)

国際特許分類[G06F7/00]に分類される特許

1 - 10 / 215

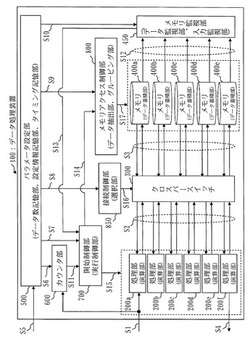

データ処理装置およびデータ処理方法およびプログラム

【課題】演算部の演算開始タイミングを変化させてデータ処理を行うデータ処理装置を実現する。

【解決手段】メモリ400aは、先行して演算を実行する処理部200aが生成したデータを蓄積する。メモリ監視部450は、メモリ400aが蓄積するデータのデータ数を監視し、後続して演算を実行する処理部200bが演算に必要なデータ数が蓄積されたら、メモリ400aが蓄積するデータを処理部200bに出力させる。処理部200bはデータが出力されるタイミングで演算を開始し、データが出力されるタイミングの変化に対応して、処理部200bの演算開始タイミングが変化する。

(もっと読む)

演算処理装置及び演算処理システム

【課題】装置のコストアップを招くことなく、装置の出荷後にユーザーが使用しない機能を装置本体に組み込む必要をなくす。

【課題を解決するための手段】演算処理装置としての制御部10は、PLL回路100と、CPU101と、調整工程用プログラムを記憶している外部デバイス30との接続が可能なインターフェイス105と、フラグ1011とを備え、CPU101は、フラグ1011が調整工程モードを示すとき、外部デバイス30から調整工程用プログラムの命令コードをフェッチする速度に対応するクロック数にPLL回路100によって変更された動作クロックに基づいて、外部デバイス30から命令コードをフェッチするとともに、当該フェッチした命令コードのデコードにより解析した命令内容を実行する。

(もっと読む)

演算回路及び演算装置

【課題】3つ以上の値の条件分岐処理を要する比較演算を高速に行うことができる演算回路及び演算装置を提供すること。

【解決手段】本発明にかかる演算回路100は、加減算器CAL11〜CAL13、セレクタSEL11〜SEL13及び判定器40を有する。加減算器CAL11〜CAL13は、入力するデータD0〜D2に対して演算を行い、演算結果に基づいて生成した符号フラグF1〜F3出力する。セレクタSEL11〜SELは、加減算器CAL11〜CAL13に入力するデータD0〜D2のいずれかを選択する。判定器40は、符号フラグF1〜F3が入力し、セレクタSEL11〜SEL13のそれぞれの選択動作を制御する。

(もっと読む)

制御装置、及び制御方法

【課題】複数のレジスタへのアクセスを高速に行う。

【解決手段】制御装置は、複数のレジスタのアドレスをそれぞれ保持し、前記複数のレジスタのアドレスとは異なる第1のアドレスの指定に応答して前記複数のレジスタのアドレスを出力するアドレス設定部と、前記アドレス設定部から前記複数のレジスタのアドレスが入力され、当該複数のレジスタを選択する選択信号を同じタイミングで出力する第1のデコーダと、前記第1のアドレスに対する書込みデータを前記選択信号により選択される複数のレジスタに並行して書き込み、また、前記選択信号により選択される複数のレジスタから並行して読み出したデータを前記第1のアドレスからの読出しデータとして出力するデータ入出力部とを有する。複数のレジスタへ同時にアクセスでき、レジスタアクセスが高速化される。

(もっと読む)

情報処理装置

【課題】従来の情報処理装置は、同時発行命令数により並列演算数に制限があった。

【解決手段】本発明の情報処理装置は、命令キャッシュと、データキャッシュと、並列動作可能な複数の演算器を備える第1、第2の演算器群22a、22bと、第1の演算器群22aに対する1以上の演算命令を生成する第1の演算制御回路10と、固定命令レジスタ31の命令コードに基づき第2の演算器群22bに対する1以上の演算命令を生成する第2の演算制御回路30と、を有し、第1の演算器群22aは、第1の演算制御回路10が第1の特定命令コードに基づき生成した演算命令に応じて固定命令レジスタ31に命令コードを設定し、第1の演算制御回路10が第2の特定命令コードに基づき生成した演算命令に応じて第2の演算器群22bに処理データを与え、第2の演算器群22bは、第2の演算制御回路30が生成した演算命令に基づく演算を繰り返し実行する。

(もっと読む)

選択可能な副精度に対して、低減された電力要求を有する浮動小数点プロセッサ

【課題】所定の精度を有する浮動小数点プロセッサにより、必要以上の電力を消費せずに浮動小数点演算を実行する。

【解決手段】1つ以上の浮動小数点数に関して、浮動小数点演算に対する副精度が選択される。副精度の選択は、1つ以上の浮動小数点数のそれぞれに対して、1つ以上の過剰ビットをもたらす。さもなければ1つ以上の過剰ビットを記憶または処理するために使用される、浮動小数点プロセッサ中の1つ以上のコンポーネントから、電力を取り除くことができ、浮動小数点演算は、1つ以上のコンポーネントから電力を取り除いた状態で実行される。

(もっと読む)

再構成デバイス、処理配置方法及びプログラム

【課題】再構成デバイスの回路構成変更において、機構追加による回路規模を増やすことなく、処理内容に対する依存を回避しつつ回路構成変更期間を短縮する。

【解決手段】外部メモリ101は、内部に回路構成情報106を保持している。回路構成情報106は再構成デバイス105を構成する要素を動作させる設定群である。コンフィギュレーションコントローラ102は上記メモリ101から結線104を通じ回路構成情報106を取得する。取得した回路構成情報106は結線103を通じて再構成デバイス105へ送られる。

(もっと読む)

データ処理装置およびそのデータ処理方法

【課題】可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能なデータ処理装置を提供すること。

【解決手段】データ処理装置100は、SIMD方式の複数のPE1(5)と、複数のPE1(5)のそれぞれに対応して設けられる複数のSRAMs2と、複数のPE2(7)とを含む。複数のPE1(5)のそれぞれは、対応する1つのSRAMs2に格納されるデータに対して演算を行なう。また、複数のPE2(7)のそれぞれは、対応する複数個のSRAMs2に格納されるデータに対して演算を行なう。したがって、複数のSRAMs2を共有することができ、可変長データに対する演算処理と、固定長データに対する演算処理とを効率的に行なうことが可能となる。

(もっと読む)

ルートi(√i)演算の保持を特徴とする基数8固定小数点FFT論理回路

【課題】 高速フーリエ変換(FFT)演算の丸め誤差を軽減させること。

【解決手段】 バタフライ演算(8p)に含まれる複素平面上の回転因子のうちで、無理数(√、平方根)として現れるデータを意図的に計算することなく、多段にパイプライン化されているFFTの複数の段のうちの1つの段に設けられているメモリに保持(preserve)しておき、後段において再度現れたきたら、2つの回転因子を掛け合わせる演算を行う。このことによって、基数8 (radix-8)のバタフライ演算8p中の丸め誤差を無くすることができる。基数2 (radix-s)または基数4 (radix-4)のバタフライ演算によって、さらなる段を被せるように応用することもできる。

(もっと読む)

浮動小数点演算回路、浮動小数点演算回路を備えたコンピュータ及びその演算制御方法と演算制御プログラム

【課題】拡張精度演算回路と単・倍精度演算回路とにより単精度同士/倍精度同士の並列演算を実現し、演算処理を高速化して演算実行時間を短縮できること。

【解決手段】第1ビット幅の数値及び前記第1ビット幅より短い第2ビット幅の数値に対してそれぞれが浮動小数点演算を行なう複数の演算回路を有する浮動小数点演算回路であって、演算命令に基づいて、第1ビット幅の演算を行なう第1演算回路が休止することを判定する休止判定部と、休止判定部が前記第1演算回路が休止すると判定した場合に、第1演算回路を第2ビット幅の数値の演算を行なうよう制御し、第2ビット幅の数値の演算を、第1演算回路と第2ビット幅の数値を演算する第2演算回路とにより並列に実行する演算制御部と、を備えることを特徴とする。

(もっと読む)

1 - 10 / 215

[ Back to top ]