国際特許分類[G06F9/32]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | プログラム制御のための装置,例.制御装置 (15,360) | プログラム記憶方式を用いるもの,すなわちプログラムを受取りそして保持するために処理装置の内部記憶装置を用いるもの (15,354) | 機械語命令を実行するための装置,例.命令デコーダ (1,710) | 次位命令のアドレス指定,例.命令カウンタ値の増加,ジャンプ (110)

国際特許分類[G06F9/32]に分類される特許

1 - 10 / 110

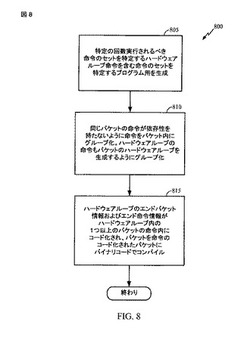

ハードウェアエンドループ情報の命令へのコード化

【課題】パケットのセットのハードウェアループに関する情報をコード化するための方法と装置を提供する。

【解決手段】パケットの各々は複数命令を含む。ハードウェアループに関する情報はパケットのセットの少なくとも1つの命令の1つ以上のビットにコード化される。前記情報は、パケットがループのエンドパケットあるか否かを示す。2つのハードウェアループに関する情報がコード化される。すなわち第1のループに関する情報は各パケットの第1の予め定められた位置における命令内にコード化され、第2のループに関する情報は各パケットの第2の予め定められた位置における命令内にコード化される。エンド命令情報は、コード化されたループ情報のために予約された同じビット位置にコード化されたループ情報を有しない命令内にコード化される。このエンド命令情報は命令がパケットの最後の命令であるかどうか、およびパケットの長さを示す。

(もっと読む)

情報処理装置、アドレス管理方法

【課題】プログラム変更時の再検査をさらに低減できる情報処理装置を提供すること。

【解決手段】変更前のプログラムと変更後のプログラムを記憶するプログラム記憶手段103と、変更前後のプログラムの変更部を抽出する変更部抽出手段141と、変更部の命令の先頭からの仮想アドレスを決定すると共に、変更前のプログラムのアドレスを固定したまま、変更前のプログラム及び前記変更部を記憶手段に配置した際の該変更部の物理アドレスを決定し、物理アドレスと仮想アドレスとを対応づけた中間テーブルを作成するアドレス決定手段142と、変更後のプログラムの各命令と、変更後のプログラムの各命令を先頭からアドレス毎に比較し、異なる命令が記述されている場合は、中間テーブルの物理アドレスと仮想アドレスとを取り出して登録したアドレス変換テーブルを作成するアドレス変換テーブル作成手段143と、を有する情報処理装置100を提供する。

(もっと読む)

プロセッサ

【課題】命令のフェッチに際して、命令を格納したメモリへの無駄なアクセスを回避すると共に、CPUの性能低下を防ぐ。

【解決手段】フェッチ部150は、第1のパルス信号CLK1が第2のエッジになったときに、演算部120が次に実行する命令の全ての内容をメモリ190からフェッチするために必要なフェッチ回数Nを算出すると共に、N回のフェッチを実行する。演算部120は、第1のパルス信号CLK1の上記第2のエッジの次の第2のエッジまでに命令を実行すると共に、前記次の第2のエッジのときに、次の命令の先頭アドレスをPC140とフェッチ部150に出力する。フェッチ部150は、上記N回のフェッチのうちの1回目のときに、フェッチアドレスとして演算部120が出力した先頭アドレスを用い、K回目(K:2以上の整数)のときに、Kと、PC140の値と、データバス幅とからフェッチアドレスを算出する。

(もっと読む)

可変長の命令セット実行モードを有するプロセッサにおけるBHTの有効な利用

【課題】可変長の命令セット実行モードを有するプロセッサにおいて、電力の節約が可能な分岐履歴テーブルの構成を提供する。

【解決手段】少なくとも第1の最小の命令長を有する第1の命令セット実行モード、及び、より小さな、第2の最小の命令長を有する第2の命令セット実行モードで命令を実行するプロセッサにおいて、分岐履歴テーブル(BHT)46のあらゆるカウンタにアクセスし、現在の命令セット実行モードに基づいて多重化されたインデックスアドレスビットの数を削減する、行インデックスアドレス及びカウンタインデックスアドレスが形成される。一実施形態において、BHTの行内のカウンタは、当該BHTの半分が一つの命令セット実行モードにおける各アクセスについて電源を落とすことができるような方法でインデックスを付けられ、配置される。

(もっと読む)

同期並列スレッドプロセッサにおける間接的な関数呼び出し命令

【課題】関数ポインタを使用して間接的な関数呼び出しを行えるようにするSIMTアーキテクチャーを提供する。

【解決手段】間接的な分岐命令は、単一命令複数スレッド(SIMT)プロセッサアーキテクチャーに対する間接的な関数呼び出し能力を与えるためにアドレスレジスタを引数としてみなす。間接的な分岐命令は、間接的な関数呼び出し、バーチャルな関数呼び出し、及びスイッチステートメントを実施して、テスト及び分岐の逐次チェーンの使用に比して処理性能を改善するのに使用される。

(もっと読む)

演算装置およびプログラム

【課題】複数の分岐条件を含む分岐構造の処理に要する命令数およびサイクル数を低減可能な演算装置およびプログラムを提供する。

【解決手段】実施形態の演算装置は、演算部と第1記憶部と読み出し部と出力部とを備える。演算部は、少なくとも2以上の分岐条件の各々について、当該分岐条件の判定を行い、当該分岐条件が成立した場合に行われる演算を実行する。第1記憶部は、判定の判定結果と、演算が有効であるか否かを示す演算情報とを対応付けて記憶する。読み出し部は、演算部の判定により得られた判定結果に対応する演算情報を第1記憶部から読み出す。出力部は、読み出し処理で読み出された演算情報によって有効であることが示された演算の結果を示す演算結果を出力する。

(もっと読む)

情報処理装置

【課題】 パイプライン処理の停止を低減するとともに、ループ処理が実施されている期間のアクセス効率を向上する。

【解決手段】 情報処理装置は、命令を取得するフェッチ部と、命令を解読するデコード部と、フェッチ部から出力される命令を順次記憶する書き込み動作と、ループ処理の範囲に対応する命令を繰り返し出力する読み出し動作とを切り替えて実施する命令バッファ部と、書き込み動作が実施されているとき、フェッチ部から出力される命令をデコード部に出力し、読み出し動作が実施されているとき、命令バッファ部から出力される命令をデコード部に出力する選択部とを有している。

(もっと読む)

中央演算処理装置及びマイクロコンピュータ

【課題】処理速度の高速化を図った中央演算処理装置及びマイクロコンピュータを提供する。

【解決手段】当該CPU3の制御回路31によって直接読み取ることができる内部メモリにプログラムデータを格納したプログラムデータエリア38を設けている。プログラムデータは、命令情報及びこの命令情報を実行するために必要なオペランド(補足情報)を含んだ複数の命令から構成されている。このプログラムデータエリア38は、アドレスが割り振られた24ビットのデータ領域が複数設けられ、1つのデータ領域に1つの命令が格納され、1つのデータ領域の先頭に命令情報が格納されている。

(もっと読む)

可変長命令のプリデコーディング

【課題】プロセッサにおける可変長命令をプリデコーディングする方法を提供する。

【解決手段】可変命令長プロセッサにおけるプリデコーダは、命令と共に命令キャッシュに格納されたプリデコードビットで命令の属性を表示する。1の長さ命令と関連付けられたプリデコードビットPD0、PD1の全符号化が定義されるとき、その長さの命令の属性は、異なる長さの命令をエミュレートするために命令を変更し、異なる長さの命令と関連付けられたプリデコードビットの属性を符号化することによって表示される。そのように表示される属性の1つの例は未定義命令である。

(もっと読む)

命令実行回路

【課題】命令実行回路の消費電力を低減させる。

【解決手段】複数の命令により構成されるプログラムの一部分を記憶する第1記憶素子、及び前記プログラムの他の部分を記憶し前記第1記憶素子よりも消費電力が少ない第2記憶素子を有する記憶回路と、命令のアドレスを前記記憶回路に対して出力し前記アドレスに記憶されている命令を取得して実行するプロセッサと、前記アドレスに記憶されている命令を出力させるためのイネーブル信号を、前記命令を記憶している前記第1記憶素子及び前記第2記憶素子のうちのいずれか一つに対して出力するアドレスデコーダと、を備え、前記プログラムの前記他の部分は前記プロセッサに特定の命令を繰り返し実行させるループ処理が記述された部分であり、前記プログラムの前記一部分は前記ループ処理以外の処理が記述された部分であることを特徴とする命令実行回路。

(もっと読む)

1 - 10 / 110

[ Back to top ]