国際特許分類[G06G7/12]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | アナログ計算機 (66) | 計算動作が電気的または磁気的量を変化させることにより行われる装置 (60) | 計算動作を行なう装置,例.そのために特に適用された増幅器 (42)

国際特許分類[G06G7/12]の下位に属する分類

最適化のためのもの,例.最小自乗法による適合法,線形計画法,クリティカルパス解析法,勾配法

加算または減算用のもの (4)

乗算または除算用のもの (9)

積分または微分のためのもの (6)

積の積分をするためのもの,例.フーリエ積分,ラプラス積分,相関積分;直交関数を用いて関数の解析または合成をするためのもの

べき,べき根,多項式,2乗平均値,標準偏差の値を求めるためのもの (4)

三角関数の値を求めるためのもの;座標変換のためのもの;ベクトル量を含む計算のためのもの (1)

対数または指数関数の値を求めるためのもの,例.双曲線関数用 (2)

不連続関数のためのもの,例.バックラッシュ,不感帯,飽和,絶対値または尖頭値のためのもの (1)

任意関数発生器 (5)

内挿または外挿のためのもの

方程式を解くためのもの (1)

国際特許分類[G06G7/12]に分類される特許

1 - 9 / 9

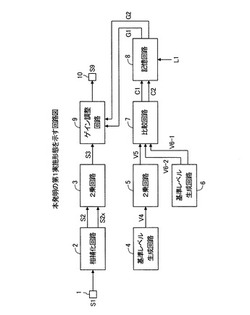

2乗回路

【課題】温度変化によるゲイン変化を補正することができる2乗回路を提供する。

【解決手段】2乗回路3に対して、基準レベルV4を生成する基準レベル生成回路4と、基準レベルV4を入力する2乗回路5と、基準レベルV6−1、V6−2を生成する基準レベル生成回路6と、2乗回路5の出力レベルV5と基準レベルV6−1、V6−2とを比較する比較回路7と、比較回路7が出力する比較結果信号C1、C2を記憶する記憶回路8と、記憶回路8が出力するゲイン切換信号G1、G2を入力して2乗回路3のゲイン調整を行うゲイン調整回路9とで温度補償回路を構成し、温度変化による2乗回路3のゲイン変化を補正し、出力信号S9のレベル変化を補正する。

(もっと読む)

掛算回路

【課題】デジタル処理や対数処理を必要とすることなく、簡易で高速な掛算を行う掛算回路を提供する。

【解決手段】第1定電流源21が、第1コンデンサc1を第1定電流i1で充電する。コンパレータcp1が、第1コンデンサc1の両端電圧Vc1と第1電圧V1とを比較する。第2定電流源31が第2電圧V2に応じた大きさの第2定電流i2を供給して、第2コンデンサc2を充電する。制御回路5が、第1充電スイッチQ10及び第2充電スイッチQ22を制御して、第1コンデンサc1及び第2コンデンサc2の充電を同時に開始させた後に第1コンデンサc1の両端電圧Vc1が第1電圧V1よりも大きくなった時点で第1コンデンサc1及び第2コンデンサc2の充電を終了させる。結果保持回路6が、第1コンデンサc1及び第2コンデンサc2の充電が終了した時点の第2コンデンサc2の両端電圧Vc2を第1電圧V1と第2電圧V2との掛算値として出力する。

(もっと読む)

反比例回路

【課題】接続される外部回路による影響が低減され、より精度の高い反比例回路を実現する。

【解決手段】反比例の演算に寄与するトランジスタQ1及びQ2の他に電流の出力に寄与するトランジスタQ3を設ける。これにより、トランジスタQ1及びQ2のコレクタ−エミッタ間電圧は外部回路の状態に関わらず一定の電圧値になる。したがって、各々のトランジスタQ1及びQ2に流れる電流の反比例関係に対する誤差要因を低減することが可能となる。

(もっと読む)

関数演算器

【課題】PWM/PPM方式において、入力値差の関数F(|x1-x2|)演算を行うことが可能な関数演算器の提供。

【解決手段】入力値x1,x2でパルス位相変調された入力信号PPW1, PPW2が入力されると、各信号に同期して、関数f(t)(f(t)はF(x)の変数xを時間tに変数置換した関数)に比例する関数信号spk1,spk2を生成する関数発生器2a,2bと、関数信号spk1,spk2のうち低い方に比例して変化する最小値信号n1を生成する最小値検出器3と、最小値信号n1の出力のピークを保持し結果信号Vspkとして出力するピークホールド回路4を備えた。

(もっと読む)

非線形演算回路

【課題】MOS回路による非線形演算回路で利得可変とし、温度依存性やプロセスによる利得特性のばらつきを低減する。また、種々の非線形演算に適用可能とする。

【解決手段】 非線形演算回路1は、2つの乗算器10,20と演算増幅器30とを備える。演算増幅器30の正相入力端子に2つの乗算器の何れか一方の乗算器の出力端子を接続し、逆相入力端子に2つの乗算器の他方の乗算器の出力端子を接続する。さらに、演算増幅器30の出力端子に2つの乗算器の何れかの乗算器が備える一方の入力端子を接続し、これによって、演算増幅器の演算出力をその乗算器に帰還させる。

(もっと読む)

絶対値比較回路および絶対値比較プログラム

【課題】 比較回路を備えずに絶対値の比較が可能な絶対値比較回路を提供する。

【解決手段】 本発明の絶対値比較回路は、半波整流回路1a〜1eおよび加算器3a〜3dで構成される。入力データXは2つに分岐され、一方は半波整流回路1aを介して加算器3aに入力され、もう一方は符号を反転させた後に半波整流回路1bを介して加算器3aに入力される。同様に、入力データYも2つに分岐され、一方は半波整流回路1cを介して加算器3bに入力され、もう一方は符号を反転させた後に半波整流回路1dを介して加算器3bに入力される。加算器3aの出力と加算器3bの出力とが加算器3cで加算され、半波整流回路1eに入力される。一方、加算器3aの出力と半波整流回路1eの出力とは加算器3dで加算され、結果が絶対値比較回路の出力となる。

(もっと読む)

中間値回路および耐故障性回路

【課題】 精度の高い中間値回路を提供する。

【解決手段】 中間値回路1は、第1の入力端子10a、第2の入力端子10bおよび第3の入力端子10c、処理回路部20、ならびに出力端子30を備えている。処理回路部20は、入力端子10a,10b,10cから出力端子30に至る経路中に設けられた演算増幅器22a,22b,22c,24を含んで構成されており、入力端子10a,10b,10cからそれぞれ入力された入力電圧Vx,Vy,Vzを処理し、これらの入力電圧の中で中間値に相当する電圧を生成する。

(もっと読む)

関数デバイス

ファジィ機能の実現は、AD変換器、DA変換器、マイクロプロセッサのソフトウエアの協同でなされ、ソフトハード両面の開発を要する。ソフトウエアを介するため、動作速度も制限される。所望のファジィ機能をしきい値付きの増幅器で実現する。左側の6個のトランジスタM11−16は、インバータとして利用される総和増幅器の本体に対応し、右側の10個のトランジスタM1−10は、総和増幅器の本体に相当する(図8)。 (もっと読む)

DNAに基づいた数値表現体系及び算術

【課題】本発明の主要な目的は、DNAに基づいた数値表現体系を開発することと、DNAに基づいた算術を実行することとであり、DNAに基づいた数値表現を符号化するソフトウェアを実行することであり、DNAで符号化された数値表現を用いて算術演算を実行することである。

【解決手段】DNAや他の分子コンピューティングの素子や処理装置の分野において広く適用できる、DNAに基づいた数値表現体系と、該数値表現体系のための、加算や減算のような基本的な算術演算を開発した。その数値表現の手法は、全てのDNA塩基への所定の値の割当と(A=0,T=1,C=2,G=3)、DNA塩基の補数の所定の割当と(Aの補数=G,Tの補数=C,逆もまた同一)、DNA塩基による整数及び実数の表現と、DNAに基づいた数値表現体系での基本的な算術割当の実行とを含む。

(もっと読む)

1 - 9 / 9

[ Back to top ]