国際特許分類[G06T1/20]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | プロセッサアーキテクチャ;プロセッサ構成,例.パイプライン (990)

国際特許分類[G06T1/20]の下位に属する分類

ニューラルネットワーク (39)

国際特許分類[G06T1/20]に分類される特許

101 - 110 / 951

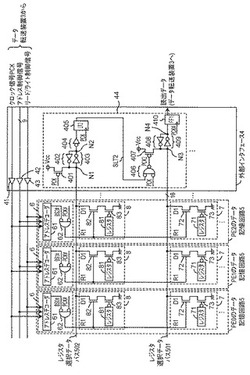

画像処理回路及びそれを備えた画像処理装置

【課題】画像処理回路の消費電力を削減する。

【解決手段】プロセッサエレメントPEnの制御データレジスタ81は、プロセッサエレメントPEnのデータレジスタ71に格納されたデータがプロセッサエレメントPEnのデータレジスタ71の次に読み出されるプロセッサエレメントPEn+1のデータレジスタ71に格納されたデータと一致するか否かを示すプリチャージ制御データを格納する。バス制御回路44は、プロセッサエレメントPEn+1のデータレジスタ71からデータを読み出すとき、プロセッサエレメントPEnの制御データレジスタ81のプリチャージ制御データに基づいて、プロセッサエレメントPEn+1のデータレジスタ71に格納されたデータが、プロセッサエレメントPEnのデータレジスタ71に格納されたデータと一致するときは、レジスタ選択データバス501のプリチャージを抑止する。

(もっと読む)

画像処理装置、および、画像処理装置におけるメモリー制御方法

【課題】データを列単位で読み出すモジュールと行単位で読み出すモジュールを有する画像処理装置について、メモリーの設置に基づく回路規模の増大化を防ぐための技術を提供する。

【解決手段】行アクセスする第1のモジュール(行アクセス処理部107)と、列アクセスする第2のモジュール(列アクセス処理部108)と、で共用されるラインメモリー106を備える画像処理装置100における画像読み出し方法である。ラインメモリー106は、複数のバンク(1061A〜H)を有しており、第1のモジュールは、別々のバンクの同アドレス位置に格納されているデータをそれぞれ読み出し、第2のモジュールは、同一バンク内において同行に格納されている複数のデータを読み出す。

(もっと読む)

タイル化されたプリフェッチ及びキャッシングされたデプスバッファ

【課題】3Dグラフィックス処理において、深さタイルのキャッシュを供給するプリフェッチメカニズムをパイプライン化する。

【解決手段】プリフェッチメカニズムは、予測的で、前のパイプライン段階からの三角形幾何情報を用いて前記キャッシュに予め装填することができ、それによってメモリ帯域幅効率の向上を可能にすることができる。電力消費量のさらなる低減及びメモリ帯域幅を考慮してz値圧縮技術をオプションで利用可能である。

(もっと読む)

印刷文書変換装置及びプログラム

【課題】複数のソフトウエア変換手段を実行するプロセッサの処理能力を活用すると共に、当該プロセッサに過剰な処理負荷がかかる可能性を低減する。

【解決手段】RIPモジュール210−1〜210−3は、ソフトウエア処理により、PDLで記述された印刷文書データをビットマップ画像形式のページ画像データに変換する。RIPモジュール210は、特定の画像処理を実行するハードウエアである画像処理装置220に依頼する。並列処理制御部208は、ページを割り当て済みのRIPモジュール210のうち画像処理装置220による画像処理の完了を待っている状態のRIPモジュール210の他のRIPモジュール210の数が、RIPモジュール210を実行するCPUの処理能力に基づいて予め設定された上限を超えないように、各RIPモジュール210に印刷文書データの各ページのRIP処理を割り当てる。

(もっと読む)

印刷文書変換装置及びプログラム

【課題】ソフトウエアでRIPを実行するソフトウエア変換手段がハードウエア画像処理装置に画像処理を依頼することによりソフトウエア変換手段の待ち状態が発生したとしても、ソフトウエア変換手段を実行するプロセッサの処理能力を活用する。

【解決手段】RIPモジュール210は、ページ記述言語で記述された印刷文書データをビットマップ画像形式のページ画像データに変換するためのソフトウエア変換処理を行う。画像処理装置220は、特定の画像処理を実行する。RIPモジュール210−1,210−2は、ソフトウエア変換処理のうち特定の画像処理を画像処理装置220に対して依頼する。RIPモジュール210−1,210−2のうち少なくとも1つが画像処理装置220による画像処理の完了を待つ状態が生じ得る場合、並列処理制御部240は、追加のRIPモジュール210−3を起動する。

(もっと読む)

画像処理装置及び画像処理方法

【課題】入力画像の特性が変化した場合に、ユーザに違和感を与えることなく画像処理の設定を変更する。

【解決手段】本発明の画像処理装置100は、入力画像の特性の変化を取得する特性変化取得部102と、入力画像に対して画像処理を行う画像処理部と、画像処理のゲインを調整するゲイン調整部108と、入力画像の特性の変化に応じて、画像処理部における画像処理の設定を変更するとともに、画像処理の設定を変更するタイミングでゲイン調整部108によりゲインを低下させる制御を行う制御部110と、を備える。

(もっと読む)

画像処理装置及びプログラム

【課題】補助演算処理部で処理されるデータサイズに依らず処理全体の高速化を図ること。

【解決手段】メインメモリを用いて複数の画像処理を実行するCPUと、ローカルメモリを内在しハーフトーン処理を実行するDSPと、を備え、DSPがメインメモリを用いてハーフトーン処理を実行するために要する第1想定処理時間と、DSPがローカルメモリを用いてハーフトーン処理を実行するために要する第2想定処理時間と、を算出し、第1想定処理時間と第2想定処理時間とのうち短い時間でのハーフトーン処理において用いるメモリを、DSPがハーフトーン処理を実行する際に用いるメモリとして設定する画像処理装置。

(もっと読む)

専用機能ハードウェア間の切り替えおよび結果データを生成するソフトウェアルーチンの使用

【課題】一連のプログラム命令に応じて、命令デコーダによって制御される処理回路を含む、データを処理するための装置を提供する。

【解決手段】処理回路から出力データを受信し、専用処理作業を実行するように構成される専用機能ハードウェア12も提供する。命令デコーダは、終了命令およびソフトウェア処理フラグに応じて、現在のソフトウェアルーチンを終了するように処理回路を制御して、出力データを生成し、ソフトウェア処理フラグに従って、専用機能ハードウェアにより出力データの処理をトリガするか、または専用ハードウェア回路で生成されるハードウェア生成結果データの代わりにソフトウェア生成結果データを生成するために、出力データにさらなるソフトウェアルーチンを実行するように処理回路をトリガするかのいずれかを行う。

(もっと読む)

データ圧縮装置、データ伸張装置およびデータ圧縮方法、データ伸張方法

【課題】複数のPEとメモリコントローラ部とラインバッファメモリなどの記憶手段とを利用して簡単構成かつ単純な処理でデータを圧縮伸張することができるデータ圧縮装置、データ伸張装置およびデータ圧縮方法、データ伸張方法を提供する。

【解決手段】GP2が、隣接する左隣の汎用レジスタの値と比較して同じ値の場合は制御コードを0に、異なる値の場合は制御コードを1に設定し、その制御コードに基づいて汎用レジスタのデータをラインバッファメモリ7にライトし、ライトしたデータを倍率2倍で汎用レジスタに書き戻し、制御コードの0の連続数をカウントしてラインバッファメモリ7にライトし、そのカウント数を倍率2倍で汎用レジスタに書き戻しデータとカウント数とが交互に並ぶように合成して圧縮データを生成する。

(もっと読む)

情報処理装置、情報処理方法

【課題】GPUにて連続的に実行される複数のエフェクト処理の変更に伴うGPUによる操作時間を短縮して全体的な効率の向上を図る。

【解決手段】ユーザより、画像データに対してかけるエフェクトの一部をキャンセルしたり、複数のエフェクトの実行順序を変更する指示が入力されたとき、CPUは、CPUメモリに保存されたエフェクト設定情報を変更し、変更されたエフェクト設定情報をもとに、初期化処理でGPUメモリに確保された入出力バッファをそのまま利用しつつ、それらの入出力バッファの接続情報のみを更新する。CPUは、入出力バッファの接続情報をもとに、GPUにて順次実行されるエフェクト毎の入力バッファおよび出力バッファのアドレス情報をGPUに通知する。

(もっと読む)

101 - 110 / 951

[ Back to top ]