国際特許分類[G06T1/20]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | プロセッサアーキテクチャ;プロセッサ構成,例.パイプライン (990)

国際特許分類[G06T1/20]の下位に属する分類

ニューラルネットワーク (39)

国際特許分類[G06T1/20]に分類される特許

51 - 60 / 951

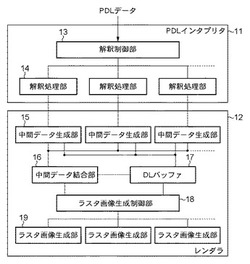

画像処理装置及び画像処理方法

【課題】PDLに記述されたページ内の画像形成命令を並列解釈し、高速にラスタ画像データ生成を行う。

【解決手段】PDLインタプリタが、PDLのページ内の画像形成命令を分割して、解釈処理部に解釈処理を並列実行させる。解釈処理部は相対的な描画状態属性値を使い画像形成命令をオブジェクト描画命令に変換してレンダラに渡す。レンダラでは、複数の中間データ生成部により、中間データ生成を並列的に行ったのち、中間データの結合処理を行う。中間データの結合処理が終了した時点で、ラスタ画像生成処理を並列実行する。

(もっと読む)

フィルタリング処理回路とそれを有するマッチング回路

【課題】簡単な回路構成で高速にフィルタリング処理を行う。

【解決手段】異なる視点での2つの画像に対する複数のずれ量に対応する差分絶対値和のうち,最小差分絶対値和を抽出するフィルタリング処理回路であって,入力回路に入力される複数のずれ量にそれぞれ対応する複数の差分絶対値和が当該入力時点までで最小の差分絶対値和の場合に最小の差分絶対値和として保持する最小差分絶対値和保持回路と,次に小さい第2最小差分絶対値和を検出して保持する第2最小差分絶対値和検出回路と,入力時点までで最小の差分絶対値和でない場合には,当該入力差分絶対値和を第2最小差分絶対値和検出回路に入力し,最小の差分絶対値和である場合には,最小差分絶対値和保持回路で最小差分絶対値が更新されることに伴って最小差分絶対値和保持回路から出力される元の最小差分絶対値和を,第2最小差分絶対値和検出回路に入力するセレクタ回路とを有する。

(もっと読む)

割当方法、割当装置、および割当プログラム

【課題】命令要求元が要求する処理性能に対応した割当を行う。

【解決手段】割当装置101は、VM1から通知された描画命令をグラフィックカード110#1に送信する。さらに、割当装置101は、グラフィックカード110#2、グラフィックカード110#3に対して、複製された描画命令を送信する。送信後、割当装置101は、グラフィックカード110#1〜グラフィックカード110#3に対して、描画命令を実行した場合の使用率を計測する。計測後、割当装置101は、グラフィックカード110#1のGPU使用率となる40[%]より適切な使用率となったグラフィックカード110#3を特定し、描画命令の送信先をグラフィックカード110#1からグラフィックカード110#3に切り替える。

(もっと読む)

画像処理プログラム、情報処理端末装置および情報処理端末装置の制御方法

【課題】アプリケーション連携機能の実行時における操作性を向上できる画像処理プログラム等の提供。

【解決手段】CPUは、特定処理実行部にスキャン処理を実行させた場合に、複数の実行部のうちから選択された選択実行部と特定処理実行部との間で画像データを共有する旨の入力を受け付けることに応じて、選択実行部が印刷/スキャンアプリケーションに基づいて機能する実行部であるか否かを判断する。CPUは、選択実行部が印刷/スキャンアプリケーションに基づいて機能する実行部であると判断される場合には、画像データに対して自身の印刷/スキャンアプリケーションに基づく処理を実行する。CPUは、選択実行部が印刷/スキャンアプリケーションに基づいて機能する実行部でないと判断される場合には、CPUを選択実行部として機能させるアプリケーションプログラムを起動させる。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】データの転送効率を維持した状態で、データ転送に係る消費電力を低減することができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】入力データを順次データバスに配置した第1の転送データを生成するデータ生成部と、データバスのビット幅を、予め定められたビット数の複数の単位ビットに分割し、第1の転送データ内に配置されたデータの配置を、単位ビット毎に並べ替えた変更データを生成し、該生成した変更データと、並べ替えられたデータの配置を表す並べ替え情報とを、転送データとして出力する第1のデータ配置変更部と、を具備し、順次入力された複数の入力データを、予め定められたビット数のデータバスと同じビット数の転送データに変換して順次転送する際に、1つの転送データを1つの転送単位とし、予め定められた数の転送単位を1つの変換単位として、入力データを変換単位毎に配置するデータ変換部、を備える。

(もっと読む)

画像処理システム

【課題】並列動作する複数の画像処理装置が共通要素のためのキャッシュメモリ等の記憶装置をそれぞれ個別に持つ構成よりも、キャッシュメモリ等の記憶装置の利用効率を向上させる。

【解決手段】印刷システム100では、PDLの印刷データをラスター画像データに変換する処理のための装置を、前段のフロントエンド装置110と後段のバックエンド装置120との2つの段階の装置に分けられている。そして、前段は複数のフロントエンド装置110による並列構成とするとともに、後段は1つのバックエンド装置120内に搭載された複数の処理回路124による並列構成としている。複数の処理回路124は、同じバックエンド装置120内にあるキャッシュメモリ123を共用する。

(もっと読む)

データ処理装置およびデータ処理方法

【課題】データの転送効率を維持した状態で、データ転送に係る消費電力を低減することができるデータ処理装置およびデータ処理方法を提供する。

【解決手段】データバスのバス幅を第1のビット範囲と第2のビット範囲とに分割し、同じ種類の情報を持つ入力データの同一ビットがデータバスの同一ビットで連続して転送されるように、第1のビット範囲用の第1のデータを生成する第1のデータ生成部と、第2のビット範囲用の第2のデータを生成する第2のデータ生成部と、第1のデータと第2のデータとを結合した変換データを生成するデータ結合部と、を具備し、順次入力された複数の入力データを、予め定められたビット数のデータバスと同じビット数の変換データに変換して順次転送する際に、1つの変換データを1つの転送単位とし、予め定められた数の転送単位を1つの変換単位として、入力データを変換単位毎に配置するデータ変換部、を備える。

(もっと読む)

キャッシュメモリ装置及び制御方法

【課題】キャッシュメモリに記憶されたピクセルデータの利用率向上を可能とするキャッシュメモリ装置を提供する。

【解決手段】本発明は、表示する画像データの幅がWピクセルであり、2次元方形領域の幅がaピクセル及び縦がbピクセルの場合、横方向のエントリ数がW/aである数pであり、縦方向のエントリ数が[a×2(1/2)/b]の整数値に2を加えた数qであるエントリマトリクスのキャッシュメモリと、表示画面の座標系の表示アドレスを、表示メモリの画像データの座標系へ角度θで座標変換が行われた、2次元方形領域のメモリアドレスから、エントリアドレスを生成するエントリアドレス生成部と、表示メモリからメモリアドレスを用いた角度θのラスタースキャンで分割画像データを読み出し、キャッシュメモリに書き込む書込制御部と、表示される画像データの全走査線に対応するピクセルデータを順次読み出す読出制御部とを有する。

(もっと読む)

画像データ処理システム

【課題】複数の論理ページを単一の物理ページ上に書き込む場合でも、並列化による速度向上効果を得ることができるようにする。

【解決手段】インタプリタ112−1と112−2は、それぞれ論理ページのPDLを処理し、中間データを生成する。論理区域データ生成部114−1,114−2は、各論理ページの中間データを2つの論理区域データに分ける。論理区域データ分配装置115は、論理区域データ生成部114−1,114−2からの論理区域データを、物理ページの物理区域ごとに編成し、マーキング処理部122A及び122Bに対し、それぞれ対応する物理区域に含まれる複数の論理区域データを分配する。マーキング処理部122A及び122Bは、それら論理区域データを物理区域Aバッファ124A及び物理区域Bバッファ124Bに描画する。セレクタ126はそれらバッファ124A及び124B内の画像データを順に印刷エンジン130に供給する。

(もっと読む)

画像処理装置及び画像処理方法

【課題】複数のコアをもつデバイスをアクセラレータとして用いる画像処理装置において、全体的な処理効率の向上を図る。

【解決手段】複数のコアを内部に持つデバイスであって、それぞれのコアを、1機能で専用させる専用モードで動作させるか、複数の機能で共用させる共用モードで動作させるかを、コンフィグレーションにより設定可能なデバイスをアクセラレータとして用いる画像処理装置において、機能の利用履歴とプロファイル結果に基づいて、各コアの現在の設定モードでの、最適な機能のコアの割り振りを決めるコア割り当て決定手段と、各コアの設定モードを変えることを前提にして、最適な各コアの設定モード及び機能のコアの割り振りを決めるコア割り当て決定手段とを段階的に切り替える。

(もっと読む)

51 - 60 / 951

[ Back to top ]