国際特許分類[G06T1/20]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | プロセッサアーキテクチャ;プロセッサ構成,例.パイプライン (990)

国際特許分類[G06T1/20]の下位に属する分類

ニューラルネットワーク (39)

国際特許分類[G06T1/20]に分類される特許

61 - 70 / 951

情報処理装置、情報処理方法およびプログラム

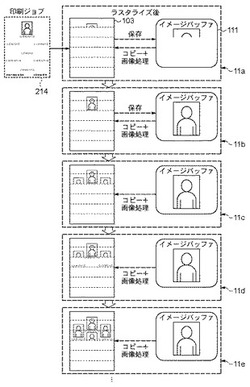

【課題】パターン印刷において処理時間を低減する情報処理装置を提供する。

【解決手段】ユーザに入力させた基準パラメータの値に基づいて、基準パラメータの値を段階的に変化させたパラメータの値を、予め定められた数分生成する。画像データの縮小画像を印刷するための描画命令を含む印刷ジョブを生成し、その描画命令をラスタデータに変換して格納する。格納されたラスタデータを予め定められた数分複製し、格納されたラスタデータに対して基準パラメータに基づき画像調整処理を行う。また、複製されたラスタデータそれぞれに対して、生成されたパラメータそれぞれに基づき画像調整処理を行う。

(もっと読む)

画像処理装置、画像処理方法及びプログラム

【課題】レンダリング処理を高速化することを目的とする。

【解決手段】PDLデータを順次、受け取り、PDLデータに含まれる図形を後段の処理に渡す受け取り手段と、受け取り手段より渡された図形ごとにエッジ情報を抽出する処理の単位であるエッジ抽出処理を割り当てる割り当て手段と、図形ごとに抽出されたエッジ情報を合成する合成手段と、合成手段で合成されたデータをタイル状のフォーマットで中間データとしてスプールするスプール手段と、スプール手段からタイル状の中間データを読み出し、中間データからピクセルを生成するに際し、タイルごとにそれぞれ処理を行う生成手段と、を有することによって課題を解決する。

(もっと読む)

画像処理装置、流体吐出装置、画像処理方法及びそのプログラム

【課題】データ変換処理の高速化をより図る。

【解決手段】プリンター20は、画像変換部56が、すべて白色の画素ラインの先頭の画素、及び画像データに含まれる画素ラインの有色画素と白色画素との境の画素にNullフラグを対応付けたxRGBデータ70を生成する。次に、ライン取得ユニット61が、xRGBデータ70から画素ラインごとに画素を取得し、この取得した画素値を出力する一方、取得した画素にNullフラグが対応付けられているときには、このフラグ付き画素77に隣接する白色画素の出力を省略する。そして、出力された画素値を、データ変換補正処理により印刷データ74の画素値へ変換する。このように、すべて白色の画素ラインに加えて有色画素を含む画素ラインについてもデータ変換補正処理を省略する。

(もっと読む)

画像処理装置、画像処理システム、データバックアップ方法、プログラム、記憶媒体

【課題】ある機器が有する記憶領域を使用できない場合でも、他の機器が、使用できない記憶領域に記憶されたデータを利用可能な連携処理システムを提供する。

【解決手段】機能テーブルを記憶する機能テーブル記憶手段23と、他機の機能テーブルを取得する取得手段17と、電子データの識別情報を、画像処理前の電子データの識別情報、及び、画像処理前の電子データに対し自機又は他の機器が施すことで生じた画像処理の差分情報を対応づけて登録した差分情報管理データを記憶する差分情報管理データ記憶手段27と、電子データを再作成するために必要な再作成機能をバックアップ対象の電子データの差分情報から特定する機能特定手段28と、機能テーブルに再作成機能が登録されているか否かを判定して、該電子データ又は新規電子データと前記差分情報をバックアップする手段29と、を有する。

(もっと読む)

画像処理装置および画像形成装置

【課題】誤差拡散法を用いた2値化処理をより迅速に行なう。

【解決手段】処理ラインの後段のラインの画素を含む処理対象画素の周囲の未処理画素を拡散範囲とする誤差の拡散を伴って、処理ラインの先頭の画素から最後尾の画素に向かって処理対象画素を順にシフトしながら2値化処理するコアを複数備え、複数のコアのうち後段のラインを処理するコアは、前段のラインを処理するコアの処理対象画素に対して少なくとも拡散範囲分だけ処理対象画素を遅らせながら順に2値化処理する。これにより、未処理画素に適切に誤差を反映させながら各ラインを並行処理することができ、誤差拡散法を用いた2値化処理をより迅速に行なうことができる。

(もっと読む)

グラフィックスプロセッサの並列アレイアーキテクチャ

【課題】高い並列度を維持したままで、異なるシェーダーの変動する負荷に適応できるグラフィックスプロセッサを提供する。

【解決手段】グラフィックスプロセッサの並列アレイアーキテクチャは、複数の処理クラスタを含み、各処理クラスタがカバレッジデータから画素データを生成するピクセルシェーダープログラムを実行する少なくとも1個の処理コアを含む、マルチスレッド型コアアレイと、複数の画素のうちの1画素毎にカバレッジデータを生成するラスタライザと、ラスタライザからマルチスレッド型コアアレイ中の処理クラスタのうちの1つにカバレッジデータを配信する画素分配ロジックとを含む。画素分配ロジックは、画像エリアの範囲内の第1画素の位置に少なくとも部分的に依存して第1画素のためのカバレッジデータが配信される処理クラスタのうちの1つを選択する。画素データが処理クラスタから適切なフレームバッファ区画へ直接的に配信される。

(もっと読む)

画像処理装置、電子機器

【課題】 RGB各色についてそれぞれ2面ずつあるメモリーを同時に使用でき、単純な1対1対応の補正出力以外のテーブル機能を持つ画像処理装置を提供する。

【解決手段】 入力画像の補正を画素毎に行う画像処理装置10であって、前記入力画像の注目画素の画素値204を補正して補正値220を生成する画像補正部30と、前記画像補正部30を制御する制御部20と、を含み、前記画像補正部30は、前記補正値の生成に用いる複数のルックアップテーブル40−1〜40−Nを含み、前記制御部20は、前記注目画素の画素値を前記複数のルックアップテーブル40−1〜40−Nの1つに入力させ、前記補正値を前記複数のルックアップテーブル40−1〜40−Nの1つから出力させ、前記複数のルックアップテーブル40−1〜40−Nの任意の1つからの出力を、他の1つの入力とする経路の電気的接続を制御する。

(もっと読む)

タイルベースのグラフィックスシステム及びこのようなシステムの動作方法

【課題】複数のタイルを含むグラフィックスデータ生成のための、タイルベースのグラフィックスシステムと、その動作方法、及びグラフィックス処理回路が提供される。

【解決手段】処理回路は、第1及び第2動作モード間で切換えられる。第1モードで処理回路は、フレーム用のグラフィックスプリミティブを受け取り、ビニング動作を行う。これにより複数のタイルそれぞれについて、グラフィックスプリミティブのうちタイルと交差するものを特定するリストを決定する。第2モードで処理回路は、割り当てられたタイルのタイルリストを受信し、ラスタライゼーション動作を行う。この動作ではタイルリストに応じて、割り当てられたタイルについてグラフィックスデータを生成する。その結果、ビニング動作およびラスタライゼーション動作で同じ処理単位を使用でき、性能およびエネルギー消費を向上でき、グラフィックスシステムのサイズも大幅に低減する。

(もっと読む)

画像処理装置および画像形成装置

【課題】 メモリの容量を小さくし、CPU−ASIC間のバスの転送レートを低くする。

【解決手段】 画像処理装置のハードウェア部分に相当するASICを構成するLSI100では、プレーン処理を行うプレーン処理モジュール104の後段に、色変換処理,階調処理,およびプレーン処理を含む画像処理がなされた画像データであるCMYK毎のプレーンデータを直接入力して圧縮処理を含む符号化処理を実施する圧縮処理モジュール105が配置されることにより、CPU1によってメインメモリ2上に格納された多値の画像データに対する上記画像処理と上記符号化処理とをパイプライン処理できる。

(もっと読む)

イメージプロセッシングパイプラインに対するグローバルアーミング(globalarming)方法

【課題】イメージプロセシングの中断がないイメージプロセシング回路を提供する。

【解決手段】パイプライン構造の複数のイメージプロセッシングの各ユニットは、アップデートされた構成ベクトルを受信し、該構成ベクトルは、時間周期以内にタイミング派生したトリガー信号と同期してのみ適用される。ハードウェアイネーブル信号は、受信された新たな構成ベクトルをイメージプロセッシングユニットに適用するスイッチを制御するためのタイミング派生したトリガリングイベント信号と論理結合される。これは、各イメージプロセッシングユニットの遅延に関係なく、CPUがデータのタイミングとは別途にアップデートされた構成ベクトルを出力する場合にも、チェーン方式のイメージプロセッシングユニットで各イメージプロセッシングユニット(段階)が順次にアップデートされることを保証する。

(もっと読む)

61 - 70 / 951

[ Back to top ]