国際特許分類[G06T1/60]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | イメージデータ処理または発生一般 (58,387) | 汎用イメージデータ処理 (27,485) | メモリ管理 (517)

国際特許分類[G06T1/60]に分類される特許

101 - 110 / 517

画像処理装置および表示用画像メモリアクセス方法

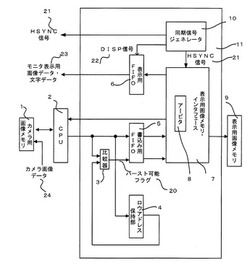

【課題】画像データおよび文字データの表示用画像メモリへの書込みおよび読出しの高速化および効率化を図る。

【解決手段】CPUと表示用画像メモリ・インタフェースの間に書込み用FIFOを設け、該CPUは該書込み用FIFOに画像データ、文字データまたは文字データ読出しコマンドを書込む。表示用画像メモリ・インタフェースは、該書込み用FIFOに蓄積されているデータ等を読んで、表示用画像メモリからの画像データ若しくは文字データのバースト読出し、画像データ若しくは文字データの表示用画像メモリへのバースト書込みまたは編集のための表示用画像メモリからの文字データ読出しを調停する機能を備える。

(もっと読む)

並列処理プロセッサシステム

【課題】 複数のプロセッサを備え、処理するデータを所定の単位に分割し、各データに対して、各プロセッサで並列に処理を行う構成において、命令キャッシュ容量を低減しながら所望のパフォーマンスを得る構成を提供する。

【解決手段】 並列処理プロセッサシステム203は、それぞれDSP301、命令キャッシュ302、画像用ローカルメモリ303を含む複数のプロセッサエレメント(PE1〜PE3)と、共有メモリ304とを備える。共有メモリには、DSPが実行するファームウェアが格納される。並列処理プロセッサシステムは、画像用ローカルメモリに処理対象の画像データを転送し、DSPにより画像処理を施す。キャッシュミスが発生した場合の命令キャッシュの更新は例えば、DSPがアクセスしたアドレスに対応する共有メモリの内容を命令キャッシュにコピーすることによって実現される。

(もっと読む)

画像描画装置

【課題】キャッシュ効率を向上させ描画速度の速い画像描画装置を提供する。

【解決手段】画面の横方向の直線状の絵を書くために、横方向一直線状にテクセルを取得する場合を考える。このとき、16x16ブロックのテクセルに割り振るキャッシュアドレスは、横方向の組のテクセルをグループとし、グループの横側に隣接するグループは、異なるキャッシュアドレス領域が割り当てられたグループとなるようにする。

(もっと読む)

画像処理装置及び画像処理方法

【課題】回路規模の増大を低減、かつ、撮像素子の画素から画素信号を取得する仕様に対して汎用性を持ちつつ、画像データを並び替えることができる画像処理及び画像処理方法を提供すること。

【解決手段】FIFO22は、撮像素子における1行の画素を複数に分割するその分割数の記憶領域を有し、その各記憶領域は撮像素子における少なくとも1行分の画素数を記憶できる。FIFO書き込み部21は、分割した1行の画素の画素データを、分割した数の少なくとも1行の画素数の記憶領域にそれぞれ撮像素子において配置されていた順番で記憶する。SDRAMアドレス制御部25は、分割した数の1行の画素数の記憶領域に記憶された画素の画素データをSDRAMの同じ記憶領域に記憶する。さらに、SDRAM書き込み指定部26は、画素の画素データ以外をSDRAMに書き込むことを禁止する。

(もっと読む)

マルチモードアクセス可能な記憶装置

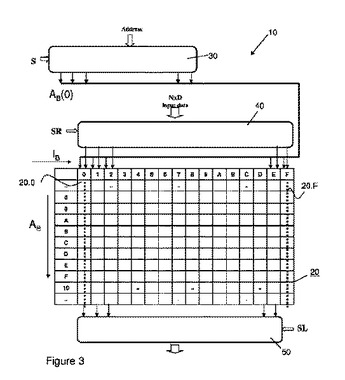

ブロックアクセスモードでのブロックアクセスおよび行アクセスモードでの行アクセスを可能にするマルチモードアクセス可能な記憶装置(10)を開示する。記憶装置は、各々がそれぞれのバンクインデックス(0、…、F)を有する複数のメモリバンク(20.0、…、20.F)を備えるメモリユニット(20)と、前記メモリバンクの各々について入力アドレスおよびシフトパラメータの関数として回転されたバンクアドレスを生成するアドレス発生器(30)と、入力ベクトルを回転させ、回転された入力ベクトルのベクトル要素をメモリユニットのそれぞれのバンクに供給する入力ベクトルデータ回転器(40)と、メモリユニットのそれぞれのバンクから取得されるベクトル要素を含むベクトルを逆回転させ、回転した出力ベクトルを供給する出力ベクトル回転器(50)と、を備える。  (もっと読む)

(もっと読む)

画像処理装置、プログラム

【課題】画像処理装置において、データ順序を変換させる場合に、特別な専用回路を設けることなく、できる限り処理速度の低下を防ぐ。

【解決手段】画像処理部10は、外部メモリー30と、プロセッサー部20とを備える。プロセッサー部20では、第1の処理部210および第2の処理部230が実現される。第1の処理部210は、外部メモリー30から第1の順序で画像データを読み出して処理し、第1の処理済データを内蔵メモリー22に書き込む。第2の処理部230は、内蔵メモリー22から第1の処理済データを読み出して処理し、第2の処理済データを第2の順序で外部メモリー30に書き込む。第1の順序から第2の順序への変更は、第2の処理部230が、第1の処理済データを第2の順序となるように内蔵メモリー22から読み出すことにより実行される。

(もっと読む)

撮像装置および撮像方法

【課題】画像取り込み時間を短縮した撮像装置および撮像方法を提供することを目的とする。

【解決手段】格子状配置の複数の画素を備えた受光部20によって撮像対象物の画像を読み取る撮像装置において、画像取込エリア情報記憶部28に記憶された画像取込エリアの情報に基づいて画像出力対象となる画素を特定する画素選択情報および画像信号を画像記憶部26に記憶させる際の記憶領域を決定する記憶アドレスを生成し、画素選択情報に基づいて画像信号を出力する画素を選択し、出力される画像信号を記憶アドレスにしたがって画像記憶部26に書き込む。これにより必要な画素の画像信号だけを出力して記憶することができる。

(もっと読む)

画像処理回路、および印刷装置

【課題】回路サイズを抑制しつつ参照値を展開する記憶部の記憶容量を増加させることが可能な画像処理回路を提供する。

【解決手段】入力データに対して参照値を参照しつつ所定の処理を施す複数の処理部と、

参照値を記憶する記憶部と、を有し、記憶部は、直列に接続された複数の記憶素子により構成され、所定数の記憶素子毎に各処理部と接続し、同記憶素子に記憶された参照値を接続された各処理部に出力するシフトレジスタと、予め指定されたアドレスを受け付け、シフトレジスタに記憶された前記参照値を更新させるアクセス受信部と、を有する。

(もっと読む)

画像処理装置および画像処理方法

【課題】画像変形処理に要するメモリ量を低減する技術を提供する。

【解決手段】画像処理装置は、変形前画像から画像領域内に変形後画像を生成する処理部を備える。この処理部は、画像領域の一部を構成する対象ブロックを設定する。そして、対象ブロックに対応づけられた変形前画像内の参照ブロックの画像を参照して対象ブロック内に画像を生成する。変形後画像の全体は、対象ブロックを画像領域内で順次移動して、移動後の対象ブロック内の画像を生成することにより生成される。この対象ブロックの画像の生成に先立って、参照ブロックの最大ブロックサイズが算出され、その大きさの画像を格納しうるように、メモリ領域が確保される。対象ブロックの画像は、対象ブロックに対応づけられた参照ブロックの画像をメモリ領域に格納するとともに、メモリ領域に格納された参照ブロックの画像を参照して生成される。

(もっと読む)

メモリ制御装置およびカメラシステム

【課題】カメラシステムにおいてアクセス先アドレスが頻繁に切り替わるデータの処理に関しては、データの先読み機能が有効に発揮されない。最小限のメモリ追加によるシステム構成で、アクセスアドレスを随時切り替える必要のある特定のアクセスパターンにおいても、高速なアクセスを実現し、高いアクセス効率を確保する。

【解決手段】メモリ制御部7が外部メモリ30にアクセスする際のアドレスを取得するアドレス取得手段10と、順次取得されるアドレスの差分情報を一時記憶するアドレスメモリ部11と、差分情報を基に順次アクセスのアドレスが一定周期をもつかを認識する周期認識手段12と、一定周期の連続回数が閾値を超えるか否かを判定する一定周期判定手段14とを備える。メモリ制御部7は、一定周期の連続回数が閾値を超えると判定されたときに先読み機能をアクティブにし、次回アクセスが予想されるアドレスに従って外部メモリに対し先読みのアクセスを行って、その先読みデータをバッファ部9にバッファリングする。

(もっと読む)

101 - 110 / 517

[ Back to top ]